# Lithium Battery Protection Circuit for One Cell Battery Packs

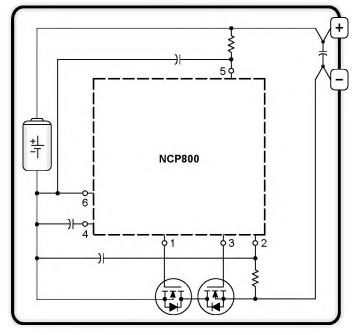

The NCP800 resides in a lithium battery pack where the battery cell continuously powers it. In order to maintain cell operation within specified limits, this protection circuit senses cell voltage and discharge current, and correspondingly controls the state of two. N-channel, MOSFET switches. These switches reside in series with the negative terminal of the cell and the negative terminal of the battery pack. During a fault condition, the NCP800 open circuits the pack by turning off one of these MOSFET switches, which disconnects the current path.

- Internally Trimmed Precision Charge and Discharge Voltage Limits

- Discharge Current Limit Detection

- Automatic Reset from Discharge Current Faults

- Low Current Standby State when Cells are Discharged

- Available in a Low Profile Surface Mount Package

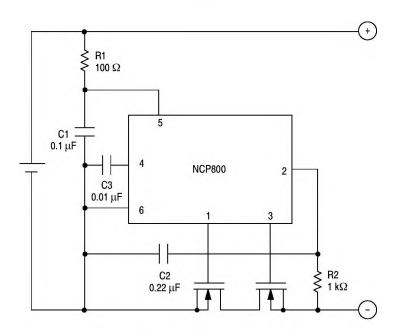

Figure 1. Typical One Cell Smart Battery Pack This device contains 169 transistors.

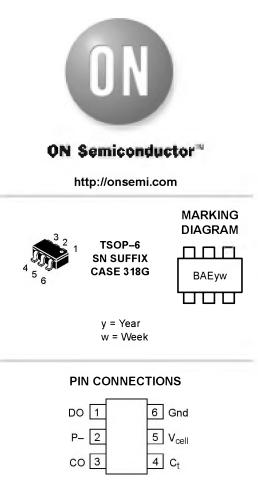

(Top View)

# ORDERING INFORMATION

| Device      | Package | Shipping        |  |

|-------------|---------|-----------------|--|

| NCP800SN1T1 | TSOP-6  | 3000 Units/Rail |  |

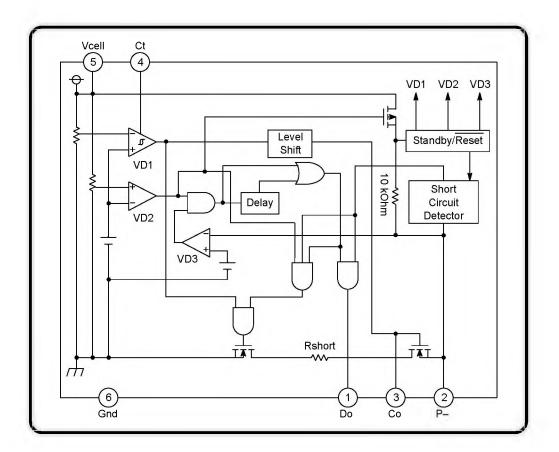

Figure 2. Detailed Block Diagram

## PIN FUNCTION DESCRIPTION

| Pin | Symbol            | Description                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | DO                | This output connects to the gate of the discharge MOSFET allowing it to enable or disable battery pack discharging.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 2   | Ρ_                | This pin monitors cell discharge current. The excess current detector sets when the combined voltage drop of the charge MOSFET and the discharge MOSFET exceeds the discharge current limit threshold voltage, V(DET3). The short circuit detector activates when V(P–) is pulled within typically 0.85 V of the V <sub>cell</sub> voltage. The CO driver is level shifted to the voltage at this pin. |  |  |  |  |  |

| 3   | со                | This output connects to the gate of the charge MOSFET switch Q1 allowing it to enable or disable battery pack charging.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 4   | Ct                | This pin connects to the external capacitor for setting the output delay of the overvoltage detector (VD1).                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 5   | V <sub>cell</sub> | This input connects to the positive terminal of the cell for voltage monitoring and provides operating bias for the integrated circuit.                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 6   | Gnd               | This is the ground pin of the IC.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

## MAXIMUM RATINGS

| Ratings                                                                                                                  | Symbol                             | Value                                       | Unit |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------|------|

| Supply Voltage (Pin 5 to Pin 6)                                                                                          | V <sub>DD</sub>                    | –0.3 to 12                                  | V    |

| Input Voltage<br>Charge Gate Drive Common/Current Limit (Pin 5 to Pin 2)<br>Overvoltage Delay Capacitor (Pin 4 to Pin 6) | V <sub>P-</sub><br>V <sub>Ct</sub> | V(pin5) + 0.3 to V(pin 5) – 8<br>0.3 to 12  | V    |

| Output Voltage<br>CO Pin Voltage (Pin 3 to Pin 2)<br>DO Pin Voltage (Pin 1 to Pin 6)                                     | V <sub>CO</sub><br>V <sub>DO</sub> | V(pin5) + 0.3 to V(pin 5) – 8<br>–0.3 to 12 | V    |

| Thermal Resistance, Junction–to–Air<br>SN Suffix, TSOP–6 Plastic Package, Case 318G                                      | R <sub>θJA</sub>                   | 250                                         | °C/W |

| Operating Junction Temperature                                                                                           | TJ                                 | –40 to 85                                   | °C   |

| Storage Temperature                                                                                                      | T <sub>stg</sub>                   | –55 to 125                                  | °C   |

1. This device contains ESD protection:

Human Body Model 2000 V. Machine Model Method 200 V.

## ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C, unless otherwise noted.)

| Characteristic                                                                                             | Symbol                                  | Min                   | Тур                    | Max                   | Unit     |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------|------------------------|-----------------------|----------|

| VOLTAGE SENSING                                                                                            |                                         |                       |                        |                       |          |

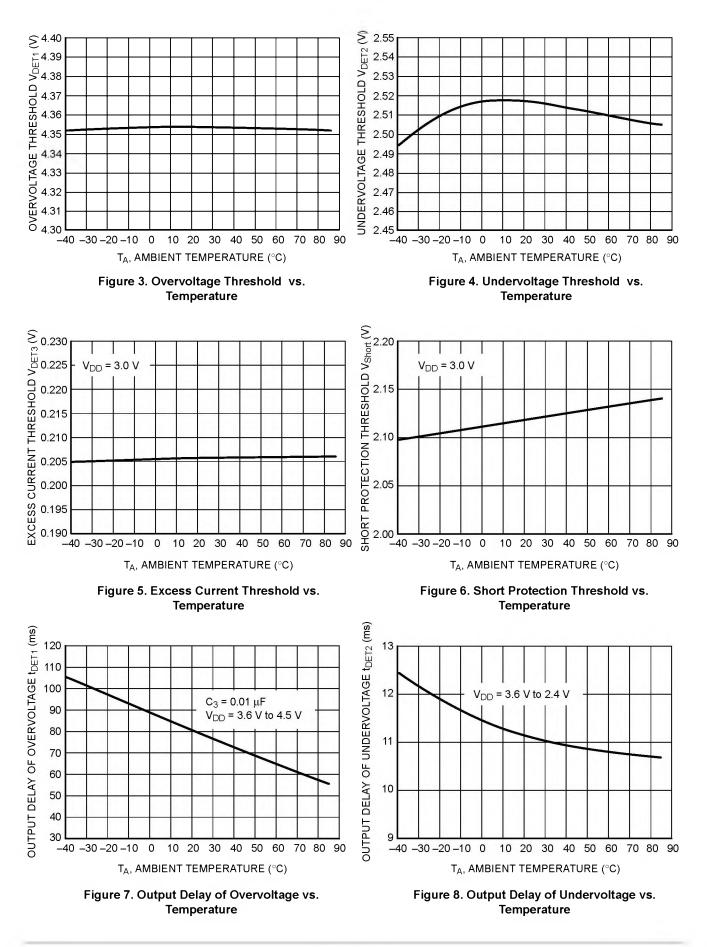

| Overvoltage Threshold, $V_{DD}$ Increasing (Note 2)<br>Overvoltage Hysteresis $V_{DD}$ Decreasing          | V <sub>DET1</sub><br>V <sub>HYS1</sub>  | 4.30<br>150           | 4.35<br>200            | 4.40<br>250           | V<br>mV  |

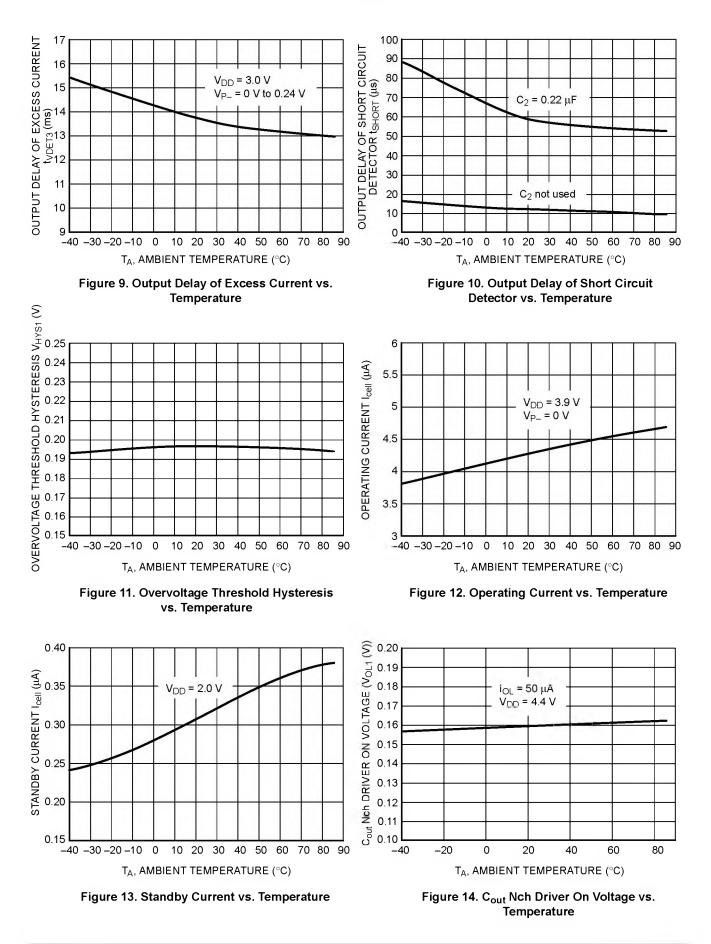

| Overvoltage Delay Time<br>$C_t = 560 \text{ pF}$<br>$C_t = 0.01 \mu\text{F}$                               | t <sub>DET1</sub>                       | 2<br>-                | 4<br>75                | 6<br>-                | ms       |

| Undervoltage Threshold, $V_{DD}$ Decreasing                                                                | V <sub>DET2</sub>                       | 2.437                 | 2.5                    | 2.563                 | V        |

| Undervoltage Delay Time ( $V_{DD}$ = 3.6 V to 2.4 V)                                                       | t <sub>DET2</sub>                       | 7.0                   | 11                     | 13                    | ms       |

| CURRENT SENSING                                                                                            |                                         |                       |                        |                       |          |

| Excess Current Threshold (Detect rising edge of P- pin voltage)<br>(Note 3)                                | V <sub>DET3</sub>                       | 170                   | 200                    | 230                   | mV       |

| Short Protection Voltage ( $V_{DD}$ = 3.0 V)                                                               | V <sub>SHORT</sub>                      | V <sub>DD</sub> – 1.1 | V <sub>DD</sub> – 0.85 | V <sub>DD</sub> - 0.5 | V        |

| Current Limit Delay Time (V <sub>DD</sub> = 3.0 V)                                                         | t <sub>DET3</sub><br>t <sub>SHORT</sub> | 9.0<br>-              | 14<br>10               | 17                    | ms<br>μs |

| Reset Resistance                                                                                           | R <sub>SHORT</sub>                      | 50                    | 100                    | 150                   | kΩ       |

| OUTPUTS                                                                                                    | 1                                       | -                     |                        |                       |          |

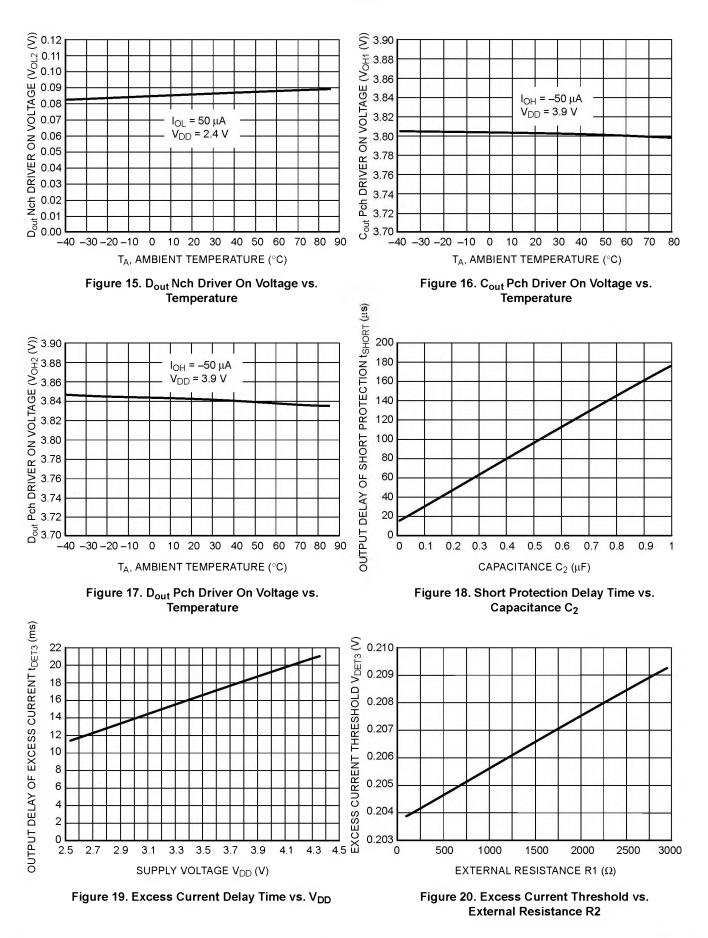

| Charge Gate Drive Output Low (Pin 3 to Pin 2) $(V_{DD} = 4.4 \text{ V}, \text{ lo} = 50 \mu\text{A})$      | V <sub>ol1</sub>                        | -                     | 0.16                   | 0.5                   | V        |

| Charge Gate Drive Output High (Pin 5 to Pin 3) $(V_{DD}$ = 3.9 V, Io = -50 $\mu$ A)                        | V <sub>oh1</sub>                        | 3.4                   | 3.8                    | -                     | V        |

| Discharge Gate Drive Output Low (Pin 1 to Pin 6) $(V_{DD} = 2.4 \text{ V}, \text{ Io} = 50 \mu\text{A})$   | V <sub>ol2</sub>                        | -                     | 0.1                    | 0.5                   | V        |

| Discharge Gate Drive Output High (Pin 5 to Pin 1) $(V_{DD} = 3.9 \text{ V}, \text{ Io} = -50 \mu\text{A})$ | V <sub>oh2</sub>                        | 3.4                   | 3.8                    | -                     | V        |

| TOTAL DEVICE                                                                                               | •                                       | •                     |                        |                       |          |

| Supply Current<br>Operating ( $V_{DD}$ = 3.9 V, VP- = 0 V)<br>Standby ( $V_{DD}$ = 2.0 V)                  | I <sub>cell</sub>                       | 2.0                   | 4.0<br>0.3             | 6.0<br>0.6            | μΑ<br>μΑ |

| Operating Voltage                                                                                          | V <sub>DD</sub>                         | 1.5                   | -                      | 10                    | V        |

|                                                                                                            | 1                                       | 1                     | 1                      |                       |          |

Consult factory about other Overvoltage Threshold Options.

Consult factory about other Excess Current Threshold Options.

#### **OPERATING DESCRIPTION**

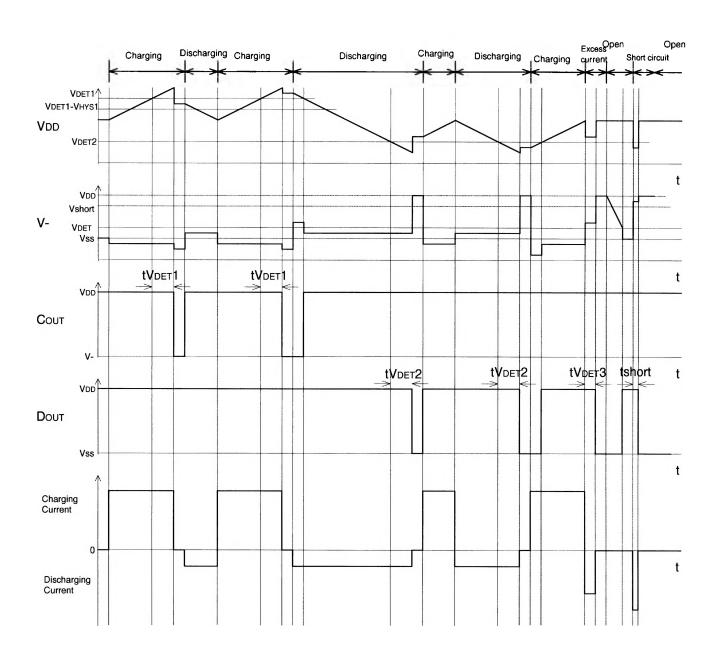

#### VD1 / Over-Charge Detector

VD1 monitors the voltage at the  $V_{CELL}$  pin ( $V_{DD}$ ). When it exceeds the over-charge detector threshold.  $V_{DET1}$ . VD1 senses an over-charging condition, the CO pin goes to a "Low" level, and the external charge control, Nch-MOSFET turns off.

Resetting VD1 allows resumption of the charging process. VD1 resets under two conditions, thus, making the CO pin level "High." The first case occurs when the cell voltage drops below " $V_{DET1}-V_{HYS1}$ ." ( $V_{HYS1}$  is typically 200 mV). In the second case, disconnecting the charger from the battery pack can reset VD1 after  $V_{DD}$  drops between " $V_{DET1}$ " and " $V_{DET1}-V_{HYS1}$ ".

After detecting over-charge, connecting a load to the battery pack allows load current to flow through the parasitic diode of the external charge control FET. The CO level goes "High" when the cell voltage drops below  $V_{DET1}$  due to load current draw through the parasitic diode.

An external capacitor connected between the Gnd pin and Ct pin sets the output delay time for over-charge detection. The external capacitor sets up a delay time from the moment of over-charge detection to the time CO outputs a signal, which enables the charge control FET to turn off. If the voltage fault occurs within the time delay window. CO will not turn off the charge control FET. The output delay time can be calculated as follows:

$$t_{\text{DET1}}[\text{sec}] = (Ct[F] \times (VDD[V] - 0.7)/(0.48 \times 10^{-6}))$$

A level shifter incorporated in a buffer driver for the CO pin drives the "Low" level of CO pin to the P– pin voltage. A CMOS buffer sets the "High" level of CO pin to  $V_{DD}$ .

#### VD2 / Over–Discharge Detector

VD2 monitors the voltage at the  $V_{CELL}$  pin ( $V_{DD}$ ). When it drops below the over-discharge detector threshold,  $V_{DET2}$ . VD2 senses an over-discharge condition, the DO pin goes to a "Low" level, and the external discharge control Nch MOSFET turns off. The IC enters a low current standby mode after detection of an over–discharged voltage by VD2. Supply current then reduces to approximately 0.3  $\mu$ A. During standby mode, only the charger detector operates.

VD2 can only reset after connecting the pack to a charger. While  $V_{DD}$  remains under the over-discharge detector threshold,  $V_{DET2}$ . discharge current can flow through the parasitic diode of the external discharge control FET. The DO level goes "High" when the cell voltage rises above  $V_{DET2}$  due to the charging current through the parasitic diode. Connecting a charger to the battery pack will instantly set DO "High" if this causes  $V_{DD}$  to rise above  $V_{DET2}$ .

Output delay time for the over–discharge detection  $(t_{DET2})$  is fixed internally. If the voltage fault occurs within the time delay window, DO will not turn off the discharge control FET.

A CMOS buffer sets the output of the DO pin to a "High" level of  $V_{DD}$  and a "Low" level of Gnd.

#### VD3 / Excess Current Detector, Short Circuit Detector

Both the excess current detector and the short circuit detector can work when the two control FET's are on. When the voltage at the P– pin rises to a value between the short circuit protection voltage,  $V_{SHORT}$ , and the excess current threshold,  $V_{DET3}$ , the excess current detector operates. Increasing  $V_{(P-)}$  higher than  $V_{SHORT}$  enables the short circuit detector. The DO pin then goes to a "Low" level, and the external discharge control Nch MOSFET turns off.

Output delay time for excess current detection ( $t_{DET3}$ ) is fixed internally. If the excess current fault occurs within the time delay window, DO will not turn off the discharge control FET. However, when the short circuit protector is enabled, DO can turn off the discharge control FET. Its delay time is approximately 10 µs.

The P-pin has a built-in pull down resistor, typically  $100 \text{ k}\Omega$ , which connects to the Gnd pin. Once an excess current or short circuit fault is removed, the internal resistor

pulls  $V_{(P-)}$  to the Gnd pin potential. Therefore, the voltage from P- to Gnd drops below the current detection thresholds and DO turns the external MOSFET back on.

**NOTE:** If  $V_{DD}$  voltage is higher than the over-discharge voltage threshold,  $V_{DET2}$ , when excess current is detected

the IC will not enter a standby mode. However, if  $V_{DD}$  is below  $V_{DET2}$  when excess current is detected, the IC will enter a standby mode. This will not occur when the short circuit detector activates.

Figure 22. Timing Diagram / Operational Description

Figure 23. Typical Application Circuit

#### **Technical Notes**

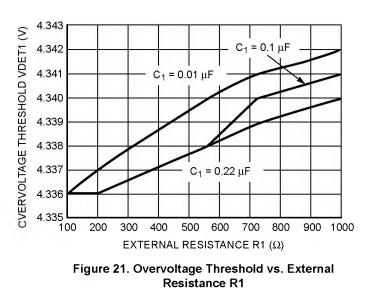

R1 and C1 will stabilize a supply voltage to the NCP800. A recommended R1 value is less than 1 k $\Omega$ . A larger value of R1 leads to higher detection voltage because of shoot through current into the IC.

R2 and C2 stabilize P– pin voltage. Larger R2 values could possibly disable reset from over–discharge by connecting a charger. Recommended values are less than 1 k $\Omega$ . After an over–charge detection even connecting a battery pack to a system could probably not allow a system to draw load current if one uses a larger R2C2 time constant. The recommended C2 value is less than 1  $\mu$ F.

R1 and R2 can operate as a current limiter against setting cell reverse direction or for applying excess charging voltage to the IC and battery pack. Smaller R1 and R2 values may cause excessive power consumption over the specified power dissipation rating. Therefore R1 + R2 should be more than 1 k $\Omega$ .

The time constants R1C1 and R2C2 must have a relation as follows:

# $R1C1 \le R2C2$

If the R1C1 time constant for the Vcell pin is larger than the R2C2 time constant for the P– pin. the IC might enter a standby mode after detecting excess current. This was noted in the operating description of the current detectors.