N1068B: 0 to +75°C

# DIGITAL 10,000 SERIES ECL

#### **DESCRIPTION**

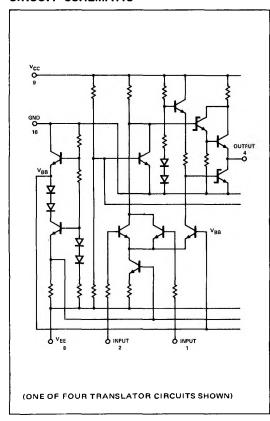

Four level translators for converting ECL signal levels to TTL or DTL logic levels. The 1068 incorporates familiar Schottky "totem pole" outputs to provide high speed operation.

#### **FEATURES**

- FAST PROPAGATION DELAY = 5.0 ns TYP

- POWER DISSIPATION = 360 mW/PACKAGE TYP

- SCHOTTKY TTL TOTEM POLE OUTPUTS

- RECOMMENDED POWER SUPPLIES:

$V_{CC}$  = +5.0 V DC ±5%

$V_{EE} = -5.2 \text{ V DC } \pm 5\%$

FOUR TRANSLATORS PER PACKAGE

#### CIRCUIT SCHEMATIC

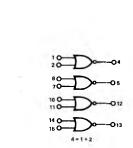

## LOGIC DIAGRAM AND PIN CONFIGURATION POSITIVE LOGIC

#### **NEGATIVE LOGIC**

Gnd = 16 V<sub>CC</sub> (+5.0 Vdc) = 9 VEE (-5.2 Vdc) = 8

DC Input Loading Factor = 2.5 (ECL) DC Output Loading Factor = 10 (TTL)

| ECTRICA!                                                                                                 | LCH    | AKA          | CI           | EK        | 151                                       | IÇS    |        |                    |                                                          |                                                    | TEST VO              | TAGE/CURRENT V       | ALUES          |                       |     |          |      |

|----------------------------------------------------------------------------------------------------------|--------|--------------|--------------|-----------|-------------------------------------------|--------|--------|--------------------|----------------------------------------------------------|----------------------------------------------------|----------------------|----------------------|----------------|-----------------------|-----|----------|------|

|                                                                                                          |        |              |              |           |                                           | @ Test | Valts  |                    |                                                          |                                                    |                      |                      | Adc            | İ                     |     |          |      |

| Fest procedures are shown<br>for one translator. The other translators<br>are tested in the same manner. |        |              |              |           | Températura<br>0°C<br>1088 +25°C<br>7 5°C |        |        | VIL min to VIL max | VIH min to VIH max                                       | VIH max                                            | V <sub>CC</sub>      | VEE                  | 10L            | юн                    | Ì   |          |      |

|                                                                                                          |        |              |              |           |                                           |        |        | -5.2 to -1.350     | -1.046 to -0.740<br>-1.000 to -0.700<br>-0.925 to -0.825 | -0.700<br>                                         | +5.0<br>+5.0<br>+5.0 | -5.2<br>-5.2<br>-5.2 | 2·<br>20<br>20 | -2.0                  | 1   |          |      |

|                                                                                                          |        |              |              |           |                                           |        |        |                    |                                                          |                                                    |                      |                      |                | 2.0                   | 4   |          |      |

|                                                                                                          |        |              |              |           |                                           |        |        |                    |                                                          |                                                    |                      |                      |                | -2.0                  | 1   |          |      |

|                                                                                                          |        | Pin<br>Under | N1088 Test L |           |                                           |        | Limits |                    |                                                          | TEST VOLTAGE/CURRENT APPLIED TO PINS LISTED BELOW: |                      |                      |                |                       |     | 1        |      |

|                                                                                                          |        |              | 0°C          |           | +25°C                                     |        | +75°C  |                    |                                                          | <b></b>                                            | т                    |                      |                |                       |     |          | ╄    |

| Characteristic                                                                                           | Symbol | Test         | Min          | Max       | Min                                       | Мея    | Min    | Max                | Unit                                                     | VIL min to VIL max                                 | ViH min to VIH max   | VIH max              | Vcc            | VEE                   | IOL | ЮН       | Gn   |

| Positive Supply                                                                                          | 1ссн   | 9            | -            | -         | -                                         | 60     | -      | -                  | mAdc                                                     | _                                                  | -                    | 1,2,8,7,10,14,15     | 9              | 8                     | -   | -        | 16   |

| Drain Current                                                                                            | ICCL   | 9            | -            | -         | -                                         | 45     | -      | -                  | mAdc                                                     | -                                                  | -                    | -                    | 9              | 1,2,6,7,8,10,11,14,15 | -   | -        | 116  |

| Negative Supply                                                                                          | 1E     | R            | -            | -         | -                                         | 60     | -      | -                  | mAde                                                     | -                                                  | - "                  | _                    |                | 1,2,6,7,8,10,11,14,15 | -   | -        | 16   |

| Drain Current                                                                                            |        |              |              |           |                                           |        |        |                    |                                                          |                                                    |                      |                      |                |                       |     |          | i    |

| Input Current                                                                                            | lin    | 1            | _            | -         | -                                         | 250    | -      | -                  | μAdc                                                     | -                                                  | 1                    | -                    | 9              | 2,6,7,8,10,11,14,15   | -   | -        | 16   |

|                                                                                                          |        | 2            | -            | -         | -                                         | 250    | -      | -                  | μAdc                                                     | -                                                  | 2 .                  | -                    | 9              | 1,6,7,8,10,11,14,15   |     | <u> </u> | 16   |

| Input Lenkage                                                                                            | 1B     | 1            | -            | -         | -                                         | 0.5    | -      | 1.0                | µAdc                                                     | - '                                                | -                    | -                    | 9              | 1,8                   | -   | ~        | 16   |

| Current                                                                                                  |        | 2            | -            | <u>1 </u> | L                                         | 0.5    | -      | 1,0                | µ Adc                                                    | -                                                  |                      |                      | 9              | 2.8                   | -   | L =      | 1 16 |

| Output Voltage High                                                                                      | VOH    | 4            | 24           | -         | 2.4                                       | -      | 24     | -                  | Vdc                                                      | 2                                                  | -                    | -                    | 9              | R                     | -   | 3        | 1€   |

|                                                                                                          |        | 4            | 2.4          | 1 -       | 2.4                                       | -      | 2.4    | -                  | Vdc                                                      | 1                                                  | _                    |                      | 9              | 8                     | -   | 3        | 16   |

| Output Valtage Low                                                                                       | VOL    | 4            |              | 0.6       | - :                                       | 0.6    | -      | 0.6                | Vdc                                                      | -                                                  | 1                    | -                    | 9              | 2,6,7,8,10,11,14,15   | 3   | -        | 1€   |

|                                                                                                          |        | 4            | -            | 0.5       | -                                         | 0.5    | -      | 0.5                | Vdc                                                      | -                                                  | 2                    | - 7                  | 9              | 1,6,7,8,10,11,14,15   | 3   | l -      | 16   |

| Output Short Circuit<br>Current                                                                          | 'sc    | 4            | - 30         | -90       | -30                                       | -90    | -30    | 90                 | mAdc                                                     | -                                                  | -                    | -                    | 8              | 1,2,6,7,8,10,11,14,15 |     | -        | 3,1  |

|                                                                                                          |        |              | Тур          | Max       | Тур                                       | Max    | Тур    | Max                | 1                                                        | Pulsa in                                           | Pulse Cut            |                      | 1              |                       |     |          |      |

| Switching Times                                                                                          | t1-4+  | 4            |              |           | 5.0                                       |        |        |                    | ns                                                       | 1                                                  | 4                    | -                    | 9              | 2,6,7,8,10,11,14,15   | _   |          | 16   |

|                                                                                                          | 11+4   | 1            | -            | -         |                                           | -      | -      | -                  | 1 1                                                      | 1                                                  | 1                    | -                    |                | 2,6,7,8,10,11,14,16   | -   | 1 -      | lι   |

|                                                                                                          | 12-4+  | 1            | -            | -         | 1                                         | -      | -      | -                  | 1                                                        | 2                                                  | 1                    | _                    | 1              | 1,6,7,8,10,11,14,15   | -   | -        | Į į  |

|                                                                                                          | 12+4-  |              | l –          | -         | 1                                         | _      | -      | -                  | 1                                                        | 2                                                  | 1                    | _                    |                | 1,6,7,8,10,11,14,15   | -   | -        |      |

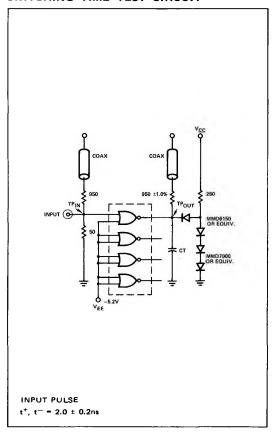

## SWITCHING TIME TEST CIRCUIT

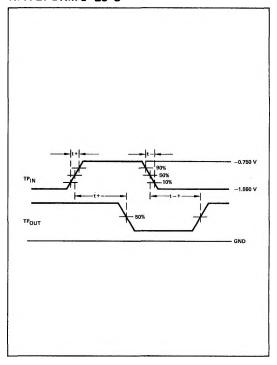

## WAVEFORM@ 25°C

The coax delays from input to scope and output to scope must be matched. The scope must be terminated in 50-ohm impedance. The 950-ohm resistor and the scope termination impedance constitute a 20:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

$\mathrm{C}_{\mathsf{T}} = 25\,\mathrm{pF} = \mathrm{total}$  parasitic capacitance, which includes probe, wiring, and load capacitances.

## ECL 1,000/10,000 SERIES PRODUCT INFORMATION

#### 19.999 SERIES ADVANTAGES

- Best system cost Performance available in a standard integrated circuit family.

- Factor of 2-or-more higher system performance than Schottky TTL.

- Complete family of SS1, interface elements, and high performance MS1, with memories coming soon.

- ECL 10,000 Series includes MECL 10,000 equivalents and Signetics-originated 10,000 Series designs.

- Offers designers the logic power of ECL Open emitter logic, simultaneous complementary outputs, transmission line capability.

- Offers designers system-optimized circuit characteristics Excellent speed power product, excellent propagation delay/ rise time ratio, excellent noise immunity/noise generation ratio, transmission line capability, differential interface capability, and high immunity from power supply variations (±5% recommended, ±10% results in minimal change in system characteristics).

- Compatible with transmission line environment, two-sided printed circuit boards, standard fan cooling techniques. Less support hardware required than Schottky TTL for many system designs.

- Low noise generation capability Complementary balancedload outputs, optimized propagation delay/rise time ratio, minimum "1"/"0" power imbalance.

- Directly compatible with MECL III family. Also compatible with ECL II/MECL II family with some reduction in noise immunity at the interface.

- These products contain a temperature compensated internal bias which ensures that the threshold point tracks with the center of the transition region over temperature.

#### 19,999 SERIES TECHNOLOGY

- Signetics thin-epitaxial high performance, high volume production process.

- Advanced circuit design techniques used:

Internal Emitter-Dot 'OR' Logic

Internal Collector-Dot 'AND' Logic

Internal Stacked Series Gating

Single Stage Delay Exclusive OR Gates

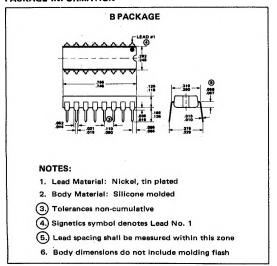

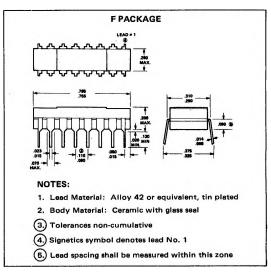

#### PACKAGE INFORMATION

#### PACKAGE TYPES

- SSI, MSI and memories will be available in cerdip packages.

Signetics new designation F specifies cerdip packages or any number of leads. (Previously E specified 16 lead cerdip).

- Presently SSI, and later some MSI and memories will be available in Signetics' double-encapsulated silicone dip with nickel lead frame. This provides minimum thermal resistance and hence maximum thermal compatibility with cerdip packages.

#### **MAXIMUM RATINGS**

| CHARACTERISTIC                             | SYMBOL    | RATING           | UNIT                 |      |

|--------------------------------------------|-----------|------------------|----------------------|------|

| Power Supply Voltage (V <sub>CC</sub> = 0) | Note 1    | VEE              | -8                   | Vdc  |

| input Voltage (V <sub>CC</sub> = 0)        | Note 1    | V <sub>IN</sub>  | 0 to V <sub>EE</sub> | Vdc  |

| Output Source Current                      | Note 1    | ' <sub>0</sub>   |                      |      |

| Continuous                                 |           | 1                | 50                   | mAdc |

| Surge                                      |           |                  | 100                  | mAdc |

| Storage Temperature Range                  | Note 1    | T <sub>stg</sub> | -55 to +125          | °c   |

| Operating Junction Temperature             | Note 1    | TJ               | 125                  | °c   |

| Operating Temperature Range                | Note 2    | TA               | -30 to +85           | °c   |

| DC Fan-Out (Gates and Flip-Flops)          | Notes 2,3 | _                | 70                   | -    |

| Power Supply Regulation Required           | Note 2    | _                | ±10%                 | –    |

#### NOTES:

- 1. Ratings above which device life may be impaired.

- Recommended maximum rating above which performance may be degraded.

- 3. AC fan-out is defined by desired system performance.

#### ORDERING INFORMATION

- 101XX F Specifies a 10,000 Series product in Cerdip Dualin-Line package, operating temperature range -30°C to +85°C (intermediate Range). (F is Signetics' new designation for Cerdip).

- 101XX B Specifies a 10,000 Series product in 16 pin Silicone

Dual-in-Line package, operating temperature range

-30°C to +85°C (intermediate Range).

Availability of a device in a particular package is indicated on the appropriate product Data Sheet.

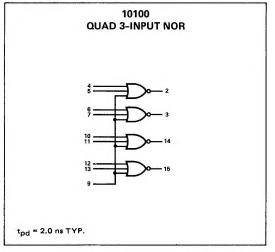

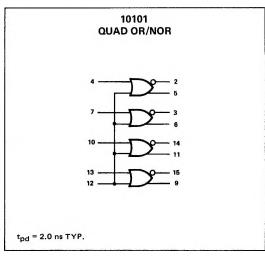

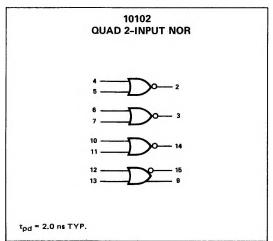

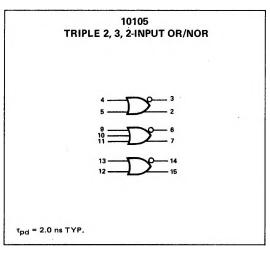

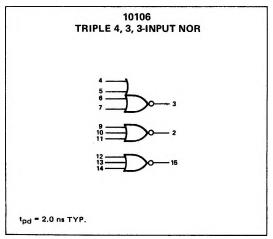

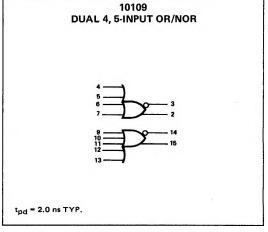

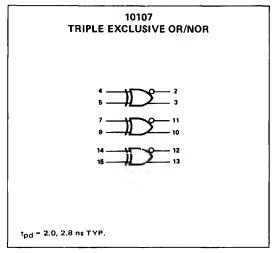

## LOGIC DIAGRAMS: BASIC GATES

NOTES: V<sub>CC1</sub> = 1, V<sub>CC2</sub> = 16, V<sub>EE</sub> = 8

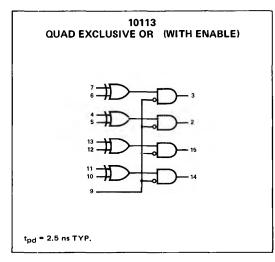

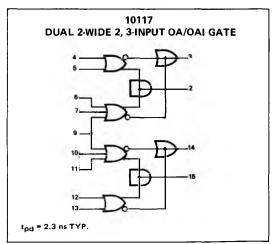

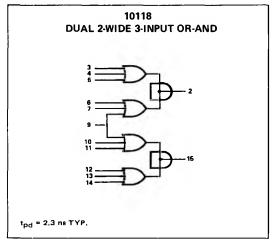

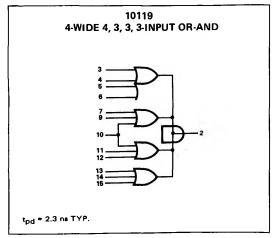

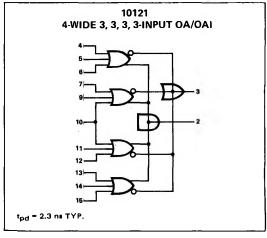

## LOGIC DIAGRAMS: COMPLEX GATES

NOTES: VCC1 = 1, VCC2 = 16, VEE = 8

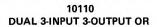

#### LOGIC DIAGRAMS: MULTIPLE OUTPUT GATES

$t_{pd} = 2.4 \text{ ns TYP. (ALL OUTPUTS LOADED)}$

## 10210 DUAL 3-INPUT 3-OUTPUT OR

tpd = 1.7 ns TYP. (ALL OUTPUTS LOADED)

# 10111 DUAL 3-INPUT 3-OUTPUT NOR

tod = 2.4 ns TYP. (ALL OUTPUTS LOADED)

#### 10211 DUAL 3-INPUT 3-OUTPUT NOR

$t_{pd} = 1.7 \text{ ns TYP.}$  (ALL OUTPUTS LOADED)

#### 10112 DUAL 3-INPUT 2-NOR/1-OR

tpd = 2.4 ns TYP. (ALL OUTPUTS LOADED)

#### 10212 DUAL 3-INPUT 2-NOR/1-OR

tpd = 1.7 ns TYP. (ALL OUTPUTS LOADED)

NOTES: VCC1 = 1, 15, VCC2 = 16, VEE = 8

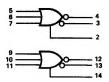

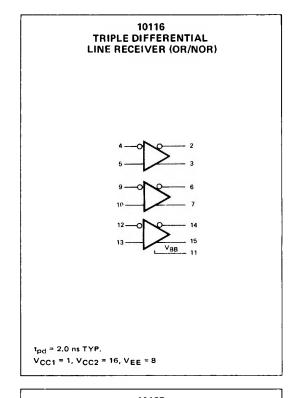

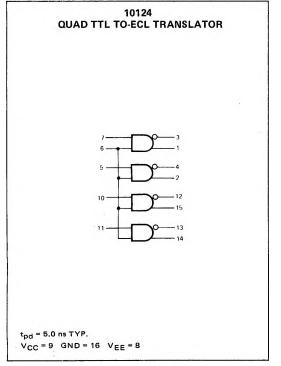

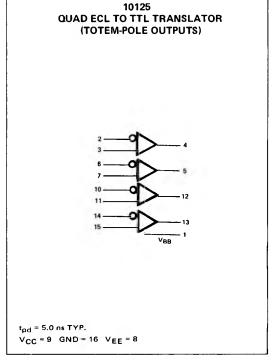

#### LOGIC DIAGRAMS: INTERFACE CIRCUITS

V<sub>CC1</sub> = 1, V<sub>CC2</sub> = 16, V<sub>EE</sub> = 8

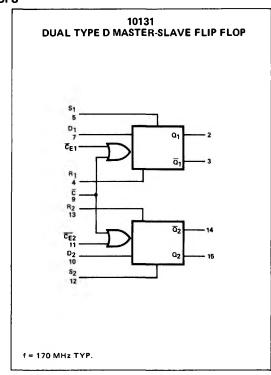

#### LOGIC DIAGRAMS: DUAL LATCHES AND FLIP-FLOPS

NOTES: V<sub>CC1</sub> = 1, V<sub>CC2</sub> = 16, V<sub>EE</sub> = 8

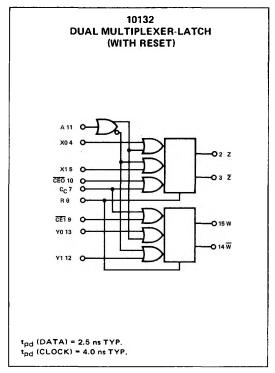

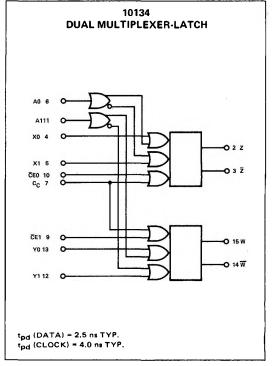

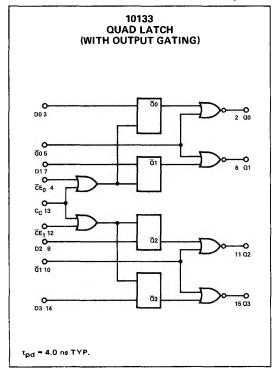

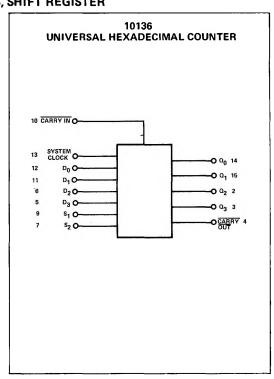

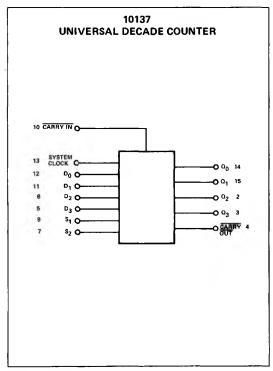

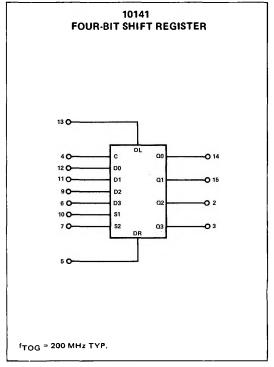

## LOGIC DIAGRAMS: MSI: QUAD LATCH, COUNTERS, SHIFT REGISTER

NOTES:  $V_{CC1} = 1$ ,  $V_{CC2} = 16$ ,  $V_{EE} = 8$

POSITIVE LOGIC: HIGH LEVEL = '1'

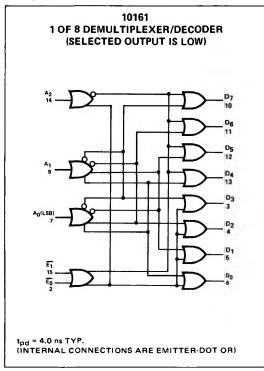

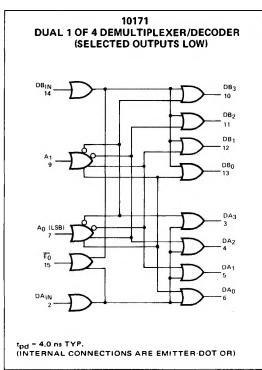

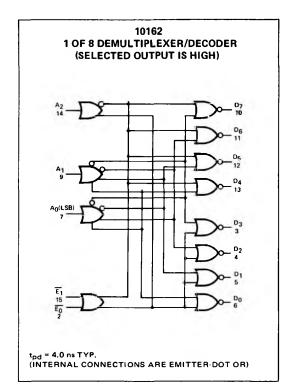

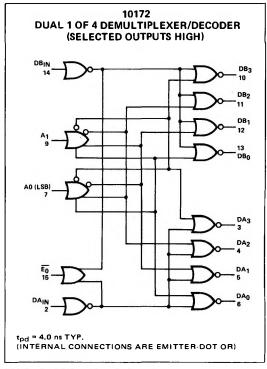

#### **LOGIC DIAGRAMS: MSI DECODERS**

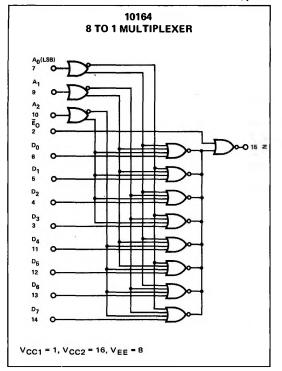

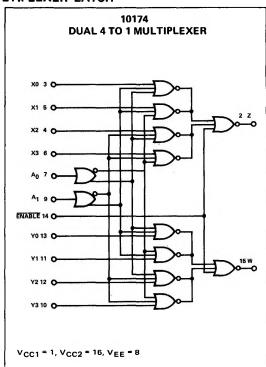

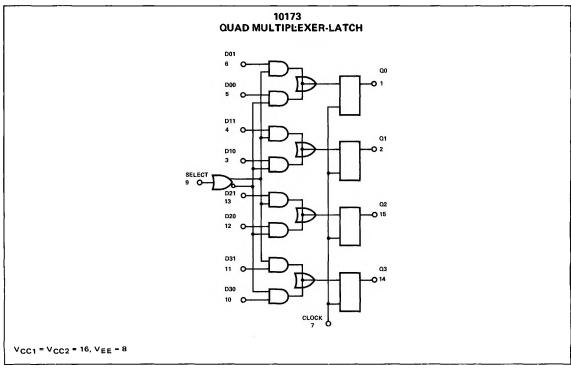

## LOGIC DIAGRAMS: MSI: MULTIPLEXER\$, QUAD MULTIPLEXER-LATCH

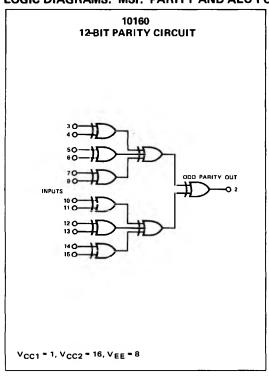

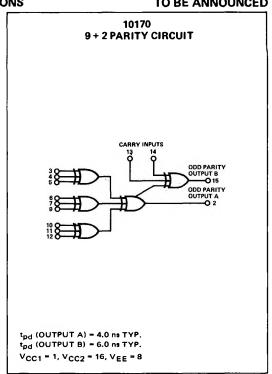

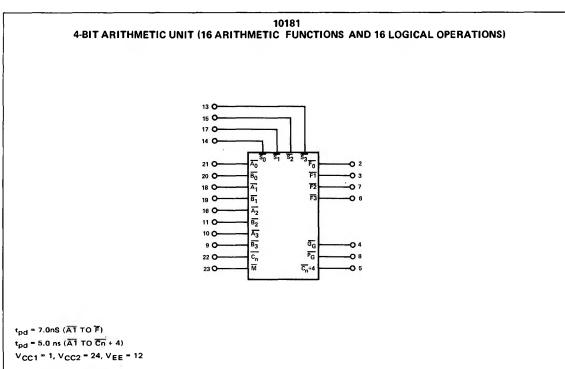

## LOGIC DIAGRAMS: MSI: PARITY AND ALU FUNCTIONS

## TO BE ANNOUNCED