Ordering number: EN3653B

## **OVERVIEW**

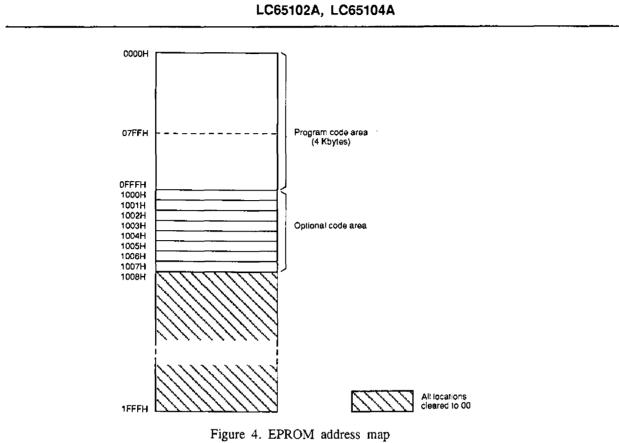

The LC65102A and LC65104A are 4-bit, single-chip microprocessors that incorporate 2 Kbyte ROM and  $128 \times 4$ -bit RAM, and 4 Kbyte ROM and  $256 \times 4$ -bit RAM, respectively, making them ideal for timer controllers, audiovisual equipment and domestic appliances.

The LC65102A and LC65104A comprise one 2-bit and five 4-bit bidirectional I/O ports, a three-wire serial interface, an eight-channel, 8-bit A/D converter and a 14-bit D/A converter that can be configured as separate 6-bit and 8-bit modules or as a single 14-bit module. An on-chip oscillator can be directly connected to either an external crystal or ceramic resonator, or alternatively, an external oscillator can be used.

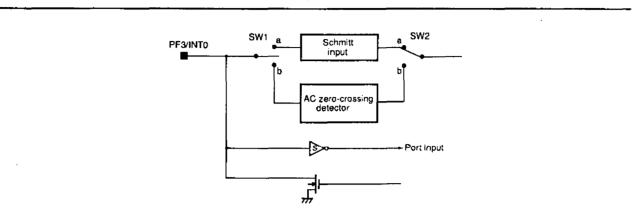

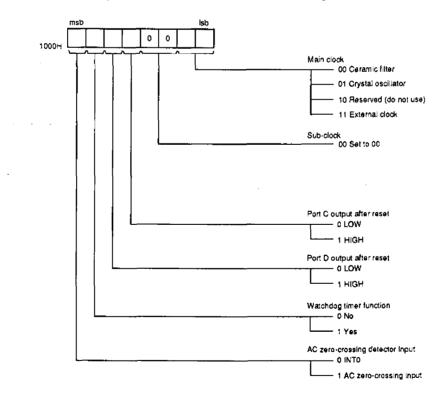

The mask options for the LC65102A and LC65104A comprise a 14-bit general-purpose timer, used to generate pulsewidth modulated output or tone output, a 14-bit clock or overrun watchdog timer, and an AC zero-crossing detector or Schmitt trigger input circuit. Two power-saving standby modes are also provided.

The LC65102A and LC65104A operate over a 2.7 to 6.0 V supply range and are available in 30-pin SDIPs. A 30-pin SMFP is currently under development.

## FEATURES

- 77 instructions

- On-chip 2 Kbyte ROM and 128 × 4-bit RAM (LC65102A) and 4 Kbyte ROM and 256 × 4-bit RAM (LC65104A)

- 0.92  $\mu$ s (4.33 MHz clock and  $V_{DD} \ge 4.5$  V) or 1.84  $\mu$ s (2.17 MHz clock and  $V_{DD} \ge 4.0$  V) minimum instruction cycle times

- Software-selectable system clock

- Four banks of eight working registers and 16 flags

- Eight-level stack

- 22 bidirectional I/O lines, including 12 multiplexed lines

- 8-bit precision, eight-channel tracking A/D converter

- · 8-bit interval timer for PWM D/A converter and music generator

- 14-bit timer for calendar/clock function

- Separate 6-bit and 8-bit or single 14-bit D/A converter configurations

- Serial I/O interface

- AC zero-crossing detector mask option

- Two external interrupts, two timer interrupts and one serial I/O interrupt

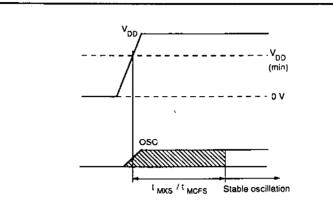

- Wait function allows oscillator to stabilize after reset

- On-chip oscillator supports 4.19 MHz crystal, 400 kHz or 4.0 MHz ceramic resonators

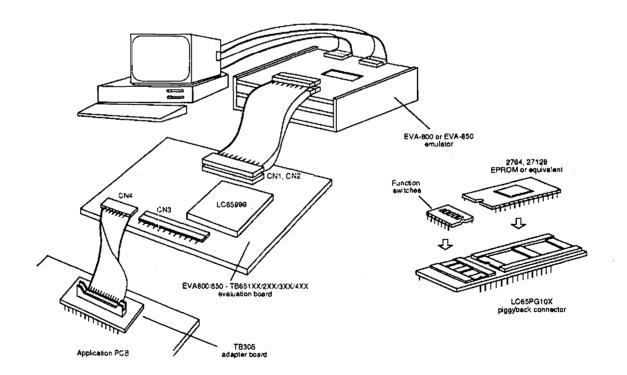

- LC65999 evaluation chip, EVA800/850 emulator, TB65XXX adapter board and LC65PG10X piggyback connector evaluation tools available

- HALT/HOLD standby functions

- 2.7 to 6.0 V supply operating range

- 30-pin SDIP and 30-pin SMFP (under development)

# SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

N1193JN B8-0195/8161 JN No.3653-1/24

### \_\_\_\_\_

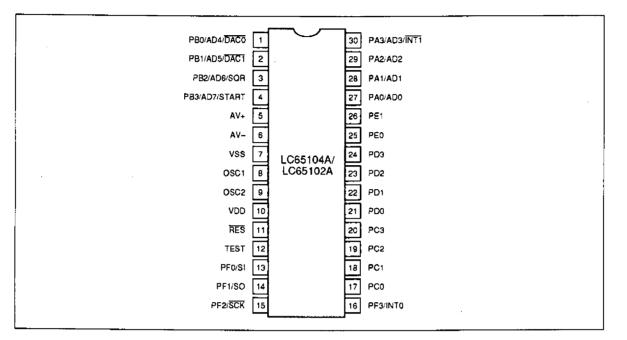

# PIN ASSIGNMENT

LC65102A, LC65104A

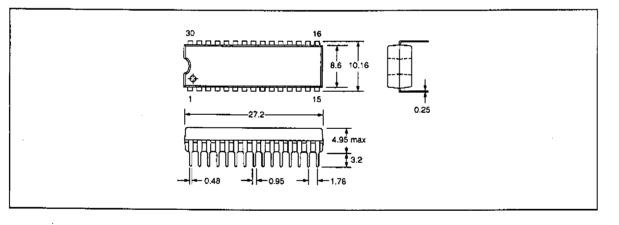

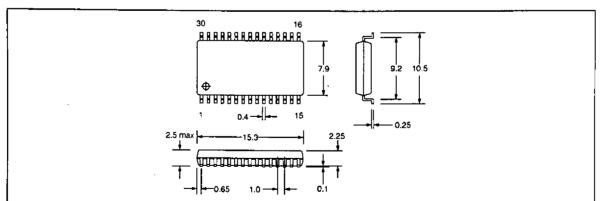

# PACKAGE DIMENSIONS

Unit: mm

3061-DIP30S

## 3073A-MFP30S

No. 3653-2/24

#### **BLOCK DIAGRAM** PA0/AD0 PA1/AD1 PA2/AD2 PA3/AD3/INT1 I/O port A বচ AV-8-bit ADC AV- $\overline{2}$ PB0/AD4/DACO PB1/AD5/DAC1 I/O port B P82/AD6/SOR 6-bit PWM DAC/ 6-bit programmable prescaler 8-bit (14-bit) PWM DAC/8-bit (nterval timer Prescaler I/O bus PE0 🛉 I/O port E Standby controller PE1 📥 PC0 🗰 256(128) x 4-bit RAM 4096(2048 × 8-bit ROM Program counter PC1 I/O port C F WR 14-bit timebase imer/counte (watchdog timer) РСЗ 🖬 Д Eight-leve stack Data pointer PD0 Instruction decoder Instruction register PD1 +++ I/O port D ⊐⇔⊾≝₀≓⇔ PD3 🛉 System t <del>ک</del> $\bigcirc$ System clock controller $\bigcirc$ PF0/SI 1) PF1/SO PF2/SCK 1/O port F STS CF F CSF **`** interrupt controller Aegister E Accumulato ALU OSC1 Ð 4,19 MHz oscillator ٤) OSC2 8-bit serial I/O port I/O bus TEST A RES AC zero-crossing delector PF3/INTO 🛉 vss PF3/INT1

Note

Values in parentheses indicate LC65102A RAM and ROM capacities

# PIN DESCRIPTION

| Number | Name          | Description                                                                             |

|--------|---------------|-----------------------------------------------------------------------------------------|

| 1      | PB0/AD4/DAC0  |                                                                                         |

| 2      | PB1/AD5/DAC1  | 4-bit I/O port B multiplexed with A/D converter lines AD4 to AD7, D/A lines DACO        |

| 3      | PB2/AD6/SQR   | and DAC1, square wave pulse output SQR and standby control line START.<br>Normally HIGH |

| 4      | PB3/AD7/START |                                                                                         |

| 5      | AV+           |                                                                                         |

| 6      | AV            | A/D converter reference voltage input                                                   |

| 7      | VSS           | Ground                                                                                  |

| 8      | OSC1          | External crystal or ceramic resonator connection or external clock input                |

| 9      | OSC2          | External crystal or ceramic resonator connection                                        |

| 10     | VDD           | 5 V supply                                                                              |

| 11     | RES           | System reset input. Normally HIGH                                                       |

| 12     | TEST          | Test pin. Normally LOW                                                                  |

# LC65102A, LC65104A

No. 3653-3/24

| Number | Name         | Description                                                                       |  |  |  |  |  |

|--------|--------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| 13     | PF0/SI       |                                                                                   |  |  |  |  |  |

| 14     | PF1/SO       | 4-bit I/O port F multiplexed with serial input and output lines SI and SO, serial |  |  |  |  |  |

| 15     | PF2/SCK      | clock output SCK and interrupt request input INTO. Normally HIGH                  |  |  |  |  |  |

| 16     | PF3/INTO     |                                                                                   |  |  |  |  |  |

| 17     | PCO          |                                                                                   |  |  |  |  |  |

| 18     | PC1          |                                                                                   |  |  |  |  |  |

| 19     | PC2          | -4-bit I/O port C                                                                 |  |  |  |  |  |

| 20     | PC3          |                                                                                   |  |  |  |  |  |

| 21     | PDO          |                                                                                   |  |  |  |  |  |

| 22     | PD1          |                                                                                   |  |  |  |  |  |

| 23     | PD2          | 4-bit 1/0 port D                                                                  |  |  |  |  |  |

| 24     | PD3          |                                                                                   |  |  |  |  |  |

| 25     | PEO          |                                                                                   |  |  |  |  |  |

| 26     | PE1          | 2-bit I/O port E. Normally HIGH                                                   |  |  |  |  |  |

| 27     | PA0/AD0      |                                                                                   |  |  |  |  |  |

| 28     | PA1/AD1      | 4-bit I/O port A multiplexed with A/D converter input lines ADO to AD3 and        |  |  |  |  |  |

| 29     | PA2/AD2      | interrupt input INT1. Normally HIGH                                               |  |  |  |  |  |

| 30     | PA3/AD3/INT1 | 1                                                                                 |  |  |  |  |  |

# SPECIFICATIONS

# Absolute Maximum Ratings

| Parameter                                                                     | Symbol           | Rating                        | Unit |

|-------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage range                                                          | Voo              | -0.3 to 7.0                   | V    |

| TEST, RES and OSC1 input voltage range                                        | V <sub>11</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | v    |

| AV * input voltage range                                                      | V <sub>12</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | v    |

| AV – input voltage range                                                      | Via              | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Ports A, B and F3 input/output voltage range                                  | Viot             | -0.3 to V <sub>DD</sub> + 0.3 | v    |

| Ports C, D and E, and F0 to F2 input/output voltage range (open-drain output) | VIC2             | -0.3 to 15.0                  | v    |

| Ports C, D and E, and FO to F2 input/output voltage range (totem-pole output) | V <sub>IO3</sub> | -0.3 to VDD + 0.3             | v    |

| Ports A, B, E and F peak output current range                                 | lop1             | -2 to 10                      | mA   |

| Ports C and D peak output current range                                       | l <sub>OP2</sub> | -2 to 20                      | mA   |

| Ports A, B, E and F average output current per<br>pin range                   | I <sub>DA1</sub> | -2 to 10                      | mA   |

| Ports C and D average output current per pin range                            | I <sub>CA2</sub> | 2 to 20                       | mA   |

|                                                                               |                  |                               |      |

| Ports A, B, E and F average current per port range | Σloai | -24 to 120 | mA |

|----------------------------------------------------|-------|------------|----|

| Ports C and D average current per port range       | ΣΙΟΑ2 | -20 to 100 | mA |

No. 3653-4/24

| Parameter                    | Symbol           | Rating     | Unit   |

|------------------------------|------------------|------------|--------|

| 30-pin DIP power dissipation | Po               | 400        | mW     |

| 30-pin MFP power dissipation | PD               | 200        | mW     |

| Operating temperature range  | Topg             | -40 to 85  | deg. C |

| Storage temperature range    | T <sub>stg</sub> | -55 to 125 | deg. C |

# **Recommended Operating Conditions**

$V_{ss} = 0$  V,  $T_a = 25$  deg. C

| Parameter            | Symbol          | Rating     | Unit |

|----------------------|-----------------|------------|------|

| Supply voltage       | V <sub>DD</sub> | 5          | V    |

| Supply voltage range | V <sub>DD</sub> | 2.7 to 6.0 | v    |

# **Electrical Characteristics**

$V_{DD}$  = 2.7 to 6.0 V,  $V_{SS}$  = 0 V,  $T_{a}$  = -40 to 85 deg. C unless noted otherwise

| Parameter                                                                  | Symbol Condition |                                                                           | Rating              |     |                     | Unit |

|----------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|---------------------|-----|---------------------|------|

| Parameter                                                                  |                  |                                                                           | min                 | typ | max                 | Uan  |

|                                                                            | V <sub>DD1</sub> | 0.92 $\mu s \leq t_{cyc} < 36 \ \mu s$                                    | 4.5                 | -   | 6.0                 | ٧    |

| Supply voltage                                                             | V <sub>DD2</sub> | 1.84 μs ≤ t <sub>cyc</sub> < 36 μs                                        | 4.0                 | -   | 6.0                 | ٧    |

|                                                                            | V <sub>DD3</sub> | 9.8 µs ≤ t <sub>eye</sub> < 36 µs                                         | 2.7                 | -   | 6.0                 | ۷    |

| Standby supply voltage                                                     | Vst              |                                                                           | 1.8                 | _   | 6.0                 | ٧    |

| Port E and F0 to F2 HIGH-level<br>nput voltage (open-drain output)         | ViH1             | n-channel transistor OFF                                                  | 0.80V <sub>DD</sub> | -   | 13.5                | v    |

| Port E and FO to F2 HIGH-level<br>input voltage (totem-pole output)        | V <sub>iH2</sub> | n-channel transistor OFF                                                  | 0.80V <sub>DD</sub> | -   | Vod                 | ٧    |

| Ports A and B HIGH-level input<br>voltage                                  | ViHa             | n-channel transistor OFF                                                  | 1.9                 | -   | VDD                 | v    |

| Ports C and D HIGH-level input                                             | V <sub>IH4</sub> | n-channel transistor OFF,<br>$V_{DD} = 4.5$ to 6.0 V                      | 0.70V <sub>DD</sub> | _   | 13.5                | v    |

| voltage (open-drain output)                                                |                  | n-channel transistor OFF                                                  | 0.75V <sub>DD</sub> | -   | 13,5                | V    |

| Ports C and D HIGH-level input                                             | Vihs             | n-channel transistor OFF,<br>$V_{DD} = 4.5$ to 6.0 V                      | 0.70V <sub>DD</sub> | _   | VDD                 | v    |

| voltage (totem-pole output)                                                |                  | n-channel transistor OFF                                                  | 0.75V <sub>DD</sub> | _   | V <sub>DD</sub>     | v    |

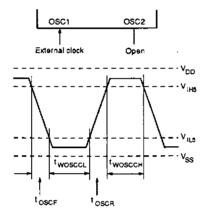

| OSC1, START, PF3/INTO and<br>INT1 HIGH-level input voltage.<br>See note 1. | V <sub>IH6</sub> | n-channel transistor OFF,<br>external oscillator input.<br>See figure 16. | 0.80V <sub>DD</sub> | _   | Voo                 | v    |

| RES HIGH-level input voltage                                               |                  | $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$                                  | 0.80V <sub>DD</sub> | -   | Voo                 | v    |

|                                                                            | V <sub>IH7</sub> | V <sub>DD</sub> = 1.8 to 6.0 V                                            | 0.85V <sub>DD</sub> |     | VDD                 | ٧    |

| Port E and FO to F2 LOW-level                                              | VIL1             | n-channel transistor OFF,<br>$V_{DD} = 4.5$ to 6.0 V                      | Vss                 | -   | 0.20V <sub>DD</sub> | v    |

| input voltage                                                              |                  | n-channel transistor OFF                                                  | Vss                 |     | 0.15V <sub>DD</sub> | ٧    |

|                                                                            |                  |                                                                           |                     |     |                     |      |

| Ports A and B LOW-level input voltage | V <sub>IL2</sub> | n-channel transistor OFF, $V_{DD} = 4.5$ to 6.0 V | Vss | - | 0.5  | V |  |

|---------------------------------------|------------------|---------------------------------------------------|-----|---|------|---|--|

| vonage                                |                  | n-channel transistor OFF                          | Vss | + | 0.35 | V |  |

No. 3653—5/24

| Demonster                                                                                          |                  |                                                                                                             |                       | 11                 |                     |      |

|----------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|---------------------|------|

| Parameter                                                                                          | Symbol           | Condition                                                                                                   | min                   | typ                | max                 | Unit |

| Ports C and D LOW-level input                                                                      | Vila             | n-channel transistor OFF,<br>$V_{00} = 4.5$ to 6.0 V                                                        | Vss                   | -                  | 0.30V <sub>DD</sub> | v    |

| voltage                                                                                            |                  | n-channel transistor OFF                                                                                    | Vss                   | _                  | 0.25V <sub>DD</sub> | V    |

|                                                                                                    |                  | $V_{DD} = 4.5$ to 6.0 V                                                                                     | Vss                   | _                  | 0.20VDD             | v    |

| START LOW-level input voltage                                                                      | VIL4             | $V_{DD} = 1.8$ to 6.0 V                                                                                     | Vss                   | _                  | 0.15Vpp             | v    |

| OSC1, RES, PF3/INTO and INT1<br>LOW-level input voltage. See                                       | Vil5             | n-channel transistor OFF,<br>external oscillator input.<br>See figure 16. V <sub>DD</sub> =<br>4.5 to 6.0 V | V <sub>SS</sub>       | _                  | 0.20Voo             | v    |

| note 1.                                                                                            |                  | n-channel transistor OFF,<br>external oscillator input.<br>See figure 16.                                   | V <sub>SS</sub>       | -                  | 0.15V <sub>DD</sub> | v    |

| TEST LOW level input with set                                                                      |                  | $V_{DD} = 4.5$ to 6.0 V                                                                                     | Vss                   | -                  | 0.30V <sub>DD</sub> | v    |

| TEST LOW-level input voltage                                                                       | VIL6             |                                                                                                             | Vss                   | -                  | 0.25V <sub>00</sub> | V    |

| Ports A, B, C, D, E and F<br>HIGH-level output voltage<br>(totem-pole output)                      | V <sub>0H1</sub> | $I_{OH} = -50 \ \mu A,$<br>$V_{DD} = 4.5 \ to \ 6.0 \ V$                                                    | V <sub>DD</sub> - 1.2 | -                  | -                   | v    |

| Ports A, B, C, D, E and F<br>HIGH-level output voltage<br>(totem-pole output)                      | V <sub>OH2</sub> | I <sub>он</sub> = -10 µА                                                                                    | V <sub>DD</sub> - 0.5 | -                  | -                   | v    |

| Ports A, B, E and F HIGH-level<br>output voltage                                                   | V <sub>OL1</sub> | l <sub>oL</sub> = 5 mA,<br>V <sub>DD</sub> = 4.5 to 6.0 V                                                   | -                     | -                  | 1.5                 | V    |

|                                                                                                    | V <sub>OL2</sub> | IoL = 1.0 mA, IoL of other ports below 1 mA                                                                 | -                     | -                  | 0.5                 | V    |

| Ports C and D LOW-level output                                                                     | V <sub>0L3</sub> | $i_{OL} = 15 \text{ mA},$<br>$V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$                                       | -                     | -                  | 1.5                 | v    |

| voltage                                                                                            | V <sub>OL4</sub> | $I_{OL} = 2.0 \text{ mA}, I_{OL} \text{ of}$<br>other ports below 1 mA                                      | -                     |                    | 0.5                 | v    |

| Port F, INTO, INT1, RES and<br>START hysteresis voltage.<br>See note 1.                            | VHYS             |                                                                                                             | -                     | 0.1V <sub>DD</sub> | -                   | V    |

| Ports C, D and E, and F0 to F2<br>HtGH-level input current<br>(open-drain output)                  | Ьна              | n-channel output<br>transistor OFF (includes<br>output transistor leakage<br>current), $V_1 = 13.5$ V       | -                     | -                  | 5.0                 | μA   |

| Ports A and B, and F3<br>HIGH-level input current<br>(open-drain output).<br>See notes 1 and 5.    | liH2             | n-channel output<br>transistor OFF (includes<br>output transistor leakage<br>current), $V_I = V_{DD}$       |                       |                    | 1.0                 | μA   |

| RES HIGH-level input current                                                                       | Інз              | VI = VDD                                                                                                    |                       | -                  | 1.0                 | μA   |

| OSC1 HIGH-level input current                                                                      | liH4             | V <sub>I</sub> = V <sub>DD</sub>                                                                            | -                     | -                  | 10                  | μА   |

| Ports A, B, C, D, E and F<br>LOW-level input current<br>(open-drain output).<br>See notes 1 and 5. | հլո              | n-channel output<br>transistor OFF, V <sub>1</sub> = V <sub>SS</sub>                                        | -1.0                  |                    | _                   | μА   |

| Ports A, B, C, D, E and F<br>LOW-level input current<br>(totem-pole output).                       | l <sub>IL2</sub> | n-channel output<br>transistor OFF, VI = Vss                                                                | -1.0                  | -0.5               | -                   | mA   |

| Coo materia di and E |  |  |  |  |

|----------------------|--|--|--|--|

| See notes 1 and 5.   |  |  |  |  |

| uee notes i anu J.   |  |  |  |  |

|                      |  |  |  |  |

|                      |  |  |  |  |

No. 3653---6/24

,

| Parameter                                                                  |                    |                                                                                                                                       | 11-14 |     |     |      |

|----------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| raramoter                                                                  | Symbol             | Condition                                                                                                                             | min   | typ | max | Unit |

| RES LOW-level input current                                                | lica               | V <sub>I</sub> = V <sub>SS</sub>                                                                                                      | -60   | -25 | _   |      |

| OSC1 LOW-level input current                                               | l <sub>IL4</sub>   | V <sub>I</sub> = V <sub>SS</sub>                                                                                                      | 10    | -   | -   | μΑ   |

|                                                                            | IDDOP1             | $f_{osc} = 4 \text{ MHz},$<br>divide ratio = 1/1,<br>$t_{cyc} = 0.95  \mu \text{s},$<br>$V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$      | _     | 3   | 6   | mA   |

|                                                                            | 100002             |                                                                                                                                       | -     | 2   | 4   | mA   |

| Operating current consumption.<br>See note 4.                              | IDDOP3             |                                                                                                                                       | -     | 0.3 | 1.0 | mA   |

|                                                                            | I <sub>DDOP4</sub> |                                                                                                                                       | -     | 0.5 | 2.0 | mA   |

|                                                                            | I <sub>DDOP5</sub> | $      f_{osc} = 400 \text{ kHz}, \\       divide ratio = 1/1, \\       t_{cyc} = 10  \mu \text{s}, \\       V_{DD} = 2.7 \text{ V} $ | · _   | 150 | 500 | μA   |

|                                                                            | IDDST1             | HALT mode,<br>4.19 MHz clock,<br>V <sub>DD</sub> = 6.0 V                                                                              | _     | 0.7 | 1.5 | mA   |

|                                                                            | IDDST2             | HALT mode,<br>4.19 MHz clock<br>V <sub>DD</sub> = 2.7 V                                                                               | -     | 150 | 500 | μA   |

| Standby current consumption.<br>See note 4.                                | IDDST3             | HALT mode,<br>400 kHz clock,<br>V <sub>DD</sub> = 6.0 V                                                                               | -     | 0.7 | 1.5 | mA   |

|                                                                            | IDDST4             | HALT mode,<br>400 kHz clock,<br>V <sub>DD</sub> = 2.7 V                                                                               | _     | 100 | 300 | μА   |

|                                                                            | IDOST5             | HOLD mode,<br>V <sub>DD</sub> = 1.8 V                                                                                                 | -     | -   | 1   | μА   |

|                                                                            | lDOSTE             | HOLD mode,<br>V <sub>DD</sub> = 6.0 V                                                                                                 | -     |     | 10  | μА   |

| Ports A, B, C, D, E and F<br>p-channel MOS output transistor<br>resistance | R <sub>1ru</sub>   | n-channel output<br>transistor OFF,<br>V <sub>DD</sub> = 5 V, V <sub>1</sub> = Vss                                                    | 8     | 12  | 30  | kΩ   |

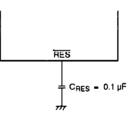

| RES input pull-up resistance                                               | Ru                 | $V_{DD} = 5 V_i V_i = V_{SS}$                                                                                                         | 100   | -   | 400 | kΩ   |

## Notes

1. This value applies when the AC zero-crossing detector option is not selected.

2. Includes n-channel output transistor leakage current (transistor OFF)

- 3. Current dissipation values apply to microprocessor circuitry. They do not include currents associated with I/O port transistors.

- 4. These values do not include I/O port transistor currents.

- 5. Includes INTO, INTI and START

No. 3653-7/24

.

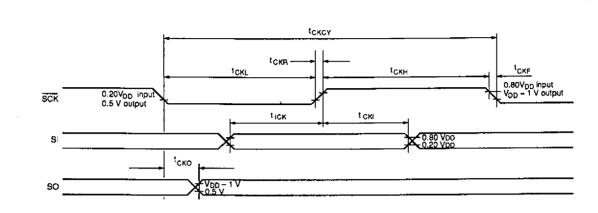

## Serlal interface

$V_{\text{DD}}$  = 4 to 6 V,  $V_{\text{SS}}$  = 0 V,  $T_{\text{a}}$  = -40 to 85 deg. C

| Demonstern                                  | <b>A</b> |                                                                                                          |                  | Rating |     |      |  |

|---------------------------------------------|----------|----------------------------------------------------------------------------------------------------------|------------------|--------|-----|------|--|

| Parameter                                   | Symbol   | Condition                                                                                                | min typ          |        | max | Unit |  |

| Input clock (SCK) period                    | LCKCY1   |                                                                                                          | 0.8              | _      | _   | μs   |  |

| Output clock (SCK) period                   | tсксу2   | See figure 19.                                                                                           | 2.0 × tcyc       | _      | _   | μs   |  |

| Input clock (SCK) LOW-level pulsewidth      | tckL1    | See figure 19. See note.                                                                                 | 0.3              | _      | -   | μs   |  |

| Output clock (SCK) LOW-level pulsewidth     | tck∟2    | See figure 19.                                                                                           | t <sub>cyc</sub> |        | _   | μs   |  |

| Input clock (SCK) HIGH-level pulsewidth     | tскнı    | See figure 19. See note.                                                                                 | 0.3              | _ ·    | -   | μs   |  |

| Output clock (SCK) HIGH-level<br>pulsewidth | tскнг    | See figure 19.                                                                                           | tcyc             | _      | -   | μs   |  |

| SI data setup time                          | tick     | Referenced to SCK                                                                                        | 0.2              | _      | -   | μs   |  |

| SI data hold time                           | tскі     | rising edge.<br>See figure 19.                                                                           | 0.2              | _      | -   | μs   |  |

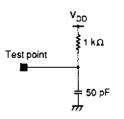

| SO propagation delay                        | tско     | Referenced to $\overline{SCK}$<br>falling edge. 1 k $\Omega$ ,<br>50 pF external load.<br>See figure 19. | -                |        | 0.5 | μs   |  |

## Note

The pullup resistor values should be set so that  $t_{CKL1}$  and  $t_{CKH1}$  are greater than 0.3  $\mu s.$

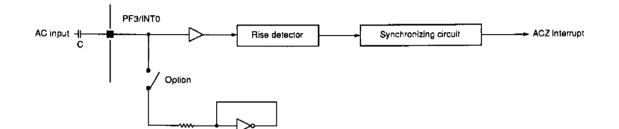

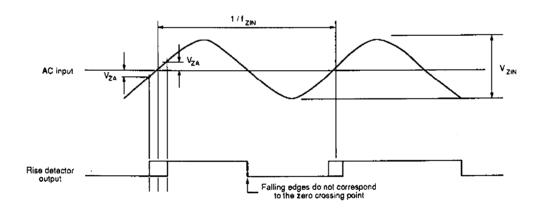

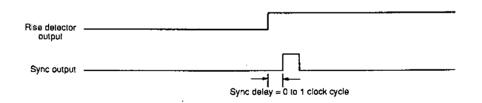

# AC zero-crossing detector input

$V_{\text{DD}}$  = 4.5 to 6.0 V,  $V_{\text{SS}}$  = 0 V,  $T_{\text{s}}$  = -40 to 85 deg. C

| Personatas                        | :<br>Dumbal         | Canditian                        |                     | Rating                    |                     | Unit             |

|-----------------------------------|---------------------|----------------------------------|---------------------|---------------------------|---------------------|------------------|

| Parameter                         | Symbol              | Condition                        | min                 | typ                       | max                 | Unit             |

| Input frequency                   | fzi                 |                                  | 40                  | -                         | 1,000               | Hz               |

| Input voltage                     | Vzi                 | C = 1 µF                         | 1.0                 | _                         | 2.4                 | V <sub>p-p</sub> |

| Detection error                   | VZA                 | 60 Hz sinewave input             |                     | -                         | ±100                | m۷               |

| HIGH-level input current          | lінz                | VI = VDD                         | -                   | -                         | 40                  | μA               |

| LOW-level input current           | litz                | V <sub>I</sub> = V <sub>SS</sub> | -40                 | -                         | -                   | μA               |

| Threshold voltage                 | Vt × Acm            |                                  | $0.3 \times V_{DD}$ | -                         | $0.7 \times V_{DD}$ | V                |

| LOW-level input threshold voltage | $V_1 \times A_{CL}$ |                                  | -                   | $V_t \times A_{CM} - 0.2$ | -                   | v                |

Note

Open-drain output with self-bias ON. See figures 21 and 22.

No. 3653—8/24

# Self-exciting oscillator

.

$V_{\text{DD}}$  = 2.7 to 6.0 V,  $V_{\text{ss}}$  = 0 V,  $T_{\text{s}}$  = -40 to 85 deg. C unless noted otherwise

| Parameter                      | Dumbal            | 0 dision                                   | T    | Rating |      | Unit |  |

|--------------------------------|-------------------|--------------------------------------------|------|--------|------|------|--|

| rarameter                      | Symbol            | Condition                                  | min  | typ    | məx  | Unix |  |

| Crystal resonator frequency    | foscx             | See figure 14.<br>See note 1.              | _    | 4.19   | _    | MHz  |  |

| Crystal oscillator start delay | t <sub>MXS</sub>  | See figure 15.                             |      | -      | 20   | ms   |  |

| Ceramic resonator frequency    | foscor            | See figure 14.<br>See note 1.              | 392  | 400    | 408  | kHz  |  |

| Ceramic oscillator start delay | t <sub>MCFS</sub> | See figure 15.                             | _    |        | 10   | ms   |  |

| Instruction cycle time         | tcyc              | See note 1.                                | 0.92 | -      | 36   | μs   |  |

| External oscillator frequency  | fxosc             | See note 1.                                | 0.39 | -      | 4.33 | MHz  |  |

| External oscillator pulsewidth | twoscch           | $V_{DD} = 4.5$ to 6.0 V.<br>See figure 16. | 70   | -      | -    | ns   |  |

|                                | twosccl           | See figure 16.                             | 140  | -      | -    | ns   |  |

| External oscillator rise time  | toscr             | San figure 16                              |      |        | 30   | ns   |  |

| External oscillator fall time  | toscr             | See figure 16.                             | -    | _      | 30   | ns   |  |

Notes

The frequency is limited by the supply voltage, operating cycle time and frequency divider ratio.

Oscillator constants are listed in table 3.

## A/D converter

$V_{\text{DD}}$  = 5.0 V ±10%,  $V_{\text{SS}}$  = 0 V,  $T_{a}$  = -40 to 85 deg. C

| Deservator              | Question |                                                                                                                                        |      | Rating |      | Unit |

|-------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|

| Parameter               | Symbol   | Condition                                                                                                                              | min  | typ    | max  | ] 0  |

| Resolution              |          |                                                                                                                                        |      | 8      | -    | bit  |

| Absolute precision      |          |                                                                                                                                        | _    | ±1     | ±2   | lsb  |

| Zero-scale error        | Ezs      | $AV + = V_{DD},$<br>$AV - = V_{SS}$                                                                                                    |      | -      | ±1   | lsb  |

| Full-scale error        | EFS      |                                                                                                                                        | · _  | -      | ±1   | lsb  |

| Conversion time         | •        | 1/1 conversion<br>speed = $26 \times t_{cyc}$<br>( $t_{cyc} = 0.92$ to 12 µs)                                                          | 24   | _      | 312  | μs   |

| Conversion time         | 1CAD     | $\begin{array}{l} 1/2 \ \ conversion \\ speed \ = \ 51 \ \times \ t_{cyc} \\ (t_{cyc} \ = \ 0.92 \ \ to \ \ 12 \ \ \mu s) \end{array}$ | 40   | -      | 612  | μs   |

|                         | AV +     |                                                                                                                                        | AV - | -      | VDD  | v    |

| Input reference voltage | AV -     |                                                                                                                                        | Vss  | -      | AV • | v    |

| Input reference current | IRIF     | $\begin{array}{l} AV^{+} = V_{DD},\\ AV^{-} = V_{SS} \end{array}$                                                                      | 75   | 150    | 300  | μΑ   |

| Analog input voltage    | VAI      |                                                                                                                                        | AV - | -      | AV + | v    |

| Analog input current    |          | Includes output<br>OFF-state leakage                                                                                                   | _    | _      | 1    | μA   |

| Analog input current | 1 <sub>AI</sub> | current, $V_{AI} = V_{DD}$        |    |   |   |    |  |

|----------------------|-----------------|-----------------------------------|----|---|---|----|--|

|                      |                 | V <sub>AI</sub> = V <sub>SS</sub> | _1 | - | _ | μA |  |

No. 3653-9/24

# Comparator

$V_{\text{DD}}$  = 5.0 V ±10%,  $V_{\text{SS}}$  = 0 V,  $T_{\text{\tiny B}}$  = -40 to 85 deg. C

| Btra-star               | Quehal | Condition                                                                                          |      | Rating |      | Unit |

|-------------------------|--------|----------------------------------------------------------------------------------------------------|------|--------|------|------|

| Parameter               | Symbol | Condition                                                                                          | min  | typ    | max  | UIIX |

| Comparison precision    | VCECON | $AV + = V_{DD},$<br>$AV - = V_{SS}$                                                                |      | ±1     | ±2   | lsb  |

| Threshold voltage       | VTHCON |                                                                                                    | AV - | _      | AV * | V    |

| Input voltage           | VINCON |                                                                                                    | AV - | _      | AV + | V    |

|                         | AV +   |                                                                                                    | AV - | -      | VDD  | v    |

| Input reference voltage | AV ~   |                                                                                                    | Vss  | _      | AV * | v    |

| Comparison time         | tas    | $\frac{1/1 \text{ comparison} = 12 \times t_{cyc}}{(t_{cyc} = 0.92 \text{ to } 12  \mu \text{s})}$ | 11   | -      | 144  | μs   |

|                         | tcc    | 1/2 comparison = $23 \times t_{cyc}$<br>( $t_{cyc}$ = 0.92 to 12 µs)                               | 21   | -      | 276  | μs   |

# INSTRUCTION SET

# Abbreviations

∧ V ∀

| AC                                     | Accumulator              |                          |                                 |

|----------------------------------------|--------------------------|--------------------------|---------------------------------|

| ACt                                    | Accumulator bit t        |                          |                                 |

| CF                                     | Carry flag               |                          |                                 |

| CTL                                    |                          |                          |                                 |

| DP                                     | Control register         |                          |                                 |

| E                                      | Data pointer             |                          |                                 |

|                                        | E register               |                          |                                 |

| bFn                                    | Flag bit n               |                          |                                 |

| GP(DP)                                 | Pseudo port specified b  | y DP                     |                                 |

| $I_0$ to $I_3$                         | Immediate data           |                          |                                 |

| М                                      | Memory                   |                          |                                 |

| M(DP)                                  | Memory addressed by I    |                          |                                 |

| MSTEN                                  | Master interrupt enable  | flag                     |                                 |

| P(DPL)                                 | I/O port specified by D  | PL                       |                                 |

| PĊ                                     | Program counter          |                          |                                 |

| STACK                                  | Stack register           |                          |                                 |

| to, t1                                 | Immediate data which sp  | ecifies the bit within t | he addressed nibble as follows. |

|                                        | •                        | <b>t</b> a               | Bit                             |

|                                        | t1                       | to                       |                                 |

|                                        | 0                        | 0                        | Da                              |

|                                        | 0                        | 1                        | D1                              |

|                                        | 1                        | 0                        | D <sub>2</sub>                  |

|                                        | 1                        | 1                        | D <sub>3</sub>                  |

| bAt, bHa, bLa                          | Working registers        |                          |                                 |

| ZF                                     | Zero flag                | •                        |                                 |

| (),[]                                  | Indicates memory or re   | vister contents          |                                 |

| < ,, , , , , , , , , , , , , , , , , , | Transfer in indicated di |                          |                                 |

| +                                      | Add                      |                          |                                 |

| _                                      | Subtract                 |                          |                                 |

|                                        | JUDUALI                  |                          |                                 |

AND OR XOR

No. 3653----10/24

|          |                                                                                                                                                          |                                                                             |         | _        |            |        |          | Instructi | on code | 8       |         |          |       |       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|----------|------------|--------|----------|-----------|---------|---------|---------|----------|-------|-------|

| Code     | Description                                                                                                                                              | Operation                                                                   | F       | ag       | D7         | D6     | 05       | D4        | D3      | D2      | D1      | DØ       | Bytas | Cycle |

|          | ·                                                                                                                                                        |                                                                             | A       | ະດາພາງອ  | lar        | L      | I        | <u> </u>  |         |         |         | L        | L     | L     |

| CLA      | Clear AC. See note 1.                                                                                                                                    | AC ← 0                                                                      | ZF      | 1        | 1          | 1      | 0        | 0         | 0       | ٥       | 0       | 0        | 1     | 1     |

| CLC      | Clear CF                                                                                                                                                 | CF ← D                                                                      |         | CF       | 1          | 1      | 1        | 0         | 0       | 0       | 0       | 1        | 1     | 1     |

| STC      | Set CF                                                                                                                                                   | CF ← 1                                                                      |         | CF       | 1          | 1      | 1        | 1         | 0       | 0       | 0       | 1        | 1     | 1     |

| CMA      | Complement AC                                                                                                                                            | $AC \leftarrow (\overline{AC})$                                             | ZF      |          | 1          | 1      | 1        | 0         | 1       | 0       | 1       | 1        | t     | 1     |

| INC      | Increment AC                                                                                                                                             | AC ← (AC) + 1                                                               | ZF      | CF       | 0          | 0      | 0        | 0         | 1       | 1       | 1       | 0        | 1     | 1     |

| DEC      | Decrement AC                                                                                                                                             | $AC \leftarrow (\overline{AC}) - 1$                                         | ZF      | CF       | 0          | 0      | ¢        | 0         | 1       | 1       | 1       | 1        | 1     | 1     |

| RAL      | Rotate AC left through CF                                                                                                                                | $AC_0 \leftarrow (CF).AC_n + 1$<br>$\leftarrow (AC_n).CF \leftarrow (AC_3)$ | Z۶      | CF       | ο          | o      | o        | ٥         | D       | 0       | 0       | 1        | 1     | 1     |

| TAE      | Transfer AC to E                                                                                                                                         | E ← (AC)                                                                    |         |          | 0          | a      | a        | 0         | 0       | Ó       | 1       | 1        | 1     | 1     |

| XAE      | Exchange AC with E                                                                                                                                       | (AC) ↔ (E)                                                                  |         |          | 0          | 0      | 0        | 0         | 1       | 1       | ٥       | 1        | 1     | 1     |

|          | · · · · · · · · · · · · ·                                                                                                                                |                                                                             |         | Meman    | ,          |        | <b>L</b> |           |         |         |         | <u> </u> |       |       |

| INM      | Increment M                                                                                                                                              | $M(DP) \leftarrow [M(DP)] + 1$                                              | ZF      | CF       | ٥          | ٥      | 1        | 0         | 1       | 1       | 1       | 0        | 1     | 1     |

| DEM      | Decrement M                                                                                                                                              | M(DP) ← [M(DP)] - 1                                                         | ZF      | CF       | ٥          | 0      | 1        | a         | 1       | 1       | 1       | 1        | 1     | 1     |

| SMB bit  | Set M data bit                                                                                                                                           | M(DP,B1Bc) ← 1                                                              |         |          | ٥          | 0      | C        | ٥         | 1       | 0       | B1      | Ba       | 1     | 1     |

| RM8 bit  | Reset M data bit                                                                                                                                         | M(DP.B1B0) ← 0                                                              | ZF      |          | ٥          | 0      | 1        | 0         | 1       | C       | B1      | BO       | 1     | 1     |

|          | ••••••••••••••••••••••••••••••••••••••                                                                                                                   |                                                                             | Arlthme | tic and  | compar     | 8      |          |           | •       |         |         |          |       |       |

| AD       | Add M to AC                                                                                                                                              | $AC \leftarrow (AC) + [M(DP)]$                                              | ŹF      | CF       | 0          | 1      | 1        | 0         | ٥       | o       | 0       | 0        | 1     | 1     |

| ADC      | Add M to AC with CF                                                                                                                                      | $AC \leftarrow (AC) + [M(DP)]$<br>+ (CF)                                    | ZF      | CF       | ٥          | o      | 1        | 0         | ٥       | ¢       | o       | C        | 1     | 1     |

| DAA      | Decimal adjust AC in addition                                                                                                                            | AC ← (AC) + 6                                                               | ZF      |          | 1          | 1      | 1        | 0         | 0       | 1       | 1       | ٥        | 1     | 1     |

| DAS      | Decimal adjust AC in subtraction                                                                                                                         | $AC \leftarrow (AC) + 10$                                                   | ZF      |          | 1          | 1      | 1        | 0         | 1       | 0       | 1       | 0        | 1     | 1     |

| EXL      | Exclusive OR M with AC                                                                                                                                   | $AC \leftarrow (AC) \forall [M(DP)]$                                        | ZF      |          | 1          | 1      | 1        | 1         | 0       | 1       | 0       | 1        | 1     | 1     |

| AND      | AND M to AC                                                                                                                                              | $AC \leftarrow (AC) \land [M(DP)]$                                          | ZF      | <b> </b> | 1          | 1      | 1        | 0         | ٥       | 1       | 1       | 1        | 1     | 1     |

| OR       | OR M with AC                                                                                                                                             | $AC \leftarrow (AC) \vee [M(DP)]$                                           | ZF      |          | 1          | 1      | 1        | 0         | ٥       | 1       | 0       | 1        | 1     | 1     |

| СМ       | Compare AC with M.<br>See table 1.                                                                                                                       | [M(DP)] + (AC) + 1                                                          | ZF      | CF       | 1          | 1      | 1        | 1         | 1       | 0       | 1       | 1        | 1     | 1     |

| Ci data  | Compare AC with immediate data.<br>See table 2.                                                                                                          | <sup>1</sup> 312 <sup>1</sup> 110 + (AC) + 1                                | ZF      | CF       | 0          | 0<br>1 | 1<br>Q   | 0         | 1<br>13 | 1<br>12 | 0<br> 1 | 0<br>10  | 2     | 2     |

| CLI data | Compare DPL with immediate data                                                                                                                          | (DPL) ∀ i3i2i1i0                                                            | ŻF      |          | 0          | 0      | 1<br>0   | 0         | 1       | 1<br>12 | 0<br> 1 | 0<br>10  | 2     | 2     |

|          |                                                                                                                                                          | r                                                                           | Loa     | d and i  | ators<br>T | ·      | 1        |           |         |         |         | <u> </u> |       | r—    |

| LI data  | Load AC with immediate data.<br>See note 1.                                                                                                              | AC ← 13121110                                                               | ZF      |          | 1          | 1      | 0        | 0         | I3      | 12      | 11      | 10       | 1     | 1     |

| S        | Store AC to M                                                                                                                                            | M(DP) ↔ (AC)                                                                |         | <u> </u> | 0          | 0      | 0        | 0         | 0       | 0       | 1       | C        | 1     | 1     |

| L        | Load AC from M                                                                                                                                           | AC ← [M(DP))                                                                | ZF      |          | 0          | 0      | 1        | 0         | ٥       | ٥       | 0       | 1        | 1     | 1     |

| XM data  | Exchange AC with M, then modify<br>DPH with immediate data. The<br>zero flag is determined by<br>comparing the data pointer high<br>hibble with OM2M1M0. | (AC) [M(DP)]<br>DPH ← (DPH) ∀<br>0M2M1M0                                    | ZF      |          | 1          | a      | 1        | a         | a       | M2      | Mi      | Ma       | 1     | 2     |

| x        | Exchange AC with M. The zero<br>flag is determined by the contents<br>of the data pointer high nibble.                                                   | (AC) harr (M(DP)]                                                           | ZF      |          | 1          | o      | 1        | 0         | ٥       | 0       | o       | C        | 1     | 2     |

| XI       | Exchange AC with M, then<br>increment DPL. The zero flag is<br>determined by the contents of the<br>data pointer low nibble.                             | (AC) ↔[M(DP)]<br>DPL ← (DPL) + 1                                            | ZF      |          | 1          | 1      | 1        | 1         | 1       | 1       | 1       | a        | 1     | 2     |

| xo       | Exchange AC with M, then decre-<br>ment DPL. The zero flag is<br>determined by the low nibble of<br>the data pointer.                                    | (AC) ↔[M(DP)]<br>DPL ← (DPL) – 1                                            | ZF      |          | 1          | 1      | 1        | 1         | 1       | 1       | 1       | 1        | 1     | 2     |

|          | Read table data from program                                                                                                                             | AC.E ↔ROM (PCh.                                                             |         |          | 0          | 1      | 1        | 0         | 0       | C       | 1       | 1        | 1     | 2     |

.

# LC65102A, LC65104A

No. 3653-11/24

| <u>.</u>                        |                                                                                                                                                                                            |                                                                                                                                                                              |          |          |                    |         |         | Instructi | on code | ;           |             |          |             |        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------------|---------|---------|-----------|---------|-------------|-------------|----------|-------------|--------|

| Code                            | Description                                                                                                                                                                                | Operation                                                                                                                                                                    | Fi       | ag       | D7                 | Dő      | 05      | D4        | D3      | D2          | 01          | DO       | Bytes       | Cycles |

|                                 | L                                                                                                                                                                                          | LD                                                                                                                                                                           | ata poli | nter ma  | nipul <b>a</b> tio |         |         |           |         |             |             |          |             |        |

| LDZ data                        | Load DPH with zero and DPL with immediate data, respectively.                                                                                                                              | DPH ← 0<br>DPL ← 13121110                                                                                                                                                    |          |          | 1                  | 0       | 0       | 0         | 13      | 12          | 11          | 10       | 1           | 1      |

| LHI data                        | Load DPR with immediate data                                                                                                                                                               | DPH ← 13121110                                                                                                                                                               |          |          | 0                  | 1       | 0       | 0         | 13      | 12          | 11          | 10       | 1           | 1      |

| IND                             | increment DPL                                                                                                                                                                              | DPL ← (DPL) + 1                                                                                                                                                              | ZF       |          | 1                  | 1       | 1       | 0         | 1       | 1           | 1           | 0        | 1           | 1      |

| DED                             | Decrement DPL                                                                                                                                                                              | DPL ← (DPL) ⊷ 1                                                                                                                                                              | ZF       |          | 1                  | 1       | 1       | 0         | 1       | 1           | 1           | 1        | 1           | 1      |

| TAL                             | Transfer AC to DPL                                                                                                                                                                         | $DP_L \leftarrow (AC)$                                                                                                                                                       |          |          | 1                  | 1       | 1       | 1         | 0       | 1           | 1           | 1        | 1           | 1      |

| TLA                             | Transfer DPL to AC                                                                                                                                                                         | $(AC) \leftarrow (DP_L)$                                                                                                                                                     | ZF       |          | 1                  | 1       | -       | 0         | 1       | 0           | 0           | 1        | 1           | 1      |

| ХАН                             | Exchange AC with DPR                                                                                                                                                                       | (AC) ↔(DPH)                                                                                                                                                                  |          |          | 0                  | 0       | 1       | 0         | 0       | Û           | 1           | 1        | 1           | 1      |

|                                 |                                                                                                                                                                                            |                                                                                                                                                                              | War      | ding reg | lster              |         |         |           |         | _           |             |          |             |        |

| XAt<br>XAO<br>XA1<br>XA2<br>XA3 | Exchange AC with working register<br>bAt                                                                                                                                                   | $\begin{array}{rcl} (AC) & \leftrightarrow(bA0) \\ (AC) & \leftrightarrow(bA1) \\ (AC) & \leftrightarrow(bA2) \\ (AC) & \leftrightarrow(bA3) \end{array}$                    |          |          | • • • 1            | 1 1 1 1 | 1 1 1   | 0000      | 50011   | 20101       | 0<br>0<br>0 | 0000     | 1<br>1<br>1 | 1 1 1  |

| XHa<br>XHO<br>XH1               | Exchange DPH with working register bHa                                                                                                                                                     | (DPH) ↔(bH0)<br>(DPH) ↔(bH1)                                                                                                                                                 |          |          | 1                  | 1       | 1       | 1         | 1       | a<br>0<br>1 | 0           | 0        | 1           | 1      |

| XLa<br>XLO<br>XL1               | Exchange DPL with working<br>register bLa                                                                                                                                                  | (DPL) ↔(bL0)<br>(DPL) ↔(bL1)                                                                                                                                                 |          |          | 1                  | 1       | 1       | 1         | o<br>Ç  | a<br>C<br>1 | 0           | 00       | 1           | 1      |

| SRBA                            | Set register bank address                                                                                                                                                                  | RBF ← Isin of SB                                                                                                                                                             |          |          | 1                  | 1       | 1       | 1         | C       | 0           | 1           | ٥        | 1           | 1      |

|                                 | I                                                                                                                                                                                          | 1                                                                                                                                                                            | Bit      | manipul  | ation              |         |         |           |         |             |             |          |             |        |

| SF8 flag                        | Set flag bit                                                                                                                                                                               | bFn ← 1                                                                                                                                                                      |          |          | 0                  | 1       | 0       | 1         | 83      | B2          | B1          | Bo       | 1           | 1      |

| RFB flag                        | Clear flag bit. The flags are orga-<br>nized in 16 $\times$ 4-bit nibbles from<br>OFOH to OF3H to 3FCH to 3FCH.<br>The zero flag is determined by the<br>contants of the specified nibble. | bFn ← O                                                                                                                                                                      | Zf       |          | O                  | 0       | O       | 1         | 83      | 82          | B1          | 80       | 1           | 1      |

|                                 |                                                                                                                                                                                            | <b>I</b> ·                                                                                                                                                                   | Jump     | and sul  | routine            |         |         |           |         |             |             |          |             |        |

| JMP addr                        | Jump in the current bank. The<br>bank changes when a JMP<br>instruction is followed by a BANK<br>instruction.                                                                              | PC ← PC11 (or PC11)<br>P10P9P8P7<br>P10P10P10P3 P2P1P0                                                                                                                       |          |          | 0<br>P7            | 1<br>P6 | 1<br>P5 | 0<br>P4   | 1<br>P3 | P10<br>P2   | Pg<br>P1    | Pa<br>Po | 2           | 2      |

| JPEA                            | Jump in the current page modified by E and AC                                                                                                                                              | PC7 to 0 $\leftarrow$ (E.AC)                                                                                                                                                 |          |          | 1                  | 1       | 1       | 1         | 1       | 0           | 1           | 0        | 1           | 1      |

| CZP addr                        | Call subroutine in the zero page                                                                                                                                                           | $\begin{array}{l} \text{STACK} \leftarrow (\text{PC}) + 1 \\ \text{PC11 to 6,} \\ \text{PC1 to 0} \leftarrow 0 \\ \text{PC5 to 2} \leftarrow \\ \text{P3P2P1P0} \end{array}$ |          |          | 1                  | 0       | 1       | 1         | Рэ      | P2          | P1          | Po       | 1           | \$     |

| CAL addr                        | Call subroutine in the zero bank                                                                                                                                                           | $\begin{array}{rcl} \text{STACK} \leftarrow (\text{PC}) + 2 \\ \text{PC11} & \text{10} & 0 \leftarrow 00 \\ \text{P10P9P8P7} & \text{P6P5P4P3} \\ \text{P2P1P0} \end{array}$ |          |          | 1<br>P7            | 0<br>P6 | 1<br>P5 | 0<br>P4   | 1<br>P3 | P10<br>P2   | Р0<br>Р1    | P8<br>P0 | 2           | 2      |

| RT                              | Return from subroutine                                                                                                                                                                     | PC ← (STACK)                                                                                                                                                                 |          |          | 0                  | 1       | 1       | 0         | 0       | O           | 1           | ٥        | 1           | 1      |

| RTI                             | Return from interrupt routine                                                                                                                                                              | PC ← (STACK)<br>CF ZF ← CSF.ZSF                                                                                                                                              | ZF       | CF       | 0                  | 0       | 1       | o         | 0       | O           | 1           | 0        | 1           | 1      |

| BANK                            | Change bank                                                                                                                                                                                | PC11 ← (PC11)<br>GP(DP)                                                                                                                                                      |          |          | 1                  | 1       | 1       | 1         | 1       | 1           | 0           | 1        | 1           | 1      |

| \$ <del>8</del>                 | Set bank                                                                                                                                                                                   | RBF ← 1110                                                                                                                                                                   |          |          | O                  | 1       | 1       | 0         | 0       | 1           | 11          | IQ       | 1           | 1      |

|                                 |                                                                                                                                                                                            |                                                                                                                                                                              | -        | Branch   |                    |         |         |           |         |             |             |          |             |        |

| BAt addr                        | Branch on AC bit. Immediate data<br>to and t1 is appended to BA,<br>which is followed by the program<br>counter branch address P0 to P7.                                                   | PC7 to 0 ←<br>P7P6P5P4 P3P2P1P0 if<br>ACt = 1                                                                                                                                |          |          | 0<br>P7            | 1<br>P6 | 1<br>P5 | 1<br>P4   | 0<br>P3 | 0<br>P2     | tı<br>P1    | to<br>Po | 2           | 2      |

| BNA1 addr                       | Branch on no AC bit. Immediate<br>data to and t1 is appended to<br>BNA, which is followed by the<br>program counter branch address<br>Po to P7.                                            | PC7 to 0 ←<br>P7P6P5P4 P3P2P1P0 if<br>ACt = 0                                                                                                                                |          |          | 0<br>P7            | 0<br>P6 | 1<br>P5 | 1<br>P4   | 0<br>P3 | 0<br>P2     | tı<br>Pı    | to<br>Po | 2           | 2      |

No. 3653—12/24

| • •                  |                                                                                                                                                           |                                                                                                                                               |    |          |         |         |                     | instructi | an codi  |           |          |          | D-4   | Outra  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|----------|---------|---------|---------------------|-----------|----------|-----------|----------|----------|-------|--------|

| Cade                 | Description                                                                                                                                               | Operation                                                                                                                                     | Fl | ag       | D7      | 06      | 05                  | D4        | D3       | 02        | D1       | DO       | Bytes | Cycles |

| BMt addr             | Branch on M bit. Immediate data<br>10 and 11 is appended to BM,<br>which is followed by the program<br>counter branch address P0 to P7.                   | PC7 to 0 ←<br>P7P6P5P4 P3P2P1P0 it<br>[M(OP.t1t0)] = 1                                                                                        |    |          | 0<br>P7 | 1<br>P6 | 1<br>P5             | 1<br>P4   | 0<br>Рз  | 1<br>P2   | tı<br>Pı | 9 C      | . 2   | 2      |