# SEMICONDUCTOR TECHNICAL DATA

# KIA8225H

#### BIPOLAR LINEAR INTEGRATED CIRCUIT

### 45W BTL SINGLE AUDIO POWER AMPLIFIER

The KIA8225H is BTL audio power amplifier for consumber application.

It is designed for high power, low distortion and low noise. It contains various kind protectors and the function of stand-by SW.

In addition, the functions of output short or over voltage detection and junction temperature are involved.

#### **FEATURES**

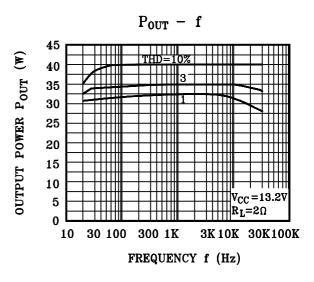

- · High Power

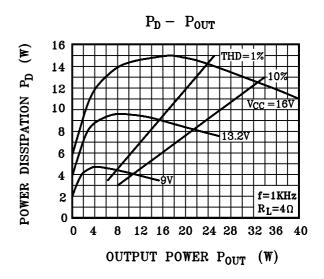

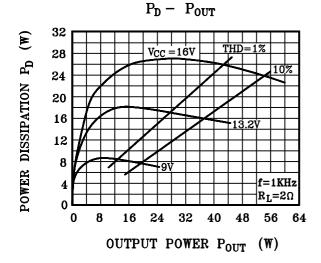

- $: P_{OUT}(1)=45W(Typ.)$

(Vcc=14.4V, f=1kHz, THD=10%,  $R_L=2\Omega$ )

:  $P_{OUT}(2)=40W(Typ.)$

(Vcc=13.2V, f=1kHz, THD=10%,  $R_L=2\Omega$ )

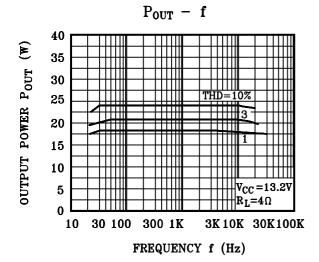

:  $P_{OUT}(3)=24W(Typ.)$

(Vcc=13.2V, f=1kHz, THD=10%,  $R_L$ =4 $\Omega$ )

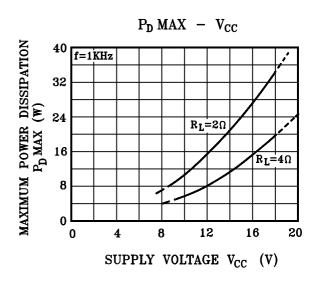

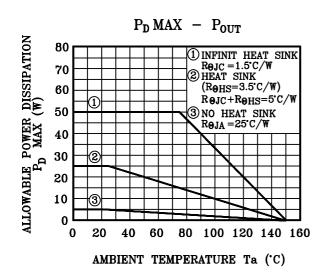

- · Low Thermal Resistance

- :  $\theta_{\rm j-c}$ =1.5°C/W (Infinite Heat Sink)

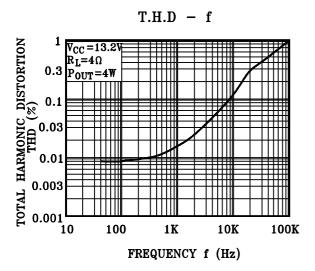

- · Excellent Output Power Band Width

- :  $P_{OUT(4)}=18W(Typ.)$

$(Vcc=13.2V, f=50Hz\sim20kHz, THD=1\%, R_L=4\Omega)$

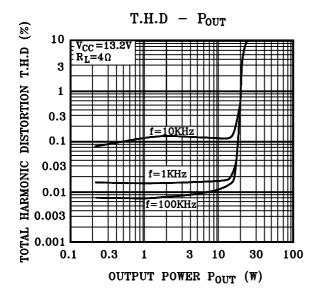

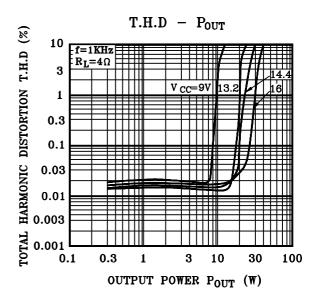

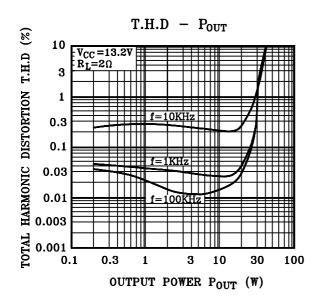

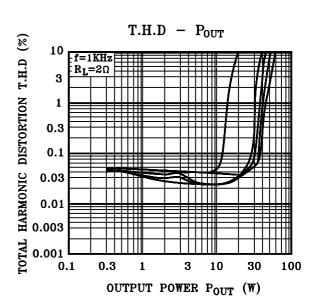

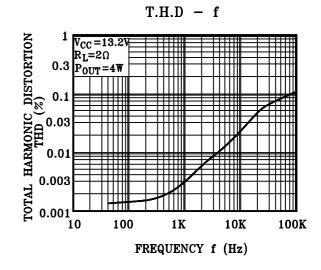

- · Low Distortion Ratio

- : THD=0.015%(Typ.) Z

(Vcc=13.2V, f=1kHz, Pout=4W,  $R_L$ =4 $\Omega$ )

- Built-in stand-by function (With Pin2) set at high, power is turned ON)

- \* Built-in Output Short or Over Voltage Detection Circuit, Output to  $V_{CC}$  and Output to GND Short. (Pin& : Open Collector)

- Built-in Junction Temperature Detection Circuit (Pin2:Open Collector)

- · Built-in various protection circuit.

- : Thermal shut down, over voltage,

- : Output to GND Short

- : Output to  $V_{\text{CC}}$  Short

- : Output to Output Short.

- Operating supply voltage. : V<sub>CC(opr)</sub>=9~18V.

# MILLIMETERS 36.00±0.20 $14.00 \pm 0.20$ 4.95±0.20 2.00 10.00± 0.30 0.40 + 0.10 $5.00 \pm 0.30$ 17.00±0.30 1.20±0.10 0 2.00 2.00±0.30 R1.8 3.82±0.30 30.00± 0.20 CPP-17

## MAXIMUM RATINGS (Ta=25°C)

| CHARACTERISTIC               | SYMBOL                  | RATING  | UNIT |

|------------------------------|-------------------------|---------|------|

| Peak Supply Voltage (0.2sec) | V <sub>CC</sub> (surge) | 50      | V    |

| DC Supply Voltage            | V <sub>CC</sub> (DC)    | 25      | V    |

| Operating Supply Voltage     | V <sub>CC</sub> (opr)   | 18      | V    |

| Output Current (Peak)        | I <sub>O (peak)</sub>   | 9       | A    |

| Power Dissipation            | P <sub>D</sub> *        | 50      | W    |

| Operating Temperature        | $T_{\mathrm{opr}}$      | -30~85  | °C   |

| Storage Temperature          | $T_{\mathrm{stg}}$      | -55~150 | °C   |

## ELECTRICAL CHARACTERISTICS

(Unless otherwise specified, Vcc=13.2V,  $R_L$ =4 $\Omega$ , f=1kHz, Ta=25 $^{\circ}$ C)

| CHARACTERISTIC                     | SYMBOL               | TEST<br>CIRCUIT | TEST CONDITION                                                            | MIN. | TYP.  | MAX. | UNIT |  |

|------------------------------------|----------------------|-----------------|---------------------------------------------------------------------------|------|-------|------|------|--|

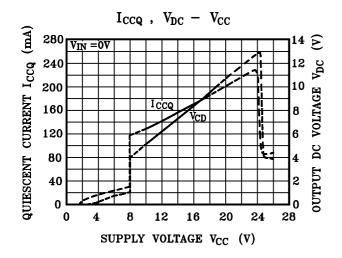

| Quiescent Current                  | $I_{CCQ}$            | -               | $V_{IN}=0$                                                                | -    | 150   | 250  | mA   |  |

| Output Power                       | P <sub>OUT</sub> (1) | _               | $V_{\text{CC}}$ =14.4V, THD=10% $R_{\text{L}}$ =2 $\Omega$                |      | 45    | -    | W    |  |

|                                    | Pout(2)              | _               | $V_{CC}$ =13.7V, MAX power                                                | 33   | 40    | -    |      |  |

|                                    | P <sub>OUT</sub> (3) | -               | $V_{CC}=14.4V$ , THD=10%                                                  | 20   | 24    | -    | "    |  |

|                                    | P <sub>OUT</sub> (4) | -               | THD=10%                                                                   | -    | 18    | -    |      |  |

| Total Harmonic<br>Distortion Ratio | THD                  | -               | P <sub>OUT</sub> =3W                                                      | _    | 0.015 | 0.07 | %    |  |

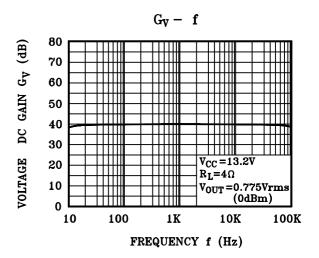

| Voltage Gain                       | Gv                   | _               | $V_{OUT}\text{=}0.775V_{rms}~(0dBm)$                                      | 38.5 | 40    | 41.5 | dB   |  |

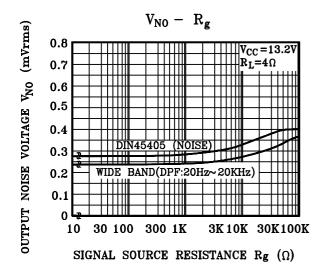

| Output Noise Voltage               | V <sub>NO</sub> (1)  | -               | Rg=0Ω, DIN45405                                                           | -    | 0.26  | _    | dB   |  |

|                                    | $V_{NO}$ (2)         | _               | Rg=0Ω, BW=20Hz~20kHz                                                      | -    | 0.23  | 0.5  |      |  |

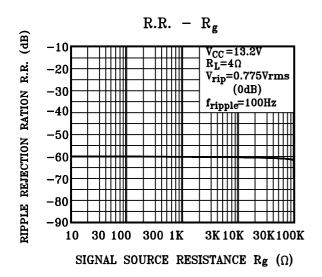

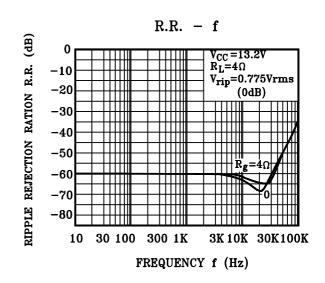

| Ripple Rejection Ratio             | R.R.                 | =               | $f_{ripple}$ =100Hz, Rg=620 $\Omega$<br>$V_{rio}$ =0.775 $V_{rms}$ (0dBm) | 50   | 60    | -    | mV   |  |

| Output Offset Voltage              | Voffset              | -               | -                                                                         | -100 | 0     | 100  | μΑ   |  |

| Current at Stan-By State           | $I_{\mathrm{SB}}$    | _               | Mute:on, V <sub>OUT</sub> =7.75V <sub>rms</sub> (20dBm) at Mute:off       | _    | 1     | 30   | dB   |  |

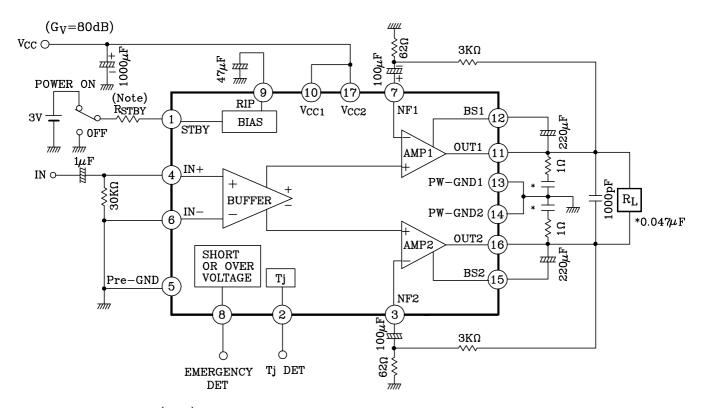

## TEST CIRCUUT & BLOCK DIAGRAM

(Note) The purpose of  $\ensuremath{R_{\,\text{STBY}}}$  is current limiting resistance.

#### CAUTION AND APPLICATION METHOD OF APPLICATION

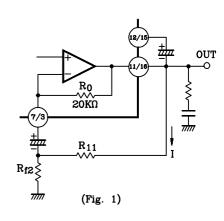

### 1. Voltage gain adjustment

Voltage gain  $G_V$  of this IC is decided by the external feedback resistors  $R_{\rm fl}$  and  $R_{\rm f2}$ .

Gain fluctuation by temperature can be made smaller than they are housed in IC.

votage gain G<sub>V</sub> is decided by the following expression:

$$\begin{split} &\text{If } R_0 = 20 \text{k} \, \Omega \gg R_{f1} > R_{f2} & G_V = 20 \log \frac{R_{f1} - R_{f2}}{R_{f2}} + 6 \text{(dB)} \\ &\text{If } R_0 = 20 \text{k} \, \Omega > R_{f1} > R_{f2} & G_V = 20 \log \frac{(R_0 / / R_{f1}) + R_{f2}}{R_{f2}} + 6 \text{(dB)} \end{split}$$

If  $R_{f1}$  and  $R_{f2}$  are made small, the following problems may be caused :

- (1) When output short is released, output DC voltage is not restored.

- (2) Fluctuation of output DC voltage by current I in (Fig1.)

If voltage gain is made small excessively, oscillation may be taken place and therefore, this IC shall be used at  $G_V$ =34dB or above.

#### 2. Preventive measure against oscillation

For preventing the oscillation, it is advisable to use C<sub>4</sub>, the condenser of polyester film having small characteristic fluctuation of the temperature and the frequency.

the condenser (C<sub>6</sub>) between input and GND is effective for preventing oscillation which is generated with feedback signal from an output stage.

The resistance R to be series applied to  $C_4$  is effective for phase correction of high frequency, and improves the oscillation allowance.

Since the oscillation allowance is varied according to the causes described below, perform the temperature test to check the oscillation allowance.

- (1) Voltage gain to be used (G<sub>V</sub> Setting)

- (2) Capacity value of condenser

(3) Kind of condenser

(4) Layout of printed board

In case of its use with the voltage gain  $G_V$  reduced or with the feedback amount increased, care must be taken because the phase-inversion is caused by the high frequency resulting in making the oscillation liable generated.

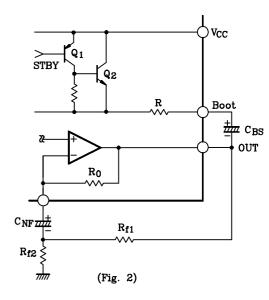

### 3. Pop Noise

A pop noise generated when the power source is turned ON depends on rise times of the in-phase side output (@pin) and the negative-phase side output offset voltage.

The following two points may be pointed out as causes for generation the output offset voltage:

- (1) In-phase and negative-phase NF capacitor charging time.

- (2) Input offset voltage.

Especially, the factor(2) relates to the pop noise level.

### (1) In-phase and negative phase NF capacitor charging time

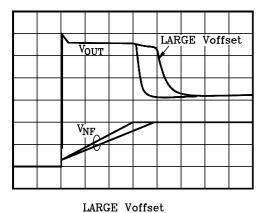

In (Fig2.), when the power source is turned ON,  $Q_1$  and  $Q_2$  are turned ON, and NF capacitors are charged in the route of VCC $\rightarrow$ Q2 $\rightarrow$ R $\rightarrow$ Boot $\rightarrow$ CBS $\rightarrow$ OUT $\rightarrow$ RO $\rightarrow$ CNF. For instance, if the capacity of an in-phase capacitor is not produced because a charging time of NF capacitor differs between the in-phase and negative-phase outputs. Therefore, to suppress the pop noise it is necessary to properly pair the in-phase and negative-phase NF capacitors. Output and NF DC voltage waveforms by the pairing of NF capacitors:  $C_{NF}$  are shown in (Fig.3) and (Fig.4).

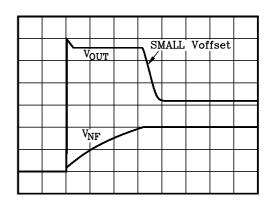

Further, voltage waveforms are shown when the power source was turned ON, under the following conditions:  $V_{CC}=13.2V$ ,  $R_L=4\Omega$ ,  $Ta=25^{\circ}C$ , and input shot-circuit.

Output DC Voltage  $V_{OUT}$ : (2V/div, 200ms/div) NF DC Voltage  $V_{NF}$ : (1V/div, 200ms/div)

LANGE VOIISEC

(When C<sub>NF</sub> are improperly paired)

(Fig.3)

SMALL Voffset

(When  $C_{NF}$  are properly paired) (Fig.4)

#### (2) Input offset voltage

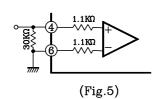

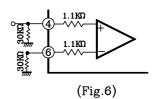

Injut offset voltage is increased by as many times as a gain and appears as output offset voltage. Input offset voltage is affected by an external resistor in addition to properness of pair of Capacitor in IC. An example of a general application circuit is shown in (Fig.5). In this case, input to the differential amplifier composing the buffer amplifier is decided to be  $30k\Omega+1.1k\Omega=31.1k\Omega$  at the IN(+) side and 1.1k at the IN(-) side. Therefore a rising difference of about 30 times between the IN(+) side and the IN(-) side. So, to fit input offset voltages, it is possible to suppress the input offset voltage by adjusting it to  $31.1k\Omega$  both at the IN(+) and IN(-) sides according to the application example shown in (Fig.6). As input coupling capacitors are used in actual set, the circuit shown in (Fig.7) is considered. In this case, it is necessary to take the utmost care of proper pair of  $C_{IN}(+)$  and  $C_{IN}(-)$ .

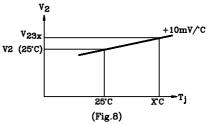

4. Junction temperature detecting pin ②

Using temperature characteristic of a band gap circuit and in proportion to junction temperature, pin ② DC voltage:  $V_2$  rises at about  $\pm 10 \text{mV/C}$  temperature characteristic. So, the relation between  $V_2$  at  $T_j=25 \text{°C}$  and  $V_2 \chi$  at  $T_j=\chi$  °C is decided by the following expression:

$$T(\chi ^{\circ}) = \frac{V_2 \chi - V_2(25^{\circ})}{10 \text{mV/}^{\circ}} + 25(^{\circ})$$

In deciding a heat sink size, a junction temperature can be easily made clear by measuring voltage at this pin while a backside temperature of IC was so far measured using a thermocouple type thermometer.

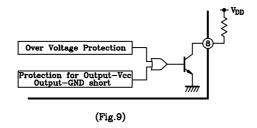

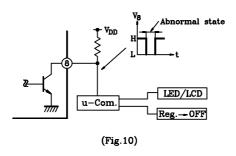

5. Output-V<sub>CC</sub> short, output-GND short and over voltage detecting pin **8**In case of such abnormalities as output-V<sub>CC</sub> short, output-GND short, overvoltage (Fig.9), it is possible to inform the abnormal state to the outside by turning a NPN transistor is turned ON.

It is possible to improve the reliability of not only power IC but also an entire equipment by (1) display by LED and LCD and (2) by turning the power supply relay off.

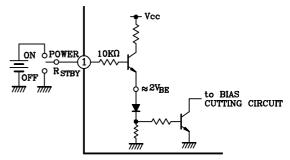

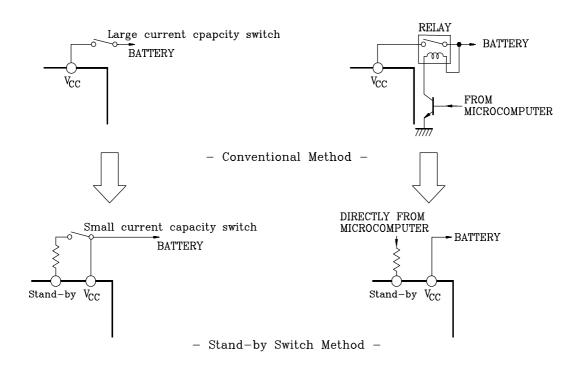

6. Stand-by SW function

By means of controlling pin 1 (Stand-by terminal) to High and Low, the power supply can be set to ON and OFF.

the threshold voltage of pin 1 is set at about  $3V_{BE} = 2.1V(Typ.)$ , and the power supply current is about  $1\mu A(Typ.)$  at the stand-by state.

Control Voltage of ① pin: V(SB)

| Stand-By | Power | $V_{(SB)}$ (V)    |

|----------|-------|-------------------|

| ON       | OFF   | 0~2               |

| OFF      | ON    | 3∼V <sub>CC</sub> |

(Fig.11) with pin ① set to high, power is truned ON.

### <Caution>

Must be set the control voltage value less than VCC when the stand-by terminal (pin①) is applied. In this case, we recommended the series connecting resistance for current limit :  $R_{STBY}$  (100k $\Omega \sim 1 k \Omega$  to pin ①)

8/9