# **Data Sheet**

# gmFC1

DAT-0005-D

November 1998

Genesis Microchip Inc.

200 Town Centre Blvd, Suite 400, Markham, ON Canada L3R 8G5 Tel: (905) 470-2742 Fax: (905) 470-9022 2071 Landings Drive, Mountain View, CA, USA 94043 Tel: (650) 428-4277 Fax (650) 428-4288 www.genesis-video.com / info@genesis-microchip.on.ca

# gmFC1 Data Sheet

#### DAT-0005-D

| Document | Revision | Incorporated Errata / Details                                                                                                                                                                                                                                                                                                                                           | Release<br>Date |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| DAT-0005 | А        | First Release Nov. 199                                                                                                                                                                                                                                                                                                                                                  |                 |

| DAT-0005 | В        | Minor update for CD-ROM                                                                                                                                                                                                                                                                                                                                                 | Dec. 1997       |

| DAT-0005 | С        | MSD-0025-A details major changes                                                                                                                                                                                                                                                                                                                                        | March 1998      |

| DAT-0005 | D        | <ol> <li>64MB memory device interface as in MSD-<br/>0038</li> <li>Electrical Specifications finalized</li> <li>Errata E04-0005, E05-0005 incorporated</li> <li>I/O pads incorporate pull-down resistors as in<br/>MSD-0028</li> <li>Various corrections and clarifications</li> <li>Order Code changed to BR1C</li> <li>Extended Temp. range part available</li> </ol> | Nov. 1998       |

#### Copyright 1998, Genesis Microchip Inc. All Rights Reserved

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without notice. It is the customer's responsibility to ensure he/she has the most recent revision of the document. Genesis Microchip Inc. makes no warranty for the use of its products and bears no responsibility for any errors or omissions which may appear in this document.

# CONTENTS

| 1. | OVER             | RVIEW                                                               | 1  |

|----|------------------|---------------------------------------------------------------------|----|

| 2. | FEAT             | URES AND APPLICATIONS                                               |    |

| 2  | CENE             | CRAL OPERATION                                                      | -  |

| 3. |                  |                                                                     |    |

|    | 3.1 Typ          | PICAL SYSTEMS                                                       | 6  |

| 4. | PINO             | U <b>T</b>                                                          | 7  |

|    | 4.1 GMI          | FC1 PINOUT- CHIP DIAGRAM                                            | 7  |

|    |                  | FC1 Pinout- Pin List                                                |    |

| 5. | FUNC             | TIONAL DESCRIPTION                                                  | 15 |

|    |                  | ver On Reset                                                        |    |

|    |                  | ver on reset                                                        |    |

|    | 5.2.1            | RGB Graphics Input Modes                                            |    |

|    | 5.2.2            | YUV Video Input Modes                                               |    |

|    | 5.2.3            | Input Active Window Control                                         |    |

|    | 5.2.4            | Input Synchronization                                               |    |

|    | 5.2.5            | Freeze Frame                                                        |    |

|    |                  | APHICS (RGB) INPUT PORT SIGNALS                                     |    |

|    |                  | EO (YUV) INPUT PORT SIGNALS                                         |    |

|    |                  | APHICS / VIDEO COMMON PORT SIGNALS                                  |    |

|    |                  | га Оитрит                                                           |    |

|    | 5.6.1            | Output Formats                                                      | 27 |

|    | 5.6.2            | Output Interface Overview                                           |    |

|    | 5.6.3            | Output Active Size                                                  | 29 |

|    | 5.6.4            | Output Synchronization                                              |    |

|    | 5.6.5            | Reverse Scanning                                                    | 31 |

|    | 5.6.6            | Bypass Mode                                                         |    |

|    | 5.6.7            | Frame Lock Mode                                                     |    |

|    | 5.6.8            | Output Signals                                                      |    |

|    |                  | ME STORE REQUIREMENTS                                               |    |

|    | 5.7.1            | Interface Overview                                                  |    |

|    | 5.7.2            | Constraints on I/O Data Rates                                       |    |

|    | 5.7.3            | Frame Store Clock Frequency and Various Data Formats                |    |

|    | 5.7.4            | SDRAM Power On                                                      |    |

|    | 5.7.5            | Clearing SDRAM                                                      |    |

|    | 5.7.6            | SDRAM Power Down                                                    |    |

|    | 5.7.7            | Supported SDRAM Devices                                             |    |

|    | 5.7.8            | Frame Store Signals                                                 |    |

|    |                  | ST INTERFACE REQUIREMENTS                                           |    |

|    | 5.8.1            | Interface Overview                                                  |    |

|    | 5.8.2            | Updating Register Contents                                          |    |

|    | 5.9 SPI<br>5.9.1 | HOST INTERFACE PROTOCOL REQUIREMENTS                                |    |

|    | 5.9.1<br>5.9.2   | 3-Wire Configuration                                                |    |

|    | 5.9.2<br>5.9.3   | 5-wire Configuration                                                |    |

|    | 5.9.3<br>5.9.4   | <i>4-wire Configuration</i><br>SPI Host Interface State Description |    |

|    | 5.9.4<br>5.9.5   | Host Interface Protocol                                             |    |

|    | 5.7.5            | 11051 Interjuce 1 1010c01                                           |    |

|    | 5.9.6    | Typical Usage Scenarios             |    |

|----|----------|-------------------------------------|----|

|    | 5.9.7    | Host Interface Registers            |    |

| 6. | ELECT    | <b>FRICAL SPECIFICATIONS</b>        | 64 |

|    | 6.1 Prei | LIMINARY DC CHARACTERISTICS         |    |

|    | 6.2 Prei | LIMINARY AC CHARACTERISTICS         |    |

|    | 6.2.1    | Input Port Timing                   |    |

|    | 6.2.2    | Output Port Timing                  |    |

|    | 6.2.3    | Frame Store Interface Timing        |    |

|    | 6.2.4    | Host Interface Timing               |    |

|    | 6.3 Prei | LIMINARY INPUT SETUP AND HOLD TIMES |    |

|    | 6.3.1    | YUV Video Input Interface           |    |

|    | 6.3.2    | RGB Graphics Input Interface        |    |

|    | 6.3.3    | Frame Store Interface               |    |

|    | 6.3.4    | Output (gmZ1/2/3) Interface         |    |

|    | 6.3.5    | Host Interface                      |    |

|    | 6.4 Prei | LIMINARY OUTPUT PROPAGATION DELAYS  | 71 |

|    | 6.4.1    | RGB Graphics Input Interface        |    |

|    | 6.4.2    | Frame Store Interface               |    |

|    | 6.4.3    | Output (gmZ1/2/3) Interface         |    |

|    | 6.4.4    | Host Interface                      |    |

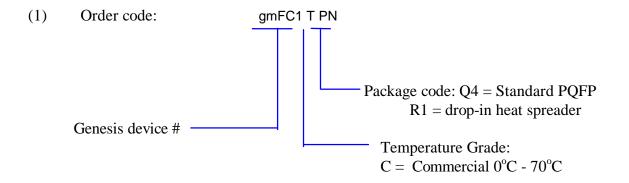

| 7. | ORDE     | RING INFORMATION                    | 74 |

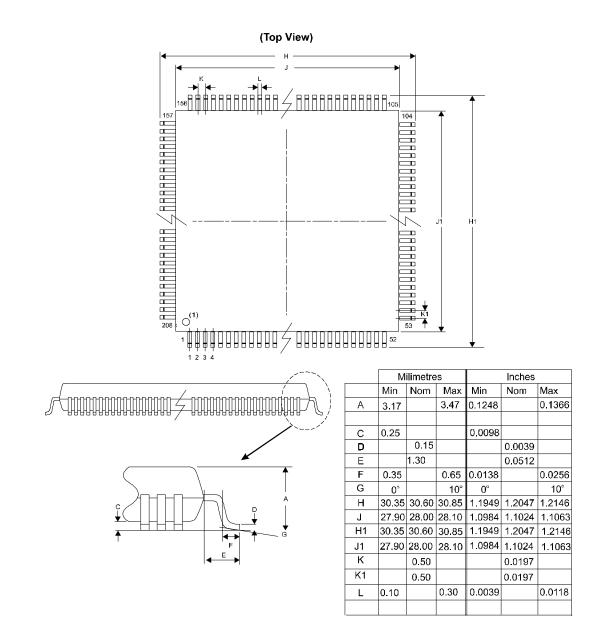

| 8. | MECH     | ANICAL SPECIFICATIONS               | 75 |

| 9. | INTER    | FACING THE GMZ1 AND GMFC1           |    |

# LIST OF TABLES

| TABLE 1: GMFC1 PINOUT DESCRIPTION                            | 8  |

|--------------------------------------------------------------|----|

| TABLE 2: GRAPHICS INPUT MODES                                | 16 |

| TABLE 3: CORRESPONDING INPUT/OUTPUT SIGNALS IN BYPASS MODE   | 31 |

| TABLE 4: FRAME STORE CLOCK REQUIREMENTS                      | 36 |

| TABLE 5: HOST INTERFACE REGISTERS                            |    |

| TABLE 6: ABSOLUTE MAXIMUM RATINGS                            | 64 |

| TABLE 7: DC CHARACTERISTICS                                  | 65 |

| TABLE 8: OUTPUT DRIVE CAPABILITY / INPUT TOLERANCE           | 66 |

| TABLE 9: YUV INPUT INTERFACE SETUP/HOLD TIMES                | 69 |

| TABLE 10: RGB INPUT INTERFACE SETUP/HOLD TIMES               | 69 |

| Table 11: Frame Store Interface Setup/Hold Times             | 70 |

| TABLE 12: OUTPUT INTERFACE SETUP/HOLD TIMES                  |    |

| TABLE 13: HOST INTERFACE SETUP/HOLD TIMES                    |    |

| TABLE 14: RGB INPUT INTERFACE DATA PROPAGATION TIMES         | 72 |

| TABLE 15: FRAME STORE INTERFACE DATA PROPAGATION TIMES       | 72 |

| TABLE 16: OUTPUT (GMZ1/2/3) INTERFACE DATA PROPAGATION TIMES | 73 |

| TABLE 17: HOST INTERFACE DATA PROPAGATION TIMES              | 73 |

# LIST OF FIGURES

| FIGURE 1. GMFC1 - OVERLAPPING CIRCULAR BUFFERS              | 1  |

|-------------------------------------------------------------|----|

| FIGURE 2: GMFC1 FUNCTIONAL BLOCK DIAGRAM                    | 2  |

| FIGURE 3. FRAME RATE CONVERSION PROCESS                     | 5  |

| FIGURE 4: TYPICAL GMFC1 IMPLEMENTATION                      | 6  |

| FIGURE 5: GMFC1 PINOUT                                      | 7  |

| FIGURE 6. GMFC1 INPUT MULTIPLEXER                           | 16 |

| FIGURE 7: XGA VERTICAL INTERLACE MODE FIELD DETECTION       | 17 |

| FIGURE 8: INPUT DATA SAMPLING WINDOW                        | 18 |

| FIGURE 9: GRAPHICS INPUT DATA HANDSHAKING                   | 19 |

| FIGURE 10: GRAPHICS HORIZONTAL SYNC. INPUTS                 | 20 |

| FIGURE 11. CLAMP SIGNAL                                     | 24 |

| FIGURE 12. VIDEO INPUT DATA HANDSHAKING                     | 25 |

| FIGURE 13: VERTICAL DE-INTERLACING                          | 27 |

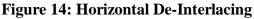

| FIGURE 14: HORIZONTAL DE-INTERLACING                        | 27 |

| FIGURE 15: OUTPUT TIMING (TO GMZ1/2/3)                      | 28 |

| FIGURE 16: GMFC1 - GMZ1/2/3 INTERFACE                       | 29 |

| FIGURE 17: OUTPUT SUB-REGION OF CAPTURED INPUT IMAGE        | 30 |

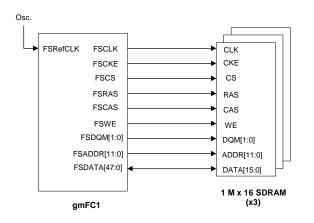

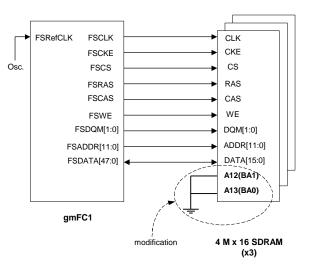

| FIGURE 18. FRAME STORE INTERFACE TO SDRAM                   | 34 |

| FIGURE 19: 4M x 16-bit Frame Store Interface                | 37 |

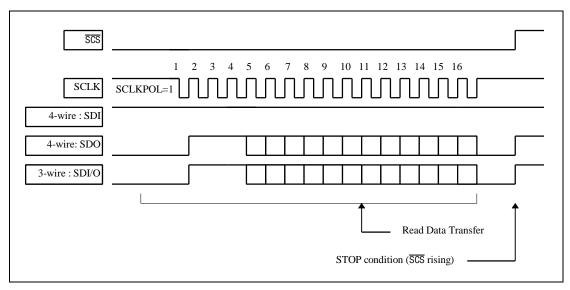

| FIGURE 20: SCLKPOL AND MSBFIRST CONFIGURATION               |    |

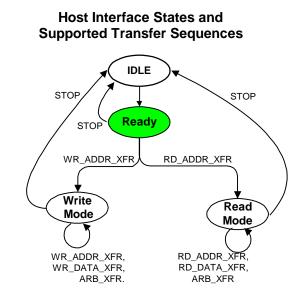

| FIGURE 21: HOST INTERFACE OPERATING STATES                  | 43 |

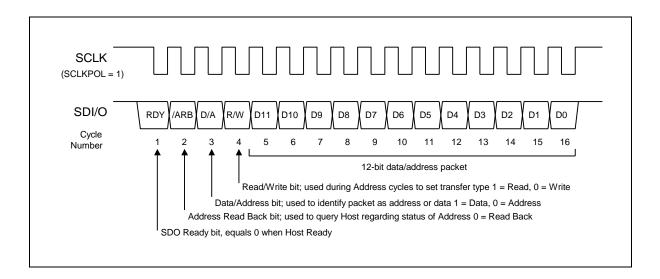

| FIGURE 22: HOST INTERFACE PROTOCOL                          | 44 |

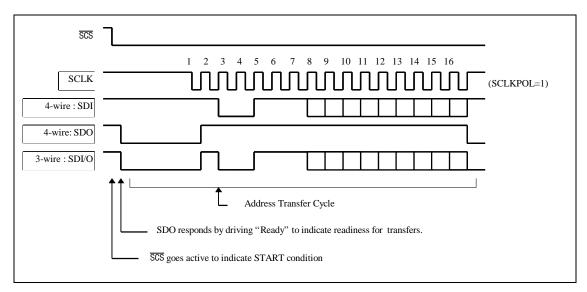

| FIGURE 23: HOST INTERFACE START CYCLE (FOLLOWED BY ADDRESS) |    |

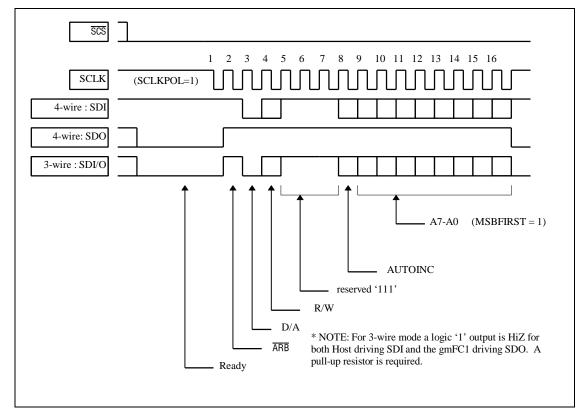

| FIGURE 24: HOST INTERFACE ADDRESS TRANSFER                  | 47 |

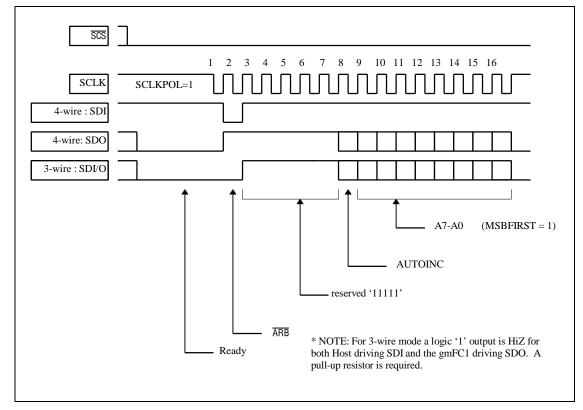

| FIGURE 25: HOST INTERFACE ADDRESS READ BACK (ARB) TRANSFER  | 48 |

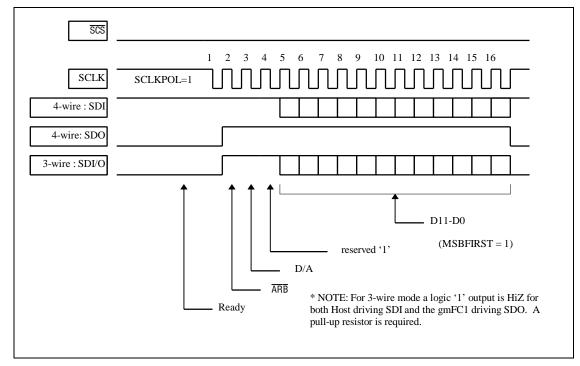

| FIGURE 26: HOST INTERFACE WRITE DATA TRANSFER               | 49 |

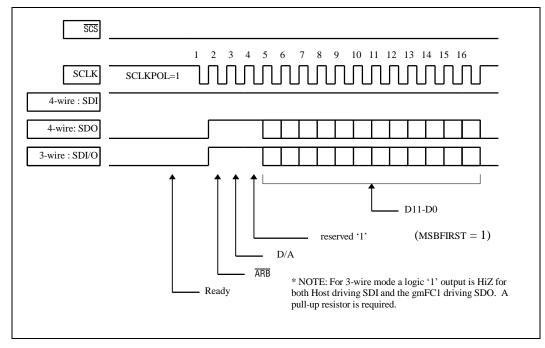

| FIGURE 27: HOST INTERFACE READ DATA TRANSFER                | 50 |

| FIGURE 28: HOST INTERFACE STOP CONDITION                    | 50 |

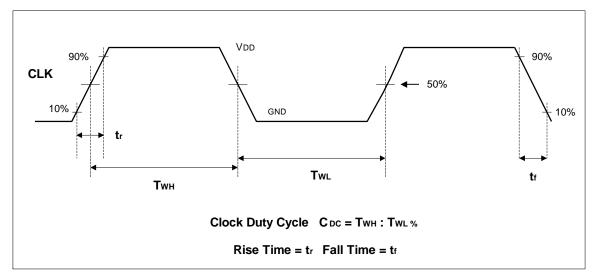

| FIGURE 29 CLOCK TIMING MEASUREMENT                          | 67 |

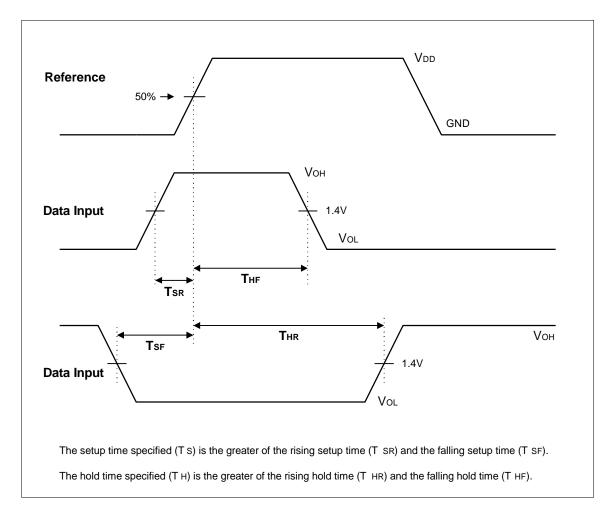

| FIGURE 30: INPUT SETUP AND HOLD TIME MEASUREMENT            | 68 |

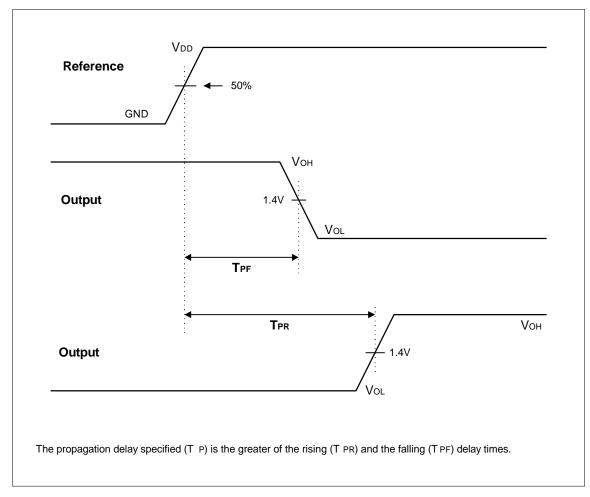

| FIGURE 31: OUTPUT PROPAGATION DELAY MEASUREMENT             | 71 |

| FIGURE 32: R1 - 208 PIN PLASTIC QUAD FLAT PACK (PQFP)       | 75 |

# 1. Overview

The Genesis Microchip gmFC1 functions as a graphics and video frame buffer controller capable of performing frame rate conversion by replicating or dropping incoming data as necessary to maintain a set output frame rate. Frame rate conversion is required in applications where it is necessary to manage high input data rates or accommodate varying video and graphics input frame rates when using display devices operating at a fixed frame rate.

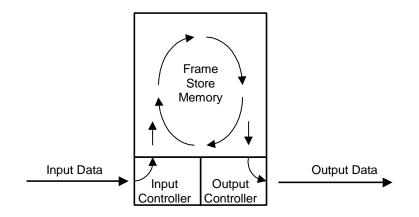

Schematically, the gmFC1 may be thought of as a control device for two circular buffers; the input buffer being write-only, and the output buffer read-only. (See Figure 1 below.) Incoming data is continuously written to the input buffer loop as it arrives. Output data is continuously read from the output buffer loop as required. If the buffers do not overlap, double buffering of data is enabled and frame tear is prevented. Although it is best to prevent frame tear whenever possible, frame tear may not be objectionable in graphics and video applications containing little motion between adjacent frames. As a rule, unless there are noticeable visual differences in successive frames, frame tear is essentially invisible. In the case of motion video, frame tear artifacts may be perceptible along areas of motion. While double buffering, the location of buffers is managed so the output consists of recently acquired input data, and the input does not overwrite output data as it is being displayed. Thus, entire frames may be dropped or replicated at the output, and an individual output frame will consist of data from only a single input frame.

Figure 1. gmFC1 - Overlapping Circular Buffers

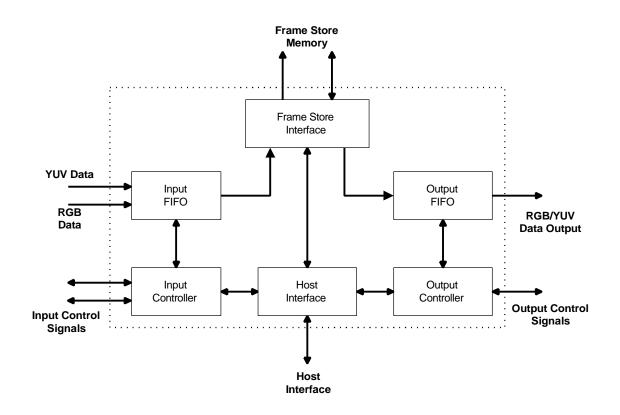

Figure 2 below illustrates the gmFC1 internal functional blocks and external interfaces. The data input interface is divided into separate RGB (graphics) and a YUV (video) input ports, further described in the following sections.

Figure 2: gmFC1 Functional Block Diagram

GENESIS

# 2. Features and Applications

# Features

- 24-bit single pixel wide I/O interfaces

- Independent RGB and YUV input ports

- Supports non-interlaced and vertical / horizontal interlaced formats

- Simplifies input format detection

- Enables constant output frame rate with variable input rates

- Drops or replicates input data to maintain output frame rate

- Seamless interface to the Genesis gmZ1/Z2/Z3 zoom scaler

- Seamless interface to three external frame store 1M x 16-bit SDRAMs

- Eliminates frame tear when double buffering enabled

- Pads or truncate input lines to a programmed output image size

- Seamless interface to common RGB ADCs

- Allows 1:1 windowing of lower resolution inputs on high resolution displays

- 500Mbytes/sec I/O bandwidth

- 3.3 Volt operation, 5 Volt tolerant I/O

- 208 pin PQFP package

# Input Format

- Single pixel wide input interface (selectable from independent 24-bit RGB and 16-bit YUV ports)

- Programmable to accept either sequential or interlaced pixels

- Input window cropping

- Flags Input Timing Errors lines are padded to correct size

- Supports input formats up to 1024 x 768 at 85 Hz (95 MHz pixel clock) (dependent on output format maximum total I/O bandwidth limit of ~ 500 MBytes/s)

# **Output Format**

- Single pixel wide output interface

- Supports output formats up to 1024 x 768 at 85 Hz (dependent on input format - maximum total I/O bandwidth limit of ~ 500 MBytes/s)

- 24-bit RGB or 16-bit YUV dependent on input data format

- Frame Rate Conversion

- Output faster than input

- Output slower than input

- Disabled: frame rate locked to input

# Host Interface

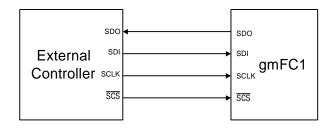

• gmZ1/Z2/Z3 compatible three or four wire serial host interface port

#### Frame Store Interface

- 48-bit wide path to external frame store (3 x16 SDRAM devices)

- 32-bit wide path to external frame store for YUV-only applications (2x16 SDRAM)

- Three 1M x 16-bit devices = 500 Mbytes/sec I/O data rate 85 Hz XGA in, 60 Hz XGA out. [ (85Hz XGA + 60Hz XGA) x 3 bytes/pixel ]

- Compatible 1M x 16-bit, 100MHz memory devices include:

| IBM     | IBM0316169   |

|---------|--------------|

| Hitachi | HM216165     |

| NEC     | uPD4516161   |

| Toshiba | TC59S1616AFT |

| TI      | TMS626162    |

| Samsung | KM416S1020B  |

• Any 4M x 16-bit (64 Mbit) device conforming to SDRAM standards may also interface to the gmFC1. Compatible 4M x 16-bit SDRAM devices include:

| Toshiba    | TC59S6416BFT-10    |

|------------|--------------------|

| Mitsubishi | MB611641642A-100FN |

| Samsung    | KM416S4030BT-GB    |

# Applications

• Accommodates BIOS and various Windows frame rates during Windows boot up sequence:

BIOS Screen - 720x400 text mode, 70 Hz Windows 95 Boot Up Screen Graphics - 640x480 16-color mode, 60 Hz Windows Environment - User selectable, VGA, SVGA, XGA, etc.

- Manage high input data rates by reducing frame rates

- Manage various input frame rates to support fixed frame rate O/P such as LCD panels, ex: XGA, PAL, RGB, VESA proposed 85 Hz Standards, older DOS screens @ 70 and 85 Hz, MAC standard formats

- Games preferring low resolutions

- Special effects using frame buffer, ex: cropped zooms, freeze frame, 1:1 windowing

- Simplified FRC designs

- System cost reduction in applications ordinarily requiring expensive variable refresh LCD panels

# 3. General Operation

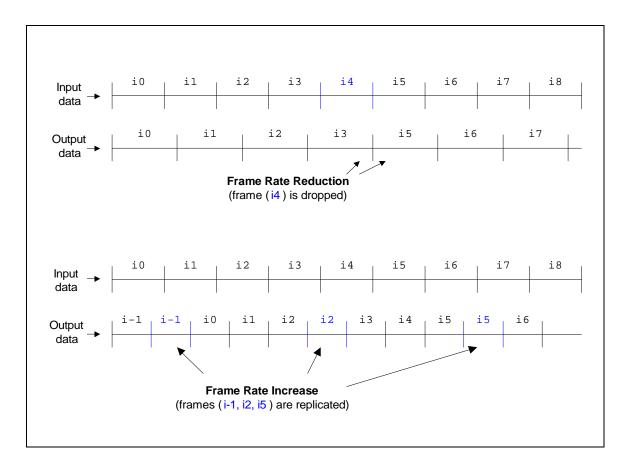

The gmFC1 is designed to simplify frame rate conversion of both graphics and digital video (YUV) data, allowing a variety of input formats to be interfaced to a single format display device. Frame rates may be reduced or increased to accommodate the output display. Figure 3 below shows the frame rate reduction and frame replication process, where each horizontal segment represents an entire two dimensional frame. In this example, double buffering is enabled and no frame tearing occurs.

**Figure 3. Frame Rate Conversion Process**

# 3.1 Typical Systems

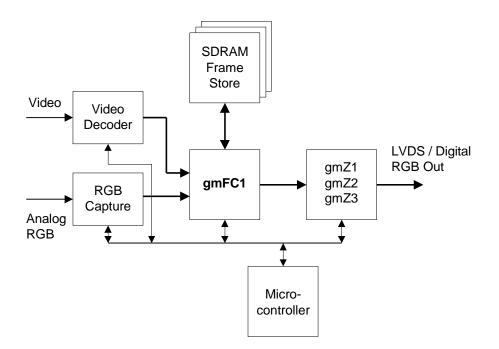

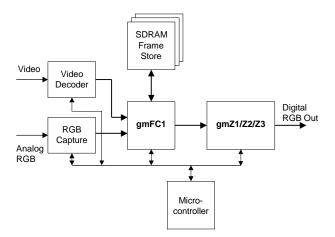

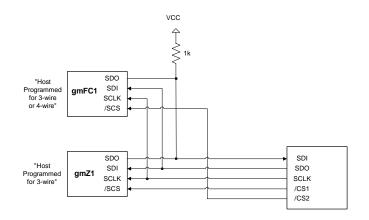

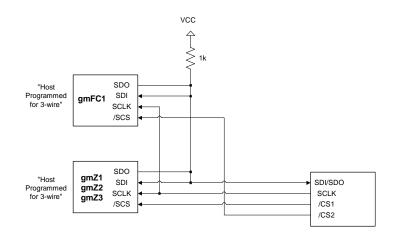

In a typical system, the gmFC1 is seamlessly interfaced to an SDRAM based frame store, input ADC, and the Genesis gmZ1/Z2/Z3 for output to an LCD display panel (see Figure 4 below). The gmFC1 provides data as required by the gmZ1/Z2/Z3 to sustain the programmed display timing. The gmZ1/Z2/Z3 operates in Free Run Mode, with all required display timing programmed into its display register set. (Frame Lock mode is also possible, although it is recommended only for applications where frame dropping/duplication is not desired.) A shared microcontroller oversees all frame rate conversion, image scaling operations and input format detection through a compatible three or four wire serial host interface.

Figure 4: Typical gmFC1 Implementation

# 4. Pinout

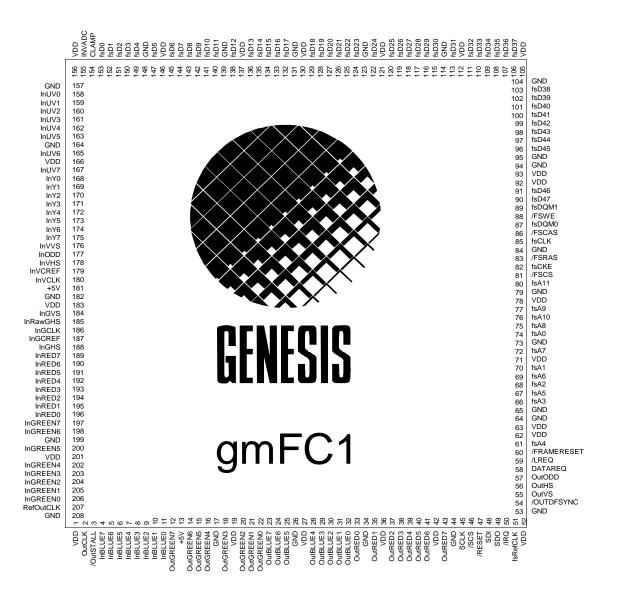

# 4.1 gmFC1 Pinout- Chip Diagram

Figure 5: gmFC1 Pinout

# 4.2 gmFC1 Pinout- Pin List

Table 1 below lists each gmFC1 pin, and provides a concise description of each signal. A detailed signal description may be found on the page listed in the Page column.

|       | Input Interface                                                                                                                              |               |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Signal Name                                                                                                                                  | I/O           | Page | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4     | InBlue7                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5     | InBlue6                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6     | InBlue5                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7     | InBlue4                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8     | InBlue3                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9     | InBlue2                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10    | InBlue1                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11    | InBlue0                                                                                                                                      | l (pull-down) | 23   | Input RGB BLUE data LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 50    | INDATAACTIVE / IRQ                                                                                                                           | 0             | 25   | Input Data Active<br>The INDATAACTIVE output signal indicates when<br>the gmFC1 is expecting valid data based on the<br>host programmed active data region registers.<br>Interrupt Request<br>The IRQ interrupt pin of the host interface is<br>physically shared with INDATAACTIVE. The<br>IRQ_OUT_EN bit in the IRQMASK register<br>controls the pin function.                                                                                                                                                                         |

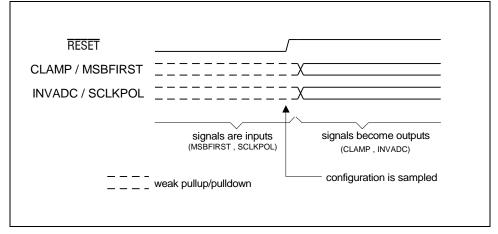

| 154   | CLAMP /<br>MSBFIRST<br>When $\overline{\text{RESET}} = 1$ ,<br>pin 154 = CLAMP<br>When $\overline{\text{RESET}} = 0$ ,<br>pin 154 = MSBFIRST | 0/1           | 23   | The <b>CLAMP</b> output is a pulse with a programmable width and location with respect to InGHS. Can be used to indicate the point for DC restoration in analog RGB signals. The CLAMP pin is shared with:<br>MSBFIRST, Host I/F Mode Select Input. Selects serial data (SDI/SDO) bit ordering. If = '1', the MSB is shifted first. The value is latched on the rising (negating) edge of RESET.                                                                                                                                         |

| 155   | INVADC /<br>SCLKPOL<br>When RESET = 1,<br>pin 155 = INVADC<br>When RESET = 0,<br>pin 155 = SCLKPOL                                           | O/I           | 23   | Invert ADC sampling clock. (Output)         INVADC is used in horizontal interlace mode to request the ADC to invert its sample clock. It will toggle every graphics frame when in this mode. The INVADC pin is shared with:         SCLKPOL, Serial Clock Mode Select. (Input)         The value is latched on the rising (negating)         edge of RESET. This selects the active edge of the host interface shift clock, SCLK. If 0, SDI is sampled on the SCLK falling edge. Otherwise, SDI is sampled on the SCLK falling edge and |

Table 1: gmFC1 Pinout Description

# gmFC1 Data Sheet

|     |          |                                         |    | SDO shifted out on the rising edge.            |

|-----|----------|-----------------------------------------|----|------------------------------------------------|

| 158 | InUV0    | l (pull-down)                           | 25 | UV Video Data Input LSB                        |

| 150 | InUV1    | I (pull-down)                           | 25 | UV Video Data Input                            |

| 160 | InUV2    | I (pull-down)                           | 25 | UV Video Data Input                            |

| 161 | InUV3    | I (pull-down)                           | 25 | UV Video Data Input                            |

| 162 | InUV4    | I (pull-down)                           | 25 | UV Video Data Input                            |

| 163 | InUV5    | I (pull-down)                           | 25 | UV Video Data Input                            |

| 165 | InUV6    | I (pull-down)                           | 25 | UV Video Data Input                            |

| 167 | InUV7    | I (pull-down)                           | 25 | UV Video Data Input<br>UV Video Data Input MSB |

| 168 | InY0     | I (pull-down)                           | 25 | Y Video Data Input LSB                         |

| 169 | InY1     | I (pull-down)                           | 25 | Y Video Data Input                             |

| 109 | InY2     | I (pull-down)                           | 25 | Y Video Data Input                             |

| 170 | InY3     |                                         | 25 | Y Video Data Input                             |

| 171 | InY4     | I (pull-down)                           | 25 | Y Video Data Input                             |

| 172 | InY5     | . , , , , , , , , , , , , , , , , , , , | 25 | •                                              |

| 173 | InY6     | l (pull-down)                           | 25 | Y Video Data Input<br>Y Video Data Input       |

| 174 | InY7     | l (pull-down)                           | 25 | Y Video Data Input<br>Y Video Data Input MSB   |

| -   | InVVS    | l (pull-down)                           |    |                                                |

| 176 |          | l (pull-down)                           | 25 | YUV Port Vertical Sync Input                   |

| 177 | InODD    | l (pull-down)                           | 26 | ODD field indicator in interlaced mode         |

| 178 | InVHS    | l (pull-down)                           | 25 | YUV Port Horizontal Sync Input                 |

| 179 |          | l (pull-down)                           | 24 | InVCLK YUV clock qualifier                     |

| 180 | InVClk   | l (pull-down)                           | 24 | YUV Port Clock                                 |

| 184 | InGVS    | l (pull-down)                           | 23 | RGB Port Vertical Sync Input                   |

| 185 | InRawGHS | l (pull-down)                           | 20 | Raw Horizontal Sync source input from ADC      |

| 186 | InGClk   | l (pull-down)                           | 18 | RGB Port Clock                                 |

| 187 | InGCRef  | l (pull-down)                           | 19 | InGCLK RGB clock qualifier                     |

| 188 | InGHS    |                                         | 19 | RGB Port Horizontal Sync Input                 |

| 189 | InRed7   | l (pull-down)                           | 23 | Input RGB RED data MSB                         |

| 190 | InRed6   | l (pull-down)                           | 23 | Input RGB RED data                             |

| 191 | InRed5   | l (pull-down)                           | 23 | Input RGB RED data                             |

| 192 | InRed4   | l (pull-down)                           | 23 | Input RGB RED data                             |

| 193 | InRed3   | l (pull-down)                           | 23 | Input RGB RED data                             |

| 194 | InRed2   | l (pull-down)                           | 23 | Input RGB RED data                             |

| 195 | InRed1   | l (pull-down)                           | 23 | Input RGB RED data                             |

| 196 | InRed0   | l (pull-down)                           | 23 | Input RGB RED data LSB                         |

| 197 | InGreen7 | l (pull-down)                           | 23 | Input RGB GREEN data MSB                       |

| 198 | InGreen6 | l (pull-down)                           | 23 | Input RGB GREEN data                           |

| 200 | InGreen5 | l (pull-down)                           | 23 | Input RGB GREEN data                           |

| 202 | InGreen4 | l (pull-down)                           | 23 | Input RGB GREEN data                           |

| 203 | InGreen3 | l (pull-down)                           | 23 | Input RGB GREEN data                           |

| 204 | InGreen2 | l (pull-down)                           | 23 | Input RGB GREEN data                           |

| 205 | InGreen1 | l (pull-down)                           | 23 | Input RGB GREEN data                           |

| 206 | InGreen0 | l (pull-down)                           | 23 | Input RGB GREEN data LSB                       |

Note:

l (pull-down):

Indicates that these gmFC1 inputs are provided with internal pull-down resistors typically valued at 91Kohm.

| <b>~00</b> 0 |  |

|--------------|--|

| GENESIS      |  |

|       | Output Interface |     |      |                                                 |

|-------|------------------|-----|------|-------------------------------------------------|

| Pin # | Signal Name      | I/O | Page | Description                                     |

| 2     | OutClk           | 0   | 32   | Clock driving gmZ1/2/3. Based on RefOutCLK.     |

| 3     | OUTSTALL         | 0   | 33   | Stall control to gmZ1 / gmZ2 / gmZ3             |

| 12    | OutGreen7        | 0   | 34   | Output RGB GREEN data MSB                       |

| 14    | OutGreen6        | 0   | 34   | Output RGB GREEN data                           |

| 15    | OutGreen5        | 0   | 34   | Output RGB GREEN data                           |

| 16    | OutGreen4        | 0   | 34   | Output RGB GREEN data                           |

| 18    | OutGreen3        | 0   | 34   | Output RGB GREEN data                           |

| 20    | OutGreen2        | 0   | 34   | Output RGB GREEN data                           |

| 21    | OutGreen1        | 0   | 34   | Output RGB GREEN data                           |

| 22    | OutGreen0        | 0   | 34   | Output RGB GREEN data LSB                       |

| 23    | OutBlue7         | 0   | 34   | Output RGB BLUE data MSB / Output UV            |

|       |                  |     |      | MSB                                             |

| 24    | OutBlue6         | 0   | 34   | Output RGB BLUE data / Output UV                |

| 25    | OutBlue5         | 0   | 34   | Output RGB BLUE data / Output UV                |

| 28    | OutBlue4         | 0   | 34   | Output RGB BLUE data / Output UV                |

| 29    | OutBlue3         | 0   | 34   | Output RGB BLUE data / Output UV                |

| 30    | OutBlue2         | 0   | 34   | Output RGB BLUE data / Output UV                |

| 31    | OutBlue1         | 0   | 34   | Output RGB BLUE data / Output UV                |

| 32    | OutBlue0         | 0   | 34   | Output RGB BLUE data LSB / Output UV LSB        |

| 33    | OutRed0          | 0   | 34   | Output RGB RED data LSB / Output Y LSB          |

| 35    | OutRed1          | 0   | 34   | Output RGB RED data / Output Y                  |

| 37    | OutRed2          | 0   | 34   | Output RGB RED data / Output Y                  |

| 38    | OutRed3          | 0   | 34   | Output RGB RED data / Output Y                  |

| 39    | OutRed4          | 0   | 34   | Output RGB RED data / Output Y                  |

| 40    | OutRed5          | 0   | 34   | Output RGB RED data / Output Y                  |

| 41    | OutRed6          | 0   | 34   | Output RGB RED data / Output Y                  |

| 43    | OutRed7          | 0   | 34   | Output RGB RED data MSB / Output Y MSB          |

| 54    | OUTDFSYNC        | 0   | 34   | Forces gmZ1/2/3 frame re-synchronization        |

| 55    | OutVS            | 0   | 33   | Output Vertical Sync                            |

| 56    | OutHS            | 0   | 33   | Output Horizontal Sync                          |

| 57    | OutODD           | 0   | 33   | Indicates interlaced output field is ODD        |

| 58    | DATAREQ          | I   | 33   | Data Request - the gmFC1 will slave to requests |

|       |                  |     |      | for data at the DATAREQ pin when the            |

|       |                  |     |      | OP_HANDSH register bit = 0, providing data      |

|       |                  |     |      | three clock cycles after DATAREQ is asserted.   |

| 59    | LREQ             | I   | 33   | Line Request Input - accepts gmZ1/2/3 VCLREQ    |

| 60    | FRAMERESET       | I   | 32   | Forces start of new output frame                |

| 207   | RefOutCLK        | 1   | 32   | Clock reference for output interface            |

|           | Power       |     |      |             |

|-----------|-------------|-----|------|-------------|

| Pin #     | Signal Name | I/O | Page | Description |

| 1, 19,    | VDD         |     |      | 3.3VDC      |

| 27, 36,   |             |     |      |             |

| 42, 52,   |             |     |      |             |

| 62, 63,   |             |     |      |             |

| 71, 78,   |             |     |      |             |

| 92, 93,   |             |     |      |             |

| 105, 112, |             |     |      |             |

| 121, 130, |             |     |      |             |

| 137, 146, |             |     |      |             |

| 156, 166, |             |     |      |             |

| 183, 201  |             |     |      |             |

| 13, 181   | +5V         |     |      | +5VDC *     |

| 17, 26,   | Gnd         |     |      | Ground      |

| 34, 44,   |             |     |      |             |

| 53, 64,   |             |     |      |             |

| 65, 73,   |             |     |      |             |

| 79, 84,   |             |     |      |             |

| 94, 95,   |             |     |      |             |

| 104, 114, |             |     |      |             |

| 123, 131, |             |     |      |             |

| 139, 148, |             |     |      |             |

| 157, 164, |             |     |      |             |

| 182, 199, |             |     |      |             |

|           |             |     |      |             |

\* +5VDC supplies may be wired to 3.3VDC if no 5V tolerance on inputs is required

208

GENESIS

|       | Host Interface                                                                                  |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin # | Signal Name                                                                                     | I/O | Page | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 45    | SCLK                                                                                            | Ι   | 40   | Host Interface Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                           |

| 46    | SCS                                                                                             | Ι   | 40   | Serial Chip Select - Host Interface Enable                                                                                                                                                                                                                                                                                                                                                                                            |

| 47    | RESET                                                                                           | Ι   | 40   | Reset input to initialize device                                                                                                                                                                                                                                                                                                                                                                                                      |

| 48    | SDI                                                                                             | I   | 41   | Host Interface Serial Data Input                                                                                                                                                                                                                                                                                                                                                                                                      |

| 49    | SDO                                                                                             | 0   | 41   | Host Interface Serial Data Output                                                                                                                                                                                                                                                                                                                                                                                                     |

| 50    | IRQ / INDATAACTIVE                                                                              | 0   | 41   | Interrupt Request<br>The IRQ interrupt pin of the host interface is<br>physically shared with INDATAACTIVE. The<br>IRQ_OUT_EN bit in the IRQMASK register<br>controls the pin function.<br>Input Data Active<br>The INDATAACTIVE output signal indicates when<br>the gmFC1 is expecting valid data based on the                                                                                                                       |

| 154   | MSBFIRST / CLAMP<br>When RESET = 1,<br>pin 154 = CLAMP<br>When RESET = 0,<br>pin 154 = MSBFIRST | I/O | 40   | host programmed active data region registers.MSBFIRST - Host I/F Mode Select Input.Selects serial data (SDI/SDO) bit ordering. If ='1', the MSB is shifted first. The value is latchedon the rising (negating) edge of RESET. TheMSBFIRST pin is shared with CLAMP.The CLAMP output is a pulse with aprogrammable width and location with respect toInGHS. Can be used to indicate the point for DCrestoration in analog RGB signals. |

| 155   | SCLKPOL / INVADC<br>When RESET = 1,<br>pin 155 = INVADC<br>When RESET = 0,<br>pin 155 = SCLKPOL | I/O | 40   | SCLKPOL - Serial Clock Mode Select. (Input)<br>The value is latched on the rising (negating)<br>edge of RESET. This selects the active edge of the<br>host interface shift clock, SCLK. If 0, SDI is<br>sampled on the SCLK rising edge and SDO is<br>shifted out on the SCLK falling edge. Otherwise,<br>SDI is sampled on the SCLK falling edge and<br>SDO shifted out on the rising edge. SCLKPOL is<br>shared with INVADC.        |

|       |                                                                                                 |     |      | Used in horizontal interlace mode to request the ADC to invert its sample clock. It will toggle every InGVS when in this mode.                                                                                                                                                                                                                                                                                                        |

| GENESIS |  |

|---------|--|

| Frame Store<br>Interface |             |     |      |                          |                  |

|--------------------------|-------------|-----|------|--------------------------|------------------|

| Pin #                    | Signal Name | I/O | Page | Descri                   | otion            |

| 74                       | fsA0        | 0   | 38   | Frame Store Address Line | )                |

| 70                       | fsA1        | 0   | 38   | Frame Store Address Line | )                |

| 68                       | fsA2        | 0   | 38   | Frame Store Address Line | )                |

| 66                       | fsA3        | 0   | 38   | Frame Store Address Line | )                |

| 61                       | fsA4        | 0   | 38   | Frame Store Address Line | )                |

| 67                       | fsA5        | 0   | 38   | Frame Store Address Line | )                |

| 69                       | fsA6        | 0   | 38   | Frame Store Address Line | )                |

| 72                       | fsA7        | 0   | 38   | Frame Store Address Line | )                |

| 75                       | fsA8        | 0   | 38   | Frame Store Address Line | )                |

| 77                       | fsA9        | 0   | 38   | Frame Store Address Line | )                |

| 76                       | fsA10       | 0   | 38   | Frame Store Address Line |                  |

| 80                       | fsA11       | 0   | 38   | Frame Store Address Line |                  |

|                          | -           |     |      |                          |                  |

| 153                      | fsD0        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 152                      | fsD1        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 151                      | fsD2        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 150                      | fsD3        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 149                      | fsD4        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 147                      | fsD5        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 145                      | fsD6        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 144                      | fsD7        | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 143                      | fsD8        | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 142                      | fsD9        | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 141                      | fsD10       | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 140                      | fsD11       | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 138                      | fsD12       | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 136                      | fsD13       | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 135                      | fsD14       | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 134                      | fsD15       | I/O | 38   | Frame Store Data Line    | (GREEN data)     |

| 133                      | fsD16       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 132                      | fsD17       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 129                      | fsD18       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 128                      | fsD19       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 127                      | fsD20       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 126                      | fsD21       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 125                      | fsD22       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 124                      | fsD23       | I/O | 38   | Frame Store Data Line    | (RED / Y data)   |

| 122                      | fsD24       | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 120                      | fsD25       | I/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 119                      | fsD26       | 1/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 118                      | fsD27       | 1/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 117                      | fsD28       | 1/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 116                      | fsD29       | 1/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 115                      | fsD30       | 1/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

| 113                      | fsD31       | 1/O | 38   | Frame Store Data Line    | (BLUE / UV data) |

# gmFC1 Data Sheet

| 111 | fsD32    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

|-----|----------|-----|----|----------------------------------------------------|

| 110 | fsD33    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 109 | fsD34    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 108 | fsD35    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 107 | fsD36    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 106 | fsD37    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 103 | fsD38    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 102 | fsD39    | I/O | 38 | Frame Store Data Line (GREEN data)                 |

| 101 | fsD40    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 100 | fsD41    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 99  | fsD42    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 98  | fsD43    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 97  | fsD44    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 96  | fsD45    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 91  | fsD46    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

| 90  | fsD47    | I/O | 38 | Frame Store Data Line (RED / Y data)               |

|     |          |     |    |                                                    |

| 86  | FSCAS    | 0   | 38 | Frame Store Column Address Strobe                  |

| 82  | fsCKE    | 0   | 38 | Frame Store Clock Enable                           |

| 85  | fsCLK    | 0   | 38 | Frame Store Clock - based on fsRefCLK              |

| 81  | FSCS     | 0   | 38 | Frame Store Chip Select                            |

| 87  | fsDQM0   | 0   | 38 | SDRAM Data Mask. FsDQM0 and fsDQM1 (pin            |

|     |          |     |    | 89) are functionally identical but split to reduce |

|     |          |     |    | loading.                                           |

|     |          |     |    | Each SDRAM device has an upper and lower           |

|     |          |     |    | DQM.                                               |

| 89  | fsDQM1   | 0   | 38 | SDRAM Data Mask. FsDQM0 (pin 87) and               |

|     |          |     |    | fsDQM1 are functionally identical but split to     |

|     |          |     |    | reduce loading.                                    |

|     |          |     |    | Each SDRAM device has an upper and lower           |

|     |          |     |    | DQM.                                               |

| 83  | FSRAS    | 0   | 38 | Frame Store Row Address Strobe                     |

| 51  | fsRefCLK | I   | 38 | Frame Store Interface Clock Oscillator Input       |

| 88  | FSWE     | 0   | 38 | Frame Store Write Enable                           |

|     |          |     |    |                                                    |

# 5. Functional Description

# 5.1 Power On Reset

A hard reset is required after power-up to ensure proper operation of all gmFC1 functional blocks and guarantee gmFC1 register contents. A hard reset may be performed by asserting RESET for a minimum of 250ns with a stable frame store clock (fsRefCLK) applied to the gmFC1. All host writable register contents default to '0' upon a hard reset, except the SOFT\_RESET bit 00 and RESERVED bit 08 in the HOSTCTRL register. See Table 5 for details. After a hard reset, all input clocks must be running and stable before gmFC1 registers may be accessed.

A SOFT\_RESET affects all gmFC1 functional blocks except the Host Interface registers, effectively disabling the input, output and frame store interfaces. All Host Interface registers may be loaded in any order while SOFT\_RESET =1. To complete the initialization procedure, IN\_FORC\_UPDATE and OUT\_FORC\_UPDATE are set to '1', and the SOFT\_RESET bit is cleared to '0'.

The gmFC1 frame store SDRAM is unavailable for 200us after a hard or soft reset. The gmFC1 will automatically perform an SDRAM power-on sequence following the negating edge of a RESET to ensure reliable SDRAM access. The SDRAM power-on sequence will also be performed during a host initiated SOFT\_RESET. Note that the SDRAM is not cleared on a hard or soft reset. This will result in the first output frame after power up being read as random display data if the output is enabled before the input is enabled.

# 5.2 Data Input

The gmFC1 provides two separate data input ports: a 24-bit RGB graphics data port, and a 16-bit YUV video data port. Each port provides a complete control interface. The active data source is selected through the IPCTRL host programmable register IP\_RGB\_nYUV. In this way, the gmFC1 acts as a data stream multiplexer. All Input Port signals except INVADC, InGHS, and CLAMP are provided with internal pull-down resistors.

# Figure 6. gmFC1 Input Multiplexer

# 5.2.1 RGB Graphics Input Modes

GENESI

Data input to the gmFC1 RGB graphics port may be interpreted in one of three ways - Progressive Scan, Vertical Interlace, and Horizontal Interlace. The appropriate mode is selected through the IP\_VINTLC\_EN and IP\_HINTLC\_EN register bits, as in Table 2 below. Note that Horizontal and Vertical Interlace modes may not be enabled simultaneously.

| Mode                 | IP_VINTLC_EN | IP_HINTLC_EN |

|----------------------|--------------|--------------|

| Progressive Scan     | 0            | 0            |

| Horizontal Interlace | 0            | 1            |

| Vertical Interlace   | 1            | 0            |

| Not Allowed          | 1            | 1            |

Table 2: Graphics Input Modes

In Progressive Scan mode, the input data represents spatially contiguous sample points of the input image.

Vertical interlacing is a common technique in video systems to reduce bandwidth. It is less common in computer graphics. In Vertical Interlace mode, data is input to the gmFC1 in fields containing only odd or even lines of data. Successive alternating odd and

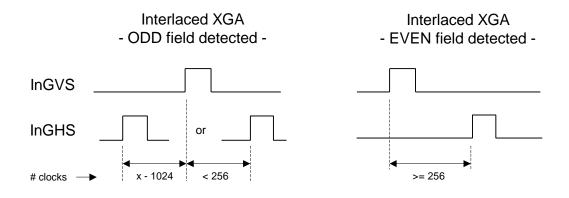

even fields make up the entire image. The gmFC1 automatically determines the state of the current XGA Vertical Interlace Mode field from the timing of InGHS relative to InGVS (see Figure 7 below). If this feature is disabled by setting the IPCTRL register bit EXTGODD\_EN=1, the InODD signal is used to determine the current field state.

where x= the total number of clocks per line of incoming data

# Figure 7: XGA Vertical Interlace Mode Field Detection

In Horizontal Interlace mode, data is input to the gmFC1 in fields containing only odd or only even pixels. The fields alternate between sets of odd and even pixels to make up the entire image. This technique may be useful when sampling computer graphics data. The sample rate, and therefore required bandwidth, is halved. See the INVADC description on page 23 for further details.

# 5.2.2 YUV Video Input Modes

The gmFC1 supports Progressive Scan and Vertically Interlaced formats as described in Section 5.2.1 above, although automatic determination of odd/even fields is not available in YUV Modes. Horizontal Interlaced YUV data is not supported.

# 5.2.3 Input Active Window Control

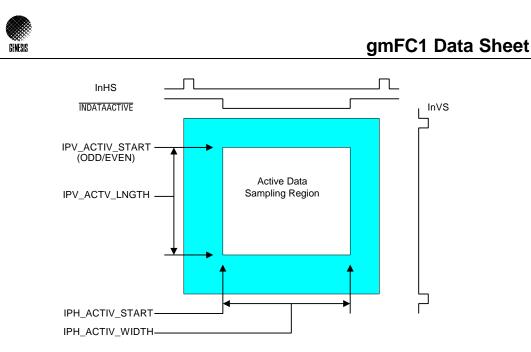

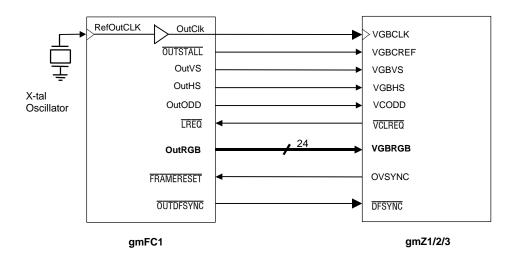

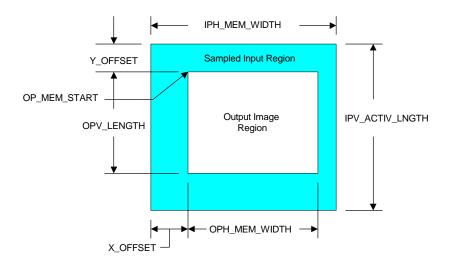

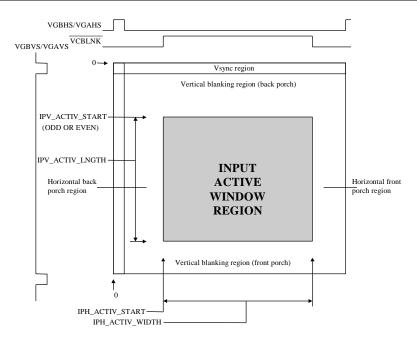

The gmFC1 contains host programmable registers which define the input active data region with respect to input vertical and horizontal sync pulses. Figure 8 below illustrates how these registers control the active input sampling region.

Figure 8: Input Data Sampling Window

# 5.2.4 Input Synchronization

Modifications to the input data window registers do not take effect immediately. After all desired changes have been made, the external system may set the input update enable bit, IN\_UPDATE\_EN. This causes the input parameters to become active only at the next input vertical sync. This mechanism ensures input frames are not captured with partially updated parameters. It is also possible for the host to force an immediate update by setting the IN\_FORC\_UPDATE bit within the HOSTCTRL register, causing modified parameters to become active without waiting for an input VSYNC. See Section 5.8.2 for further details.

# 5.2.5 Freeze Frame

The input data capture circuitry may be disabled through the host programmed register INP\_EN. When disabled, the gmFC1 continues to display previously captured data, providing freeze frame capability.

# 5.3 Graphics (RGB) Input Port Signals

The Graphics (RGB) Input Port signals are active when the gmFC1 is operating with the RGB port selected, by setting the HOSTCTRL register bit IP\_RGB\_nYUV=1. Otherwise, this port is ignored. All Graphics Input Port signals except INVADC, InGHS, and CLAMP are provided with internal pull-down resistors.

# InGCLK

InGCLK provides the timing reference for the RGB port signals. The active edge is programmable through the IPCLK\_INV register.

# InGCREF

InGCREF further qualifies InGCLK. InGCREF must be active during an active InGCLK edge to validate the InGCLK cycle, i.e., InGCREF can be considered an InGCLK clock enable. In most designs, the CREF signals may be hard-wired to either VCC or GND to validate all clocks. The active polarity of InGCREF is programmable through the IPCTRL register control bit IPCREF\_INV.

If the CREF qualifier signals InVCREF / InGCREF are left floating or not connected, the gmFC1 may operate incorrectly. It is recommended that any unused input clock reference signals (InVCREF or InGCREF) be tied either HIGH or LOW. When the clock reference is tied HIGH, program the gmFC1 IPCTRL register bit IPCREF\_INV (Register 05, bit 1) = 1. When the clock reference is tied LOW, program IPCREF\_INV = 0.

Figure 9: Graphics Input Data Handshaking

# InGHS

InGHS is the RGB port horizontal sync input. The active edge of InGHS is sampled synchronously to InGCLK, and resets clock counters used in determining the active data region. The active polarity of InGHS is programmable through the IPCTRL register control bit IPHS\_INV. Some amount of skew, approximately 18 InGCLK periods, is accepted between InGHS and InGVS (i.e., if there are less than 18 InGCLK periods between InGVS and InGHS, the internal line counter is not incremented). This is required since the HSYNC is generally synchronized to the reconstructed pixel clock InGCLK, and may have a different path delay from the VSYNC.

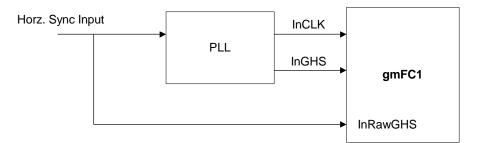

# InRawGHS

InRawGHS is the 'raw' horizontal sync input for the RGB port. This signal is used as the source for horizontal sync timing measurements when the RGB port is selected. By bypassing the PLL, input mode detection is possible prior to PLL programming.

Figure 10: Graphics Horizontal Sync. Inputs

#### Measurement example:

To measure the active pulse width of the Horizontal Sync Input at InRawGHS:

- 1. Write register MEAS\_VS\_nHS = 0 (measure Horizontal Sync)

- 2. Write register PERIOD\_nACTIVE = 0 (measure active 'high' width, not entire period)

- 3. Read MEAS\_VALID, wait until MEAS\_VALID =1 (a valid measurement is complete)

- 4. Read the measured result from MEAS\_RESULTL register

Note: The selected measurement is performed continuously once steps 1) and 2) are complete. MEAS\_VALID will remain set to '1' while the selected signal is being continuously re-measured. The most recent measurement is always available in the MEAS\_RESULTL register. The MEAS\_VALID bit will only be cleared to '0' if the MEAS\_VS\_nHS or PERIOD\_nACTIVE bits are re-written.

| Measured Parameter Units |               | gmFC1 HOSTCTRL Register settings |                |  |

|--------------------------|---------------|----------------------------------|----------------|--|

|                          |               | MEAS_VS_nHS                      | PERIOD_nACTIVE |  |

| H-Sync Period            | fsCLK / 2     | 0                                | 1              |  |

| H-Sync 'High' Period     | fsCLK / 2     | 0                                | 0              |  |

| V-Sync Period            | H-Sync pulses | 1                                | 1              |  |

| V-Sync 'High' Period     | H-Sync pulses | 1                                | 0              |  |

The following measurements are possible:

To determine the period of an input Horizontal or Vertical Sync signal, the gmFC1 register MEAS\_RESULTL (Registers 1A) is read by the system microcontroller. The measured value in this register is updated continuously. Erroneous values may be

interpreted from the MEAS\_RESULTL register if a read-back is requested during a register update.

For example, if the measured sync value is nominally 0x200, but occasionally varies to 0x1FF, the read-back value may be incorrectly read as 0x2FF if an update occurs between the time the "2" and the next most significant bit are shifted out of the gmFC1. This problem is particularly pronounced during HS measurement read-back, as HS updates occur more frequently than VS updates.

To avoid the possibility of incorrect read-back, it is possible to take advantage of the longer window between VS measurement updates to perform an HS measurement value read-back. The recommended sequence is given below, with the corrective steps highlighted in a box.

#### 1. Program the gmFC1 to measure HS:

WRITE (Register 03 bit 09) MEAS\_VS\_nHS = 0 WRITE (Register 03 bit 10) PERIOD\_nACTIVE = 0)

(measure HS) (measure full period =1, measure hi time

# 2. Poll (check) gmFC1 to ensure at least one valid measurement has been completed:

READ (Register 01 bit 10) MEAS\_VALID = 1

3. Poll gmFC1 for a VS pulse (MEAS\_RESULT registers are continuously updated)

:

READ (Register 01 bit 08) IPRGB\_VS = 1

[ or READ (Register 01 bit 07) IPYUV\_VS = 1 for YUV inputs ]

4. Program gmFC1 to measure VS period (this guarantees no more updates to the MEAS\_RESULT registers until the next VS, giving the microcontroller one frame period to read the correct HS measurement results) :

WRITE (Register 03 bit 09) MEAS VS nHS = 1 (measure VS)

WRITE (Register 03 bit 09) MEAS\_VS\_NHS = 1 (measure vS) WRITE (Register 03 bit 10) PERIOD\_nACTIVE =1 (measure full VS period)

# **5.** Read the 'captured' HS measurement value (this must be completed prior to next VS) :

READ (Register 1A) MEAS\_RESULTL

Similarly, when reading VS measurement values from MEAS\_RESULTL register, wait for a VS pulse and read the registers immediately to guarantee the read will not occur during an update.

GENESU

#### **'C'** psuedo-code for the HS measurement and read procedure is given below:

```

/*

HS Period Measurement Procedure

MeasureHSPeriod:

*

{

*

SelectMeasurement (HS_Period);

WaitForValidMeasurement;

WaitForVSYNC;

*

SelectMeasurement (VS_Period);

ReadMeasurementResult;

*

}

*/

uint

MeasHSPeriod ()

{

int hostctrl;

int status;

uint result;

hostctrl = gmFC1_Rd (fc1_HOSTCTRL); /* read contents of HOSTCTRL register to the hostctrl variable

*/

hostctrl = hostctrl & (~MEAS_VS_nHS); /* select HS */

hostctrl = hostctrl | (PERIOD_nACTIVE); /* period */

gmFC1_Wr (fc1_HOSTCTRL, hostctrl); /* write new value of HOSTCTRL register */

while (1) {

wait for measurement to be valid

*/

status = gmFC1_Rd (fc1_STATUS);

if ((status & MEAS_VALID) != 0) {

break; /* measurement is valid and ready */

}

}

/*

once the horizontal measurement is valid, wait for VSYNC rising edge,

switch to VSYNC measurement, and immediately read the result.

*/

status = gmFC1_Rd (fc1_STATUS); /* read STATUS register to clear VSYNC bit */

while (1) {

wait for VSYNC

*/

status = gmFC1_Rd (fc1_STATUS);

if ((status & IPRGB_VS) != 0) {

break; /* VSYNC detected */

}

}

/*

switch to VSYNC measurement - prevents updates to the previously measured HSYNC value for 1

frame

*/

hostctrl = hostctrl | (MEAS_VS_nHS); /* select VS */

gmFC1_Wr (fc1_HOSTCTRL, hostctrl); /* read correct value of HSYNC measurement */

result = (gmFC1_Rd (fc1_MEAS_RESULTL) & 0xFFF);

return (result);

}

```

# InGVS

InGVS is the RGB port vertical sync input. The active edge of InGVS is sampled synchronously to InGCLK, and resets line counters used in determining the active data region. The active polarity of InGVS is programmable through the IPCTRL register control bit IPVS\_INV.

# InRed [7:0], InGreen [7:0], InBlue [7:0]

These are the 24-bit RGB data inputs.

# INVADC

INVADC is an output signal provided by the gmFC1 to support horizontal interlacing. If the data source is an analog to digital converter (ADC), INVADC may be used to invert the ADC sampling clock at the end of every field, effectively shifting the sample points by half a clock period.

When the IPCTRL register bit IP\_HINTLC\_EN =1, the gmFC1 will change the state of INVADC after the final pixel of a field is captured (before InGVS). INVADC may be tied directly to the ADC clock driver (e.g. the INV pin of the Philips TDA8752 ADC). Inverting the ADC sampling clock using INVADC may cause the sampling clock to momentarily glitch. The gmFC1 InGClk is internally gated to filter these glitches within approximately 16 fsCLK periods prior to and after a toggled INVADC.

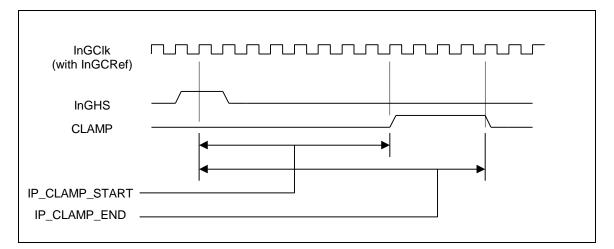

# CLAMP

CLAMP is a gmFC1 output signal provided to aid the input ADC in DC restoration of the source analog RGB signal. The CLAMP pulse has programmable start and end points referenced from the input InGHS signal. The active polarity is also programmable from the host register bit IP\_CLAMP\_INV. CLAMP is programmed to frame a short period within the horizontal back porch. The DC restoration circuit in the ADC then modifies the DC offset value to bring the clamping level to the required voltage. The CLAMP pin is shared with the mode select pin MSBFIRST.

# 5.4 Video (YUV) Input Port Signals

The Video (YUV) Data Input Port signals are active when the gmFC1 is operating with this port selected by the host programmed register bit IP\_RGB\_nYUV. Otherwise, this port is ignored. All Video Input Port signals are provided with internal pull-down resistors.

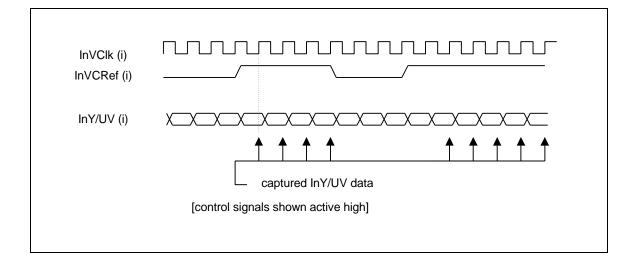

#### InVCLK

InVCLK provides the timing reference for the YUV port signals. The active edge is programmable though the IPCTRL register control bit IPCLK\_INV.

# InVCREF

InVCREF further qualifies InVCLK. InVCREF must be asserted during an active InVCLK edge to validate the InVCLK cycle, i.e., InVCREF can be considered an InVCLK clock enable. In most designs, the CREF signals may be hard-wired to either VCC or GND to validate all clocks. The asserting (active) polarity of InVCREF is programmable through the IPCTRL register control bit IPCREF\_INV.

If the CREF qualifier signals InVCREF / InGCREF are left floating or not connected, the gmFC1 may operate incorrectly. It is recommended that any unused input clock reference signals (InVCREF or InGCREF) be tied either HIGH or LOW. When the clock reference is tied HIGH, program the gmFC1 IPCTRL register bit IPCREF\_INV (Register 05, bit 1) = 1. When the clock reference is tied LOW, program IPCREF\_INV = 0.

Figure 12. Video Input Data Handshaking

# InVHS

InVHS is the YUV port horizontal sync input. The active edge of InVHS resets clock counters used in determining the active data region. The active polarity of InVHS is programmable through the IPCTRL register control bit IPHS\_INV.

# InVVS

InVVS is the YUV port vertical sync input. The active edge of InVVS resets line counters used in determining the active data region. The active polarity of InVVS is programmable through the IPCTRL register control bit IPVS\_INV.

# InY [7:0], InUV [7:0]

These are the 16-bit YUV data inputs.

# 5.5 Graphics / Video Common Port Signals

# INDATAACTIVE

$\overline{\text{INDATAACTIVE}}$  is common to both graphics and video ports and is driven based on the active clock input. The  $\overline{\text{INDATAACTIVE}}$  output signal indicates when the gmFC1 is expecting valid data based on the host programmed active data region registers.

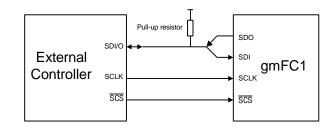

$\overline{\text{INDATAACTIVE}}$  is not predictive. The  $\overline{\text{INDATAACTIVE}}$  pin is physically shared with the  $\overline{\text{IRQ}}$  interrupt pin of the host interface; the IRQ\_OUT\_EN bit in the IRQMASK register controls the function. Note that the output is open-drain, and requires a pull-up resistor.

# InODD

InODD is the odd/even field indicator when operating in vertical interlace mode. It must be valid prior to the first line of active input data. When asserted, InODD indicates the current input field contains odd lines. The active polarity of InODD is programmable through the IPCTRL register control bit IPODD\_INV.

The gmFC1 has the capability to auto-detect odd/even fields in certain graphics interlaced modes. The gmFC1 distinguishes fields by monitoring InGVS and InGHS. If this feature is disabled by setting the IPCTRL register bit EXTGODD\_EN=1, the InODD signal is used to determine the current field state. InODD is provided with an internal pull-down resistor.

# 5.6 Data Output

GENESU

#### 5.6.1 Output Formats

The gmFC1 will produce a Progressive Scan output format if the input format is Progressive Scan.

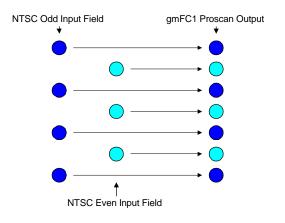

If the input format is vertically interlaced, the gmFC1 may output vertically interlaced data, or it may be configured to perform static mesh de-interlacing and output a Progressive Scan format. Static mesh de-interlacing weaves together alternating odd and even lines of data as illustrated in Figure 13 below.

**Figure 13: Vertical De-Interlacing**

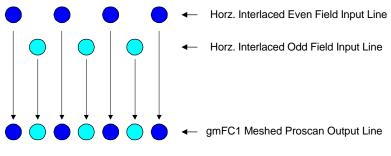

If the input format is horizontally interlaced, the gmFC1 will weave together alternating odd and even pixel data fields, and produce a Progressive Scan output. Horizontal interlacing allows an ADC to effectively sample a signal at twice the maximum ADC clock rate (e.g., a 160 MHz signal may be sampled using a 80 MHz ADC, assuming the full power bandwidth of the ADC is  $\geq$  160 MHz). See Figure 14 below.

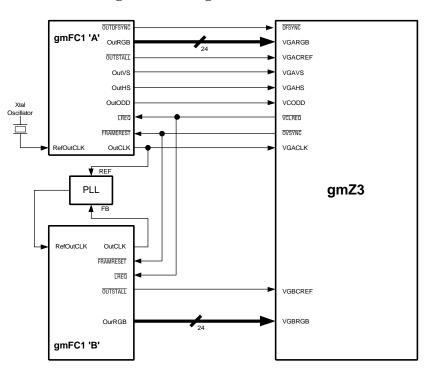

#### 5.6.2 Output Interface Overview

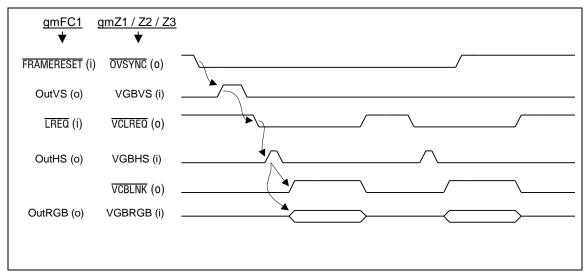

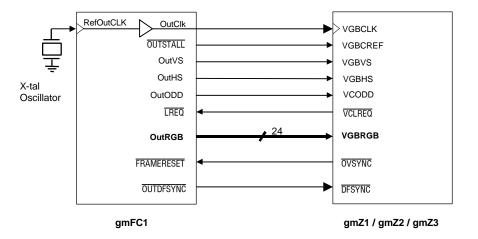

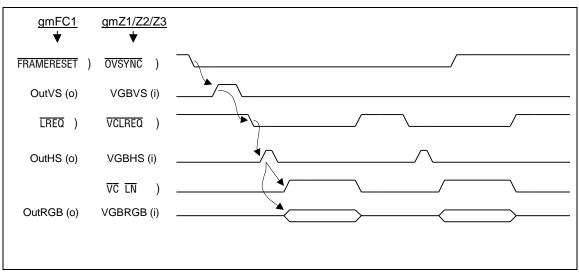

The operational parameters of both the gmFC1 and the Genesis gmZ1/Z2/Z3 zoom scaler are closely related. In Free Run Mode, the gmFC1 depends on the gmZ1/Z2/Z3 to set the output frame rate, and to request data required to maintain the data rate. (In Frame Sync Mode, the gmFC1 input source sets the frame rate.) Output interface handshaking is shown in Figure 15 below. See Figure 16 for interface details.

Figure 15: Output Timing (to gmZ1/2/3)

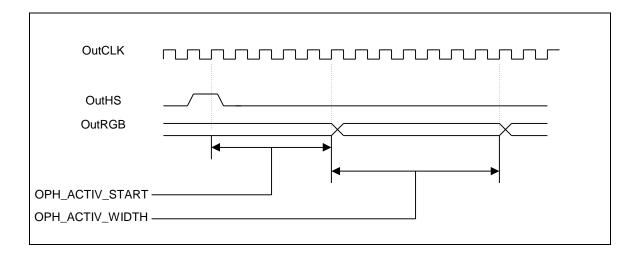

The gmFC1 is programmed to provide active output data a specified number of clock cycles (OPH\_ACTIV\_START) after the gmFC1 asserts OutHS. The gmZ1/Z2/Z3 is programmed to receive active single pixel RGB input data occupying the same active window as the gmFC1 RGB output data. This is achieved by matching the gmFC1 Active Output Window parameters to the gmZ1/Z2/Z3 Active Input Window parameters.

When the gmZ1/Z2/Z3 has completed displaying an image, the gmFC1 must be signaled to queue up data for the next frame. This is accomplished by tying a gmZ1/Z2/Z3 display-side VSYNC signal (ex: OVSYNC) to the gmFC1 FRAMERESET input. This resets the gmFC1's output circuitry, and produces a pulse on the OutVS signal. In response to this the gmZ1/Z2/Z3 asserts  $\overline{VCLREQ}$ , indicating internal line storage is available.  $\overline{VCLREQ}$  is tied to the gmFC1's  $\overline{LREQ}$  pin.

Figure 16: gmFC1 - gmZ1/2/3 Interface

In applications where the gmFC1 must provide data on demand from a source other than the gmZ1 / gmZ2 / gmZ3, the DATAREQ signal may be used. By programming the MISC register control bit OP\_HANDSH = 0, the gmFC1 will slave to requests for data at the DATAREQ input pin and provide data three clock cycles after DATAREQ is asserted. In this mode, the latency to data from DATAREQ (three clock cycles) differs from the gmZ1 / gmZ2 / gmZ3's VCBLNK data latency requirement (two clock cycles). Therefore, in applications where the gmFC1 is interfacing to the gmZ1 / gmZ2 / gmZ3, the gmFC1 control bit OP\_HANDSH must be programmed to '1'. This enables the gmFC1 to provide data a fixed number of clock cycles after asserting OutHS. The gmZ1/Z2/Z3 must be programmed to expect data at the same point.

$\overline{OUTSTALL}$  is used by the gmFC1 to indicate it does not have the requested data available. Because of internal buffering within the gmZ1 / gmZ2 / gmZ3, momentary data transfer stalls are acceptable. If prolonged data transfer stalls occur (ex: because the I/O data rates through the gmFC1 exceed its frame store capabilities) the gmZ1/Z2/Z3 will underflow.

# 5.6.3 Output Active Size