National Semiconductor

# COP680C/COP681C/COP880C/COP881C/ COP980C/COP981C Microcontrollers

## **General Description**

The COP680C/COP681C/COP880C/COP881C/COP980C, and COP981C are members of the COPSTM microcontroller family. They are fully static parts, fabricated using doublemetal silicon gate microCMOS technology. This low cost microcontroller is a complete microcomputer containing all system timing, interrupt logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a variety of applications. Features include an 8-bit memory mapped architecture, MICROWIRE/PLUSTM serial I/O, a 16-bit timer/ counter with capture register and a multi-sourced interrupt. Each I/O pin has software selectable options to adapt the device to the specific application. The part operates over a voltage range of 2.5 to 6.0V. High throughput is achieved with an efficient, regular instruction set operating at a 1 microsecond per instruction rate.

## Features

- Low cost 8-bit microcontroller

- Fully static CMOS

- 1 μs instruction time

- Low current drain

- Low current static HALT mode (Typically < 1  $\mu$ A)

- Single supply operation: 2.5 to 6.0V

- 4096 bytes ROM/128 Bytes RAM

- 16-bit read/write timer operates in a variety of modes

- Timer with 16-bit auto reload register

- 16-bit external event counter

- Timer with 16-bit capture register (selectable edge)

- Multi-source interrupt

- Reset master clear

- External interrupt with selectable edge

- Timer interrupt or capture interrupt

- Software interrupt

- 8-bit stack pointer (stack in RAM)

- Powerful instruction set, most instructions single byte

- BCD arithmetic instructions

- MICROWIRE PLUS™ serial I/O

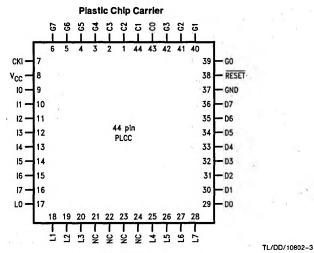

- 44 PLCC, 36 I/O pins

- 40 DIP, 36 I/O pins

- 28 DIP and SO, 24 I/O pins

- Software selectable I/O options (TRI-STATE®, pushpull, weak pull-up)

- Schmitt trigger inputs on Port G

- Temperature ranges: COP98XC/COP98XCH 0°C to 70°C, COP88XC -40°C to +85°C, COP68XC -55°C to +125°C.

- Form factor emulation devices

- Fully supported by Metalink's development systems

# COP980C/COP981C

# Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Subbly voltage (vCC)                            | 7ν                                    |

|-------------------------------------------------|---------------------------------------|

| Voltage at any Pin                              | $-0.3V$ to $V_{CC}$ + 0.3V $_{\odot}$ |

| Total Current into V <sub>CC</sub> Pin (Source) | 50 mA                                 |

Total Current out of GND Pin (Sink)

60 mA

Storage Temperature Range  $-65^{\circ}$ C to  $+140^{\circ}$ C Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

## DC Electrical Characteristics COP980XC; $0^{\circ}C \le T_A \le +70^{\circ}C$ unless otherwise specified

| Parameter                                  | Condition                                                        | Min                                   | Тур   | Max                  | Units    |

|--------------------------------------------|------------------------------------------------------------------|---------------------------------------|-------|----------------------|----------|

| Operating Voltage<br>98XC<br>98XCH         | 90                                                               | 2.3<br>4.0                            |       | 4.0                  | v,       |

| Power Supply Ripple (Note 1)               | Peak to Peak                                                     | 4.0                                   | 3.6   | 0.1 V <sub>CC</sub>  | v        |

| Supply Current                             |                                                                  |                                       |       |                      | 1        |

| CKI = 10 MHz                               | $V_{CC} = 6V$ , tc = 1 $\mu$ s                                   | · · · · · · · · · · · · · · · · · · · |       | 6.0                  | mA       |

| CKI = 4 MHz                                | $V_{CC} = 6V, tc = 2.5 \mu s$                                    |                                       |       | 4.4                  | mA       |

| CKI = 4 MHz                                | $V_{CC} = 4.0V$ , tc = 2.5 $\mu$ s                               |                                       |       | 2.2                  | mA       |

| CKI = 1 MHz                                | $V_{CC} = 4.0V, tc = 10 \mu s$                                   | 1                                     |       | 1.4                  | mA       |

| (Note 2)<br>HALT Current                   | $V_{CC} = 6V_{L}CKI = 0 MHz$                                     |                                       | < 0.7 |                      |          |

| (Note 3)                                   | $V_{CC} = 4.0V, CKI = 0 MHz$<br>$V_{CC} = 4.0V, CKI = 0 MHz$     |                                       | < 0.4 | - 8<br>5             | μА<br>μА |

| Input Levels                               |                                                                  |                                       |       |                      | <u> </u> |

| RESET, CKI                                 |                                                                  |                                       |       |                      |          |

| Logic High                                 |                                                                  | 0.9 V <sub>CC</sub>                   |       |                      | v        |

| Logic Low                                  |                                                                  |                                       |       | 0.1 V <sub>CC</sub>  | v        |

| All Other Inputs                           |                                                                  |                                       |       |                      |          |

| Logic High                                 |                                                                  | 0.7 V <sub>CC</sub>                   |       |                      | V        |

| Logic Low                                  |                                                                  |                                       | -     | 0.2 V <sub>CC</sub>  | V        |

| Hi-Z Input Leakage<br>Input Pullup Current | $V_{CC} = 6.0V$                                                  | - 1.0                                 |       | + 1.0                | μA       |

|                                            | $V_{\rm CC} = 6.0V, V_{\rm IN} = 0V$                             | 40                                    |       |                      | μA<br>V  |

| G Port Input Hysteresis                    |                                                                  |                                       |       | 0.35 V <sub>CC</sub> |          |

| Output Current Levels<br>D Outputs         |                                                                  |                                       |       | 19-                  |          |

| Source                                     | $V_{\rm CC} = 4.5 V, V_{\rm OH} = 3.8 V$                         | -0.4                                  |       | - 10                 | mA       |

|                                            | $V_{CC} = 2.3V, V_{OH} = 1.6V$                                   | -0.2                                  |       | 3. F                 | mA       |

| Sink                                       | $V_{CC} = 4.5V, V_{OL} = 1.0V$                                   | 10                                    |       |                      | mA       |

|                                            | $V_{\rm CC} = 2.3 V, V_{\rm OL} = 0.4 V$                         | 2                                     |       |                      | mA       |

| All Others                                 | V 45V/V 0.0V                                                     | 10                                    |       |                      |          |

| Source (Weak Pull-Up)                      | $V_{CC} = 4.5V, V_{OH} = 3.2V$<br>$V_{CC} = 2.3V, V_{OH} = 1.6V$ | -10<br>-2.5                           |       | -110<br>-33          | μΑ       |

| Source (Push-Pull Mode)                    | $V_{CC} = 4.5V, V_{OH} = 3.8V$                                   | -0.4                                  |       | - 33                 | μA<br>mA |

|                                            | $V_{CC} = 2.3V, V_{OH} = 1.6V$                                   | -0.2                                  |       | all a set            | 110/1    |

| Sink (Push-Pull Mode)                      | $V_{CC} = 4.5V, V_{OL} = 0.4V$                                   | 1.6                                   |       | 12 444               | mA       |

|                                            | $V_{CC} = 2.3V, V_{OL} = 0.4V$                                   | 0.7                                   |       | 100                  | · · · ·  |

| TRI-STATE Leakage                          | $V_{CC} = 6.0V$                                                  | - 1.0                                 |       | + 1.0                | µА       |

| Allowable Sink/Source                      |                                                                  |                                       |       |                      |          |

| Current Per Pin                            |                                                                  |                                       |       |                      |          |

| D Outputs (Sink)                           |                                                                  |                                       |       | 15                   | mA       |

| All Others                                 |                                                                  |                                       |       | 3                    | mA       |

| Maximum Input Current (Note 4)             | Reem Temp                                                        |                                       |       | + 100                | •        |

| Without Latchup (Room Temp)                | Room Temp                                                        |                                       |       | ±100                 | mA       |

| RAM Retention Voltage, Vr<br>(Note 5)      | 500 ns Rise and<br>Fall Time (Min)                               | 2.0                                   |       |                      | v        |

| Input Capacitance                          |                                                                  | 2.0                                   |       | 7                    |          |

|                                            |                                                                  |                                       |       |                      | pF       |

| Load Capacitance on D2                     |                                                                  |                                       |       | 1000                 | pF       |

# COP980C/COP981C

## DC Electrical Characteristics (Continued)

Note 1: Rate of voltage change must be less than 0.5V/ms.

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI Input, CKO open, inputs at rails and outputs open.

Note 3: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations. Test conditions: All inputs tied to V<sub>CC</sub>, L, C and G ports TRI-STATE and tied to ground, all outputs low and tied to ground.

Note 4: Pins G6 and RESET are designed with a high voltage input network for factory testing. These pins allow input voltages greater than  $V_{CC}$  and the pins will have sink current to  $V_{CC}$  when biased at voltages greater than  $V_{CC}$  (the pins do not have source current when biased at a voltage below  $V_{CC}$ ). The effective resistance to  $V_{CC}$  is 750 $\Omega$  (typ). These two pins will not latch up. The voltage at the pins must be limited to less than 14V.

Note 5: To maintain RAM integrity, the voltage must not be dropped or raised instantaneously.

## AC Electrical Characteristics $0^{\circ}C \le T_A \le +70^{\circ}C$ unless otherwise specified

| Parameter                                | Condition                               | Min | Тур | Max  | Units |

|------------------------------------------|-----------------------------------------|-----|-----|------|-------|

| Instruction Cycle Time (tc)              |                                         |     |     |      |       |

| Crystal/Resonator or External            | $V_{CC} \ge 4.0V$                       | 1   |     | DC   | μs    |

| (Div-by 10)                              | $2.3V \le V_{CC} \le 4.0V$              | 2.5 |     | DC   | μs    |

| R/C Oscillator Mode                      | $V_{CC} \ge 4.0V$                       | 3   |     | DC   | μs    |

| (Div-by 10)                              | $2.3V \le V_{CC} \le 4.0V$              | 7.5 |     | DC   | μs    |

| CKI Clock Duty Cycle (Note 6)            | fr = Max                                | 40  |     | 60   | %     |

| Rise Time (Note 6)                       | fr = 10 MHz Ext Clock                   |     |     | 12   | ns    |

| Fall Time (Note 6)                       | fr = 10 MHz Ext Clock                   |     |     | 8    | ns    |

| Inputs                                   |                                         |     |     |      |       |

| <sup>t</sup> SETUP                       | $V_{CC} \ge 4.0V$                       | 200 |     | ]    | ns    |

|                                          | $2.3V \le V_{CC} \le 4.0V$              | 500 |     |      | ns    |

| thold                                    | $V_{CC} \ge 4.0V$                       | 60  |     |      | ns    |

|                                          | $2.3V \le V_{CC} \le 4.0V$              | 150 |     |      | ns    |

| Output Propagation Delay                 | $C_{L} = 100  pF, R_{L} = 2.2  k\Omega$ |     |     |      |       |

| tPD1, tPD0                               |                                         | 1   |     |      |       |

| SO, SK                                   | $V_{CC} \ge 4.0V$                       |     |     | 0.7  | μs    |

|                                          | $2.3V \le V_{CC} \le 4.0V$              | Į   |     | 1.75 | μs    |

| All Others                               | $V_{CC} \ge 4.0V$                       |     |     | 1    | μs    |

| е.,                                      | $2.3V \le V_{\rm CC} \le 4.0V$          |     |     | 2.5  | μs    |

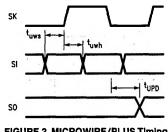

| MICROWIRE™ Setup Time (t <sub>UWS)</sub> |                                         | 20  |     |      | ns    |

| MICROWIRE Hold Time (tUWH)               |                                         | 56  |     |      | ns    |

| MICROWIRE Output                         |                                         |     |     | ł    |       |

| Propagation Delay (t <sub>UPD</sub> )    |                                         |     |     | 220  | ns    |

| Input Pulse Width                        |                                         |     |     |      |       |

| Interrupt Input High Time                |                                         | tc  |     |      |       |

| Interrupt Input Low Time                 |                                         | tc  |     |      |       |

| Timer Input High Time                    |                                         | tc  |     |      |       |

| Timer Input Low Time                     |                                         | tc  |     |      |       |

| Reset Pulse Width                        |                                         | 1.0 |     |      | μs    |

Note 6: Parameter characterized but not production tested.

# COP880C/COP881C

# Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )               | 7V                              |

|-------------------------------------------------|---------------------------------|

| Voltage at any Pin                              | -0.3V to V <sub>CC</sub> + 0.3V |

| Total Current into V <sub>CC</sub> Pin (Source) | 50 mA                           |

Total Current out of GND Pin (Sink)

60 mA

Storage Temperature Range -65°C to + 140°C Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

## DC Electrical Characteristics COP88XC; -40°C ≤ T<sub>A</sub> ≤ +85°C unless otherwise specified

| Parameter                      | Condition                       | Min                 | Тур  | Max                  | Units |

|--------------------------------|---------------------------------|---------------------|------|----------------------|-------|

| Operating Voltage              |                                 | 2.5                 |      | 6.0                  | V     |

| Power Supply Ripple (Note 1)   | Peak to Peak                    |                     |      | 0.1 V <sub>CC</sub>  | V -   |

| Supply Current                 |                                 |                     |      |                      |       |

| CKI = 10 MHz                   | $V_{CC} = 6V$ , tc = 1 $\mu$ s  | -                   |      | 6.0                  | mA    |

| CKI = 4 MHz                    | $V_{CC} = 6V, tc = 2.5 \mu s$   |                     |      | 4.4                  | mA    |

| CKI = 4 MHz                    | $V_{CC} = 4.0V, tc = 2.5 \mu s$ |                     |      | 2.2                  | mA    |

| CKI = 1 MHz                    | $V_{CC} = 4.0V, tc = 10 \mu s$  |                     |      | 1.4                  | mA    |

| (Note 2)                       |                                 |                     |      |                      |       |

| HALT Current                   | $V_{CC} = 6V, CKI = 0 MHz$      |                     | <1   | 10                   | μA    |

| (Note 3)                       | $V_{CC} = 3.5V, CKI = 0 MHz$    |                     | <0.5 | 6                    | μA    |

| Input Levels                   |                                 |                     |      |                      |       |

| RESET, CKI                     |                                 |                     |      |                      |       |

| Logic High                     |                                 | 0.9 V <sub>CC</sub> |      |                      | V     |

| Logic Low                      |                                 |                     |      | 0.1 V <sub>CC</sub>  | v     |

| All Other Inputs               |                                 |                     |      |                      |       |

| Logic High                     |                                 | 0.7 V <sub>CC</sub> |      |                      | l v   |

| Logic Low                      |                                 |                     |      | 0.2 V <sub>CC</sub>  | v     |

| Hi-Z Input Leakage             | $V_{CC} = 6.0V$                 | -2                  |      | +2                   | μA    |

| Input Pullup Current           | $V_{CC} = 6.0V, V_{IN} = 0V$    | -40                 |      | -250                 | μΑ    |

| G Port Input Hysteresis        |                                 |                     |      | 0.35 V <sub>CC</sub> | v     |

| Output Current Levels          |                                 |                     |      |                      |       |

| D Outputs                      |                                 |                     |      | -                    |       |

| Source                         | $V_{CC} = 4.5V, V_{CH} = 3.8V$  | -0.4                |      |                      | mA    |

|                                | $V_{CC} = 2.5V, V_{OH} = 1.8V$  | -0.2                |      |                      | mA    |

| Sink                           | $V_{CC} = 4.5V, V_{OL} = 1.0V$  | 10                  |      |                      | mA    |

|                                | $V_{CC} = 2.5V, V_{OL} = 0.4V$  | 2                   |      |                      | mA    |

| All Others                     | 00 02                           |                     |      |                      |       |

| Source (Weak Pull-Up)          | $V_{CC} = 4.5V_1V_{OH} = 3.2V$  | 10                  |      | 110                  | μA    |

|                                | $V_{CC} = 2.5V, V_{OH} = 1.8V$  | -2.5                |      | -33                  | μA    |

| Source (Push-Pull Mode)        | $V_{CC} = 4.5V, V_{OH} = 3.8V$  | -0.4                |      |                      | mA    |

|                                | $V_{CC} = 2.5V, V_{OH} = 1.8V$  | -0.2                |      |                      |       |

| Sink (Push-Pull Mode)          | $V_{CC} = 4.5V, V_{OL} = 0.4V$  | 1.6                 |      |                      | mA    |

|                                | $V_{CC} = 2.5V, V_{OL} = 0.4V$  | 0.7                 |      |                      | 1     |

| TRI-STATE Leakage              | $V_{CC} = 6.0V$                 | -2.0                |      | + 2.0                | μA    |

| Allowable Sink/Source          |                                 |                     |      |                      |       |

| Current Per Pin                |                                 |                     |      |                      |       |

| D Outputs (Sink)               |                                 | 1 i                 |      | 15                   | mA    |

| All Others                     |                                 |                     |      | 3                    | mA    |

| Maximum Input Current (Note 4) |                                 |                     |      |                      |       |

| Without Latchup (Room Temp)    | Room Temp                       | L                   |      | ± 100                | mA    |

| RAM Retention Voltage, Vr      | 500 ns Rise and                 |                     |      |                      |       |

| (Note 5)                       | Fall Time (Min)                 | 2.0                 |      |                      | V     |

| Input Capacitance              |                                 |                     |      | 7                    | pF    |

| Load Capacitance on D2         | - No                            |                     |      | 1000                 | p۶    |

# COP880C/COP881C

## DC Electrical Characteristics (Continued)

Note 1: Rate of voltage change must be less than 0.5V/ms.

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails and outputs open.

Note 3: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations. Test conditions: All inputs tied to VCC, L, C and G ports TRI-STATE and tied to ground, all outputs low and tied to ground.

Note 4: Pins G6 and RESET are designed with a high voltage input network for factory testing. These pins allow input voltages greater than V<sub>CC</sub> and the pins will have sink current to V<sub>CC</sub> when biased at voltages greater than V<sub>CC</sub> (the pins do not have source current when biased at a voltage below V<sub>CC</sub>). The effective resistance to V<sub>CC</sub> is 750Ω (typ). These two pins will not latch up. The voltage at the pins must be limited to less than 14V. Note 5: To maintain RAM integrity, the voltage must not be dropped or raised instantaneously.

## AC Electrical Characteristics $-40^{\circ}C \le T_A \le +85^{\circ}C$ unless otherwise specified

| Parameter                                | Condition                               | Min  | Тур     | Max  | Units  |

|------------------------------------------|-----------------------------------------|------|---------|------|--------|

| Instruction Cycle Time (tc)              | *                                       |      | (c)     |      |        |

| Crystal/Resonator or External            | $V_{CC} \ge 4.5V$                       | 1    | 1       | DC   | μs     |

| (Div-by 10)                              | $2.5V \le V_{CC} < 4.5V$                | 2.5  |         | DC   | μs     |

| R/C Oscillator Mode                      | $V_{CC} \ge 4.5V$                       | 3    |         | DC   |        |

| (Div-by 10)                              | $2.5V \le V_{\rm CC} < 4.5V$            | 7.5  |         | DC   | μs     |

| CKI Clock Duty Cycle (Note 6)            | fr = Max                                | 40   |         | 60   | %      |

| Rise Time (Note 6)                       | fr = 10 MHz Ext Clock                   |      | 1       | 12   | ns     |

| Fall Time (Note 6)                       | fr = 10 MHz Ext Clock                   | *    |         | 8    | ns     |

| Inputs                                   |                                         |      |         |      |        |

| tSETUP                                   | $V_{CC} \ge 4.5V$                       | 200  |         |      | ns     |

|                                          | $2.5V \leq V_{CC} < 4.5V$               | 500  |         |      | ns     |

| tHOLD                                    | $V_{CC} \ge 4.5V$                       | 60   |         |      | ns     |

|                                          | $2.5V \leq V_{CC} < 4.5V$               | 150  |         |      | ns     |

| Output Propagation Delay                 | $C_{L} = 100  pF, R_{L} = 2.2  k\Omega$ |      |         |      | - 0    |

| tPD1, tPD0                               |                                         |      |         |      |        |

| SO, SK                                   | $V_{CC} \ge 4.5V$                       | - 4- |         | 0.7  | μs     |

|                                          | $2.5V \le V_{CC} \le 4.5V$              |      | <i></i> | 1,75 | μs     |

| All Others                               | $V_{CC} \ge 4.5V$                       |      |         | 1    | μs     |

| -                                        | $2.5V \le V_{CC} < 4.5V$                |      |         | 2.5  | μs     |

| MICROWIRE™ Setup Time (t <sub>UWS)</sub> |                                         | 20   |         |      | ns     |

| MICROWIRE Hold Time (tuwh)               |                                         | 56   |         |      | ns     |

| MICROWIRE Output                         |                                         |      |         |      |        |

| Propagation Delay (t <sub>UPD</sub> )    | 0                                       |      |         | 220  | ns     |

| Input Pulse Width                        |                                         |      |         |      |        |

| Interrupt Input High Time                |                                         | tc   |         |      |        |

| Interrupt Input Low Time                 | - 100-                                  | tc   |         |      | - )( - |

| Timer Input High Time                    |                                         | tc   |         |      |        |

| Timer Input Low Time                     |                                         | tc   |         |      | ÷      |

| Reset Pulse Width                        |                                         | 1.0  |         | -    | μs     |

Note 6: Parameter characterized but not production tested.

## **Timing Diagram**

TL/DD/10802-2

## COP680C/COP681C

# Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications. Supply Voltage (V<sub>CC</sub>) 6V

| Voltage at Any Pin                       | $-0.3V$ to $V_{CC}$ $+$ 0.3V |

|------------------------------------------|------------------------------|

| Total Current into $V_{CC}$ Pin (Source) | 40 mA                        |

Total Current Out of GND Pin (Sink)

48 mA

Storage Temperature Range  $-65^{\circ}$ C to  $+140^{\circ}$ C Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

## **DC Electrical Characteristics** COP68XC: $-55^{\circ}C \le T_A \le +125^{\circ}C$ unless otherwise specified

| Parameter                                                                                                                                                            | Condition                                                                                                                                                                  | Min                                        | Тур  | Max                                        | Units                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|--------------------------------------------|----------------------------|

| Operating Voltage<br>Power Supply Ripple (Note 1)                                                                                                                    | Peak to Peak                                                                                                                                                               | 4.5                                        | . 10 | 5.5<br>0.1 V <sub>CC</sub>                 | v<br>v                     |

| Supply Current (Note 2)<br>CKI = 10 MHz<br>CKI = 4 MHz<br>HALT Current (Note 3)                                                                                      | $V_{CC} = 5.5V, tc = 1 \ \mu s$<br>$V_{CC} = 5.5V, tc = 2.5 \ \mu s$<br>$V_{CC} = 5.5V, CKI = 0 \ MHz$                                                                     |                                            | <10  | 8.0<br>4.4<br>30                           | mA<br>mA<br>μA             |

| Input Levels<br>RESET, CKI<br>Logic High<br>Logic Low<br>All Other Inputs<br>Logic High<br>Logic Low                                                                 |                                                                                                                                                                            | 0.9 V <sub>CC</sub><br>0.7 V <sub>CC</sub> |      | 0.1 V <sub>CC</sub><br>0.2 V <sub>CC</sub> | V<br>V<br>V                |

| Hi-Z Input Leakage<br>Input Pullup Current                                                                                                                           | $V_{CC} = 5.5V$<br>$V_{CC} = 5.5V$ , $V_{IN} = 0V$                                                                                                                         | -5<br>-35                                  |      | + 5<br>- 300                               | μΑ<br>μΑ                   |

| G Port Input Hysteresis                                                                                                                                              |                                                                                                                                                                            |                                            |      | 0.35 V <sub>CC</sub>                       | v                          |

| Output Current Levels<br>D Outputs<br>Source<br>Sink<br>All Others<br>Source (Weak Pull-Up)<br>Source (Push-Pull Mode)<br>Sink (Push-Pull Mode)<br>TRI-STATE Leakage | $V_{CC} = 4.5V, V_{OH} = 3.8V$ $V_{CC} = 4.5V, V_{OL} = 1.0V$ $V_{CC} = 4.5V, V_{OH} = 3.2V$ $V_{CC} = 4.5V, V_{OH} = 3.2V$ $V_{CC} = 4.5V, V_{OL} = 0.4V$ $V_{CC} = 5.5V$ | -0.35<br>9<br>-9<br>-0.35<br>1.4<br>-5.0   |      | - 120<br>+ 5.0                             | mA<br>mA<br>mA<br>mA<br>μA |

| Allowable Sink/Source Current per Pin<br>D Outputs (Sink)<br>All Others                                                                                              |                                                                                                                                                                            | 0                                          |      | 12<br>2.5                                  | mA<br>mA                   |

| Maximum Input Current (Room Temp)<br>without Latchup (Note 4)                                                                                                        | Room Temp                                                                                                                                                                  |                                            |      | ±100                                       | mA                         |

| RAM Retention Voltage, Vr (Note 5)                                                                                                                                   | 500 ns Rise and Fall Time (Min)                                                                                                                                            | 2.5                                        |      |                                            | v                          |

| Input Capacitance                                                                                                                                                    |                                                                                                                                                                            |                                            |      | 7                                          | pF                         |

| Load Capacitance on D2                                                                                                                                               |                                                                                                                                                                            |                                            |      | 1000                                       | pF                         |

Note 1: Rate of voltage change must be less than 0.5V/ms.

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails and outputs open.

Note 3: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations. Test conditions: All inputs tied to V<sub>CC</sub>, L and G ports TRI-STATE and tied to ground, all outputs low and tied to ground.

Note 4: Pins G6 and RESET are designed with a high voltage input network for factory testing. These pins allow input voltages greater than  $V_{CC}$  and the pins will have sink current to  $V_{CC}$  when biased at voltages greater than  $V_{CC}$  (the pins do not have source current when biased at a voltage below  $V_{CC}$ ). The effective resistance to  $V_{CC}$  is 750 $\Omega$  (typical). These two pins will not latch up. The voltage at the pins must be limited to less than 14V.

Note 5: To maintain RAM integrity, the voltage must not be dropped or raised instantaneously.

# COP680C/COP681C

# AC Electrical Characteristics $-55^{\circ}C \le T_A \le +125^{\circ}C$ unless otherwise specified

| Parameter                                                                                                                                                                                         | Condition                                                  | Min                  | Тур | Max           | Units          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----|---------------|----------------|

| Instruction Cycle Time (tc)<br>Ext. or Crystal/Resonant<br>(Div-by 10)                                                                                                                            | V <sub>CC</sub> ≥ 4.5V                                     | 1                    |     | DC            | μs             |

| CKI Clock Duty Cycle<br>(Note 6)<br>Rise Time (Note 6)<br>Fall Time (Note 6)                                                                                                                      | fr = Max<br>fr = 10 MHz Ext Clock<br>fr = 10 MHz Ext Clock | 40<br>St             |     | 60<br>12<br>8 | %<br>ns<br>ns  |

| $\label{eq:microwine} \begin{array}{l} \text{MICROWIRE Setup Time} \ (t_{UWS}) \\ \text{MICROWIRE Hold Time} \ (t_{UWH}) \\ \text{MICROWIRE Output Valid} \\ \text{Time} \ (t_{UPD}) \end{array}$ |                                                            | 20<br>56             |     | 220           | ns<br>ns<br>ns |

| Input Pulse Width<br>Interrupt Input High Time<br>Interrupt Input Low Time<br>Timer Input High Time<br>Timer Input Low Time                                                                       |                                                            | to to<br>to to<br>to |     |               |                |

| Reset Pulse Width                                                                                                                                                                                 |                                                            | 1                    |     |               | μs             |

Note 6: Parameter characterized but not production tested.

1-105

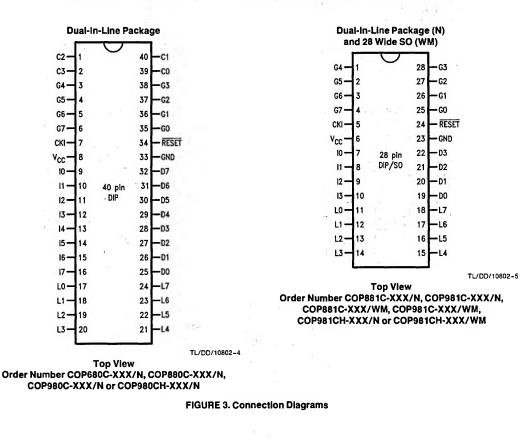

## **Connection Diagrams**

Top View

Order Number COP680C-XXX/V, COP880C-XXX/V, COP980C-XXX/V or COP980CH-XXX/V

## **Pin Descriptions**

V<sub>CC</sub> and GND are the power supply pins.

CKI is the clock input. This can come from an external source, a R/C generated oscillator or a crystal (in conjunction with CKO). See Oscillator description.

RESET is the master reset input. See Reset description.

PORT I is an 8-bit Hi-Z input port. The 28-pin device does not have a full complement of Port I pins. The unavailable pins are not terminated i.e., they are floating. A read operation for these unterminated pins will return unpredictable values. The user must ensure that the software takes this into account by either masking or restricting the accesses to bit operations. The unterminated Port I pins will draw power only when addressed.

PORT L is an 8-bit I/O port.

#### PORT C is a 4-bit I/O port.

Three memory locations are allocated for the L, G and C ports, one each for data register, configuration register and the input pins. Reading bits 4–7 of the C-Configuration register, data register, and input pins returns undefined data.

There are two registers associated with the L and C ports: a data register and a configuration register. Therefore, each L and C I/O bit can be individually configured under software control as shown below:

| Config. | Data | Ports L and C Setup                  |

|---------|------|--------------------------------------|

| 0       | 0    | Hi-Z Input (TRI-STATE Output)        |

| 0       | 1    | Input with Pull-Up (Weak One Output) |

| 1       | 0    | Push-Pull Zero Output                |

| 1       | 1    | Push-Pull One Output                 |

On the 28-pin part, it is recommended that all bits of Port C be configured as outputs.

PORT G is an 8-bit port with 6 I/O pins (G0–G5) and 2 input pins (G6, G7). All eight G-pins have Schmitt Triggers on the inputs.

There are two registers associated with the G port: a data register and a configuration register. Therefore, each G port bit can be individually configured under software control as shown below:

| Config. | Data | Port G Setup                         |

|---------|------|--------------------------------------|

| 0       | 0    | Hi-Z Input (TRI-STATE Output)        |

| 0       | 1    | Input with Pull-Up (Weak One Output) |

| 1       | 0    | Push-Pull Zero Output                |

| 1       | 1    | Push-Pull One Output                 |

Since G6 and G7 are input only pins, any attempt by the user to configure them as outputs by writing a one to the configuration register will be disregarded. Reading the G6 and G7 configuration bits will return zeros. The device will be placed in the HALT mode by writing to the G7 bit in the G-port data register.

Six pins of Port G have alternate features:

G0 INTR (an external interrupt)

G3 TIO (timer/counter input/output)

G4 SO (MICROWIRE serial data output)

G5 SK (MICROWIRE clock I/O)

G6 SI (MICROWIRE serial data input)

G7 CKO crystal oscillator output (selected by mask option) or HALT restart input (general purpose input)

Pins G1 and G2 currently do not have any alternate functions. PORT D is an 8-bit output port that is preset high when RESET goes low. Care must be exercised with the D2 pin operation. At RESET, the external loads on this pin must ensure that the output voltages stay above  $0.9 V_{CC}$  to prevent the chip from entering special modes. Also, keep the external loading on D2 to less than 1000 pF.

## **Functional Description**

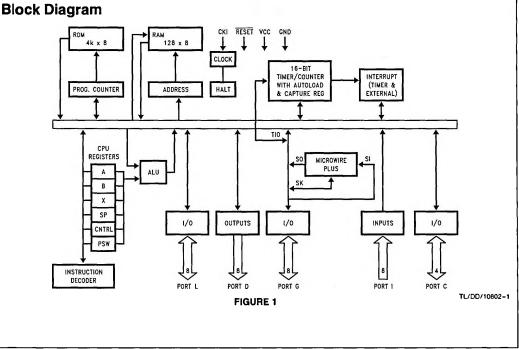

Figure 1 shows the block diagram of the internal architecture. Data paths are illustrated in simplified form to depict how the various logic elements communicate with each other in implementing the instruction set of the device.

#### ALU AND CPU REGISTERS

The ALU can do an 8-bit addition, subtraction, logical or shift operation in one cycle time.

There are five CPU registers:

A is the 8-bit Accumulator register

PU is the upper 7 bits of the program counter (PC)

PL is the lower 8 bits of the program counter (PC)

B is the 8-bit address register, can be auto incremented or decremented.

X is the 8-bit alternate address register, can be incremented or decremented.

SP is the 8-bit stack pointer, points to subroutine stack (in RAM).

B, X and SP registers are mapped into the on chip RAM. The B and X registers are used to address the on chip RAM. The SP register is used to address the stack in RAM during subroutine calls and returns.

#### **PROGRAM MEMORY**

Program memory consists of 4096 bytes of ROM. These bytes may hold program instructions or constant data. The program memory is addressed by the 15-bit program counter (PC). ROM can be indirectly read by the LAID instruction for table lookup.

#### DATA MEMORY

The data memory address space includes on chip RAM, I/O and registers. Data memory is addressed directly by the instruction or indirectly by the B, X and SP registers.

The device has 128 bytes of RAM. Sixteen bytes of RAM are mapped as "registers" that can be loaded immediately, decremented or tested. Three specific registers: B, X and SP are mapped into this space, the other bytes are available for general usage.

The instruction set permits any bit in memory to be set, reset or tested. All I/O and registers (except the A & PC) are memory mapped; therefore, I/O bits and register bits can be directly and individually set, reset and tested. A is not memory mapped, but bit operations can be still performed on it. Note: RAM contents are undefined upon power-up.

#### RESET

The RESET input when pulled low initializes the microcontroller. Initialization will occur whenever the RESET input is pulled low. Upon initialization, the ports L, G and C are placed in the TRI-STATE mode and the Port D is set high. The PC, PSW and CNTRL registers are cleared. The data and configuration registers for Ports L, G and C are cleared.

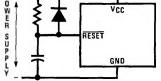

The external RC network shown in Figure 4 should be used to ensure that the RESET pin is held low until the power supply to the chip stabilizes.

# Functional Description (Continued)

TL/DD/10802-6

#### RC ≥ 5X Power Supply Rise Time FIGURE 4. Recommended Reset Circuit

#### **OSCILLATOR CIRCUITS**

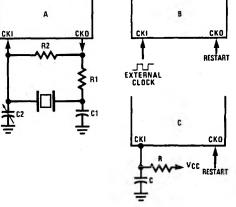

Figure 5 shows the three clock oscillator configurations.

#### A. CRYSTAL OSCILLATOR

The device can be driven by a crystal clock. The crystal network is connected between the pins CKI and CKO.

Table I shows the component values required for various standard crystal values.

#### **B. EXTERNAL OSCILLATOR**

CKI can be driven by an external clock signal. CKO is available as a general purpose input and/or HALT restart control.

#### C. R/C OSCILLATOR

CKI is configured as a single pin RC controlled Schmitt trigger oscillator. CKO is available as a general purpose input and/or HALT restart control.

TL/DD/10802-7

#### FIGURE 5. Crystal and R-C Connection Diagrams

#### **OSCILLATOR MASK OPTIONS**

The device can be driven by clock inputs between DC and 10  $\ensuremath{\mathsf{MHz}}$  .

| TABLE I. Cry | stal Oscillator | Configuration | . TA = 25°C |

|--------------|-----------------|---------------|-------------|

|              |                 |               |             |

| <b>R1</b><br>(kΩ) | R2<br>(MΩ) | C1<br>(pF) | C2<br>(pF) | CKI Freq<br>(MHz) | Conditions      |

|-------------------|------------|------------|------------|-------------------|-----------------|

| 0                 | 1          | 30         | 30-36      | 10                | $V_{CC} = 5V$   |

| 0                 | 1          | 30         | 30-36      | 4                 | $V_{CC} = 2.5V$ |

| 5.6               | 1          | 200        | 100-150    | 0.455             | $V_{CC} = 5V$   |

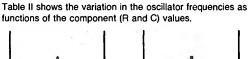

#### TABLE II. RC Oscillator Configuration, T<sub>A</sub> = 25°C

| <b>Β</b><br>(kΩ) | C<br>(pF) | CKI Freq.<br>(MHz) | Instr. Cycle<br>(μs) | Conditions    |

|------------------|-----------|--------------------|----------------------|---------------|

| 3.3              | 82        | 2.2 to 2.7         | 3.7 to 4.6           | $V_{CC} = 5V$ |

| 5.6              | 100       | 1.1 to 1.3         | 7.4 to 9.0           | $V_{CC} = 5V$ |

| 6.8              | 100       | 0.9 to 1.1         | 8.8 to 10.8          | $V_{CC} = 5V$ |

Note: (R/C Oscillator Configuration):  $3k \le R \le 200k$ ,  $50 \text{ pF} \le C \le 200 \text{ pF}$ .

## Functional Description (Continued)

The device has three mask options for configuring the clock input. The CKI and CKO pins are automatically configured upon selecting a particular option.

- Crystal (CKI/10); CKO for crystal configuration

- External (CKI/10); CKO available as G7 input

- R/C (CKI/10); CKO available as G7 input

G7 can be used either as a general purpose input or as a control input to continue from the HALT mode.

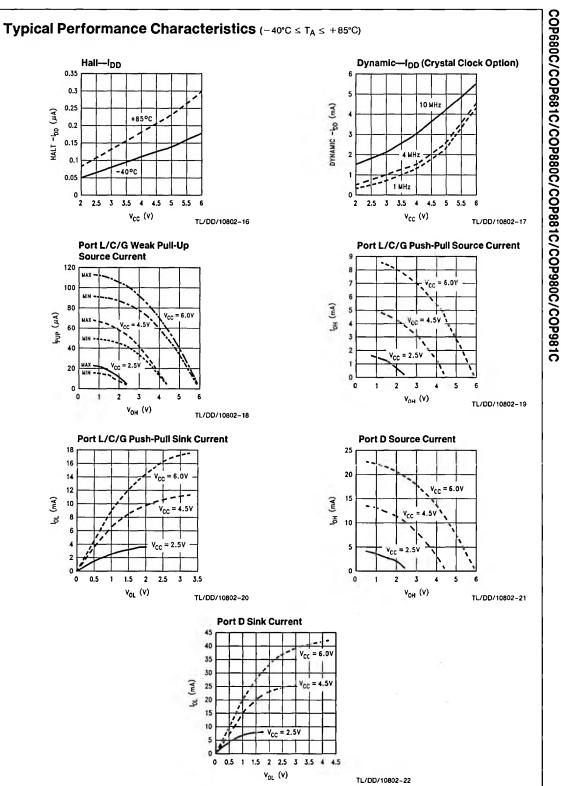

#### CURRENT DRAIN

The total current drain of the chip depends on:

- 1) Oscillator operating mode-I1

- 2) Internal switching current-I2

- 3) Internal leakage current-I3

- 4) Output source current-I4

Thus the total current drain, It is given as

To reduce the total current drain, each of the above components must be minimum.

Operating with a crystal network will draw more current than an external square-wave. The R/C mode will draw the most. Switching current, governed by the equation below, can be reduced by lowering voltage and frequency. Leakage current can be reduced by lowering voltage and temperature. The other two items can be reduced by carefully designing the end-user's system.

$12 = C \times V \times f$

Where

- C = equivalent capacitance of the chip.

- V = operating voltage

f = CKI frequency

#### HALT MODE

The device supports a power saving mode of operation: HALT. The controller is placed in the HALT mode by setting the G7 data bit, alternatively the user can stop the clock input. In the HALT mode all internal processor activities including the clock oscillator are stopped. The fully static architecture freezes the state of the controller and retains all information until continuing. In the HALT mode, power requirements are minimal as it draws only leakage currents and output current. The applied voltage (V<sub>CC</sub>) may be decreased down to Vr (minimum RAM retention voltage) without altering the state of the machine.

There are two ways to exit the HALT mode: via the RESET or by the CKO pin. A low on the RESET line reinitializes the microcontroller and starts executing from the address 0000H. A low to high transition on the CKO pin (only if the external or R/C clock option selected) causes the microcontroller to continue with no reinitialization from the address following the HALT instruction. This also resets the G7 data bit.

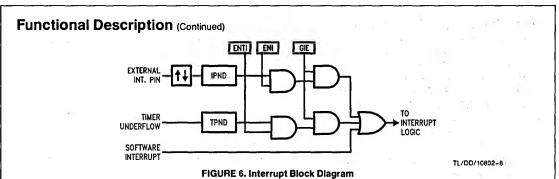

#### INTERRUPTS

There are three interrupt sources, as shown below.

A maskable interrupt on external G0 input (positive or negative edge sensitive under software control)

A maskable interrupt on timer underflow or timer capture

A non-maskable software/error interrupt on opcode zero

#### **INTERRUPT CONTROL**

The GIE (global interrupt enable) bit enables the interrupt function. This is used in conjunction with ENI and ENTI to select one or both of the interrupt sources. This bit is reset when interrupt is acknowledged.

ENI and ENTI bits select external and timer interrupt respectively. Thus the user can select either or both sources to interrupt the microcontroller when GIE is enabled.

IEDG selects the external interrupt edge (0 = rising edge, 1 = falling edge). The user can get an interrupt on both rising and falling edges by toggling the state of IEDG bit after each interrupt.

IPND and TPND bits signal which interrupt is pending. After interrupt is acknowledged, the user can check these two bits to determine which interrupt is pending. This permits the interrupts to be prioritized under software. The pending flags have to be cleared by the user. Setting the GIE bit high inside the interrupt subroutine allows nested interrupts.

The software interrupt does not reset the GIE bit. This means that the controller can be interrupted by other interrupt sources while servicing the software interrupt.

#### INTERRUPT PROCESSING

The interrupt, once acknowledged, puches the program counter (PC) onto the stack and the stack pointer (SP) is decremented twice. The Global Interrupt Enable (GIE) bit is reset to disable further interrupts. The microcontroller then vectors to the address 00FFH and resumes execution from that address. This process takes 7 cycles to complete. At the end of the interrupt subroutine, any of the following three instructions return the processor back to the main program: RET, RETSK or RETI. Either one of the three instructions will pop the stack into the program counter (PC). The stack pointer is then incremented twice. The RETI instruction additionally sets the GIE bit to re-enable further interrupts.

Any of the three instructions can be used to return from a hardware interrupt subroutine. The RETSK instruction should be used when returning from a software interrupt subroutine to avoid entering an infinite loop.

#### **DETECTION OF ILLEGAL CONDITIONS**

The device contains a hardware mechanism that allows it to detect illegal conditions which may occur from coding errors, noise and 'brown out' voltage drop situations. Specifically it detects cases of executing out of undefined ROM area and unbalanced stack situations.

Reading an undefined ROM location returns 00 (hexadecimal) as its contents. The opcode for a software interrupt is also '00'. Thus a program accessing undefined ROM will cause a software interrupt.

Reading an undefined RAM location returns an FF (hexadecimal). The subroutine stack grows down for each subroutine call. By initializing the stack pointer to the top of RAM, the first unbalanced return instruction will cause the stack pointer to address undefined RAM. As a result the program will attempt to execute from FFFF (hexadecimal), which is an undefined ROM location and will trigger a software interrupt.

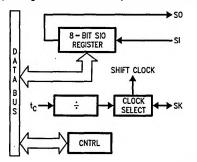

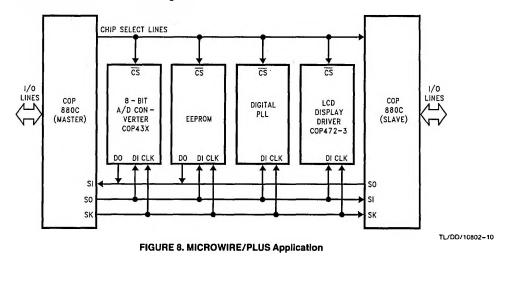

#### MICROWIRE/PLUSTM

MICROWIRE/PLUS is a serial synchronous bidirectional communications interface. The MICROWIRE/PLUS capability enables the device to interface with any of National Semiconductor's MICROWIRE peripherals (i.e. A/D converters, display drivers, EEPROMS, etc.) and with other microcontrollers which support the MICROWIRE/PLUS interface. It consists of an 8-bit serial shift register (SIO) with serial data input (SI), serial data output (SO) and serial shift clock (SK). *Figure 7* shows the block diagram of the MICRO-WIRE/PLUS interface.

The shift clock can be selected from either an internal source or an external source. Operating the MICROWIRE/ PLUS interface with the internal clock source is called the Master mode of operation. Similarly, operating the MICRO-WIRE/PLUS interface with an external shift clock is called the Slave mode of operation.

The CNTRL register is used to configure and control the MICROWIRE/PLUS mode. To use the MICROWIRE/PLUS, the MSEL bit in the CNTRL register is set to one. The SK clock rate is selected by the two bits, SL0 and SL1, in the CNTRL register. Table III details the different clock rates that may be selected.

|     | TABLE | . III           |

|-----|-------|-----------------|

| SL1 | SL0   | SK Cycle Time   |

| 0   | 0     | 2t <sub>C</sub> |

| 0   | 1     | 4t <sub>C</sub> |

| 1   | ×     | 8t <sub>C</sub> |

where,

t<sub>C</sub> is the instruction cycle clock.

#### **MICROWIRE/PLUS OPERATION**

Setting the BUSY bit in the PSW register causes the MI-CROWIRE/PLUS arrangement to start shifting the data. It gets reset when eight data bits have been shifted. The user may reset the BUSY bit by software to allow less than 8 bits to shift. The devoce may enter the MICROWIRE/PLUS mode either as a Master or as a Slave. *Figure 8* shows how two COP880C microcontrollers and several peripherals may be interconnected using the MICROWIRE/PLUS arrangement.

#### Master MICROWIRE/PLUS Operation

In the MICROWIRE/PLUS Master mode of operation the shift clock (SK) is generated internally. The MICROWIRE/ PLUS Master always initiates all data exchanges. (See *Figure 8*). The MSEL bit in the CNTRL register must be set to enable the SO and SK functions onto the G Port. The SO and SK pins must also be selected as outputs by setting appropriate bits in the Port G configuration register. Table IV summarizes the bit settings required for Master mode of operation.

#### SLAVE MICROWIRE/PLUS OPERATION

In the MICROWIRE/PLUS Slave mode of operation the SK clock is generated by an external source. Setting the MSEL bit in the CNTRL register enables the SO and SK functions onto the G Port. The SK pin must be selected as an input and the SO pin is selected as an output pin by appropriately setting up the Port G configuration register. Table IV summarizes the settings required to enter the Slave mode of operation.

The user must set the BUSY flag immediately upon entering the Slave mode. This will ensure that all data bits sent by the Master will be shifted properly. After eight clock pulses the BUSY flag will be cleared and the sequence may be repeated. (See *Figure 8.*)

# Functional Description (Continued)

| G4<br>Config.<br>Bit | G5<br>Config.<br>Bit | G4<br>Fun. | G5<br>Fun. | G6<br>Fun. | Operation        |

|----------------------|----------------------|------------|------------|------------|------------------|

| 1                    | 1                    | so         | Int. SK    | SI         | MICROWIRE Master |

| 0                    | 1                    | TRI-STATE  | Int. SK    | SI         | MICROWIRE Master |

| 1                    | 0                    | SO         | Ext. SK    | SI         | MICROWIRE Slave  |

| 0                    | 0                    | TRI-STATE  | Ext. SK    | SI         | MICROWIRE Slave  |

TABLE IV

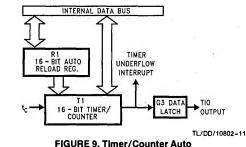

#### **TIMER/COUNTER**

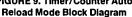

The device has a powerful 16-bit timer with an associated 16-bit register enabling them to perform extensive timer functions. The timer T1 and its register R1 are each organized as two 8-bit read/write registers. Control bits in the register CNTRL allow the timer to be started and stopped under software control. The timer-register pair can be operated in one of three possible modes. Table V details various timer operating modes and their requisite control settings.

TL/DD/10802-9

FIGURE 7. MICROWIRE/PLUS Block Diagram

#### MODE 1. TIMER WITH AUTO-LOAD REGISTER

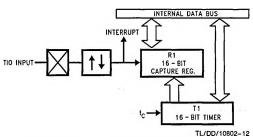

In this mode of operation, the timer T1 counts down at the instruction cycle rate. Upon underflow the value in the register R1 gets automatically reloaded into the timer which continues to count down. The timer underflow can be programmed to interrupt the microcontroller. A bit in the control register CNTRL enables the TIO (G3) pin to toggle upon timer underflows. This allow the generation of square-wave outputs or pulse width modulated outputs under software control. (See *Figure 9*.)

#### **MODE 2. EXTERNAL COUNTER**

In this mode, the timer T1 becomes a 16-bit external event counter. The counter counts down upon an edge on the TIO pin. Control bits in the register CNTRL program the counter to decrement either on a positive edge or on a negative edge. Upon underflow the contents of the register R1 are automatically copied into the counter. The underflow can also be programmed to generate an interrupt. (See *Figure 9*)

#### MODE 3. TIMER WITH CAPTURE REGISTER

Timer T1 can be used to precisely measure external frequencies or events in this mode of operation. The timer T1 counts down at the instruction cycle rate. Upon the occurrence of a specified edge on the TIO pin the contents of the timer T1 are copied into the register R1. Bits in the control register CNTRL allow the trigger edge to be specified either as a positive edge or as a negative edge. In this mode the user can elect to be interrupted on the specified trigger edge. (See *Figure 10*.)

|                      | TABLE V. Timer Operating Modes        |                 |                       |  |  |  |  |  |  |  |

|----------------------|---------------------------------------|-----------------|-----------------------|--|--|--|--|--|--|--|

| CNTRL<br>Bits<br>765 | Operation Mode                        | T Interrupt     | Timer<br>Counts<br>On |  |  |  |  |  |  |  |

| 000                  | External Counter W/Auto-Load Reg.     | Timer Underflow | TIO Pos. Edge         |  |  |  |  |  |  |  |

| 001                  | External Counter W/Auto-Load Reg.     | Timer Underflow | TIO Neg. Edge         |  |  |  |  |  |  |  |

| 010                  | Not Allowed                           | Not Allowed     | Not Allowed           |  |  |  |  |  |  |  |

| 011                  | Not Allowed                           | Not Allowed     | Not Allowed           |  |  |  |  |  |  |  |

| 100                  | Timer W/Auto-Load Reg.                | Timer Underflow | tc                    |  |  |  |  |  |  |  |

| 101                  | Timer W/Auto-Load Reg./Toggle TIO Out | Timer Underflow | tc                    |  |  |  |  |  |  |  |

| 110                  | Timer W/Capture Register              | TIO Pos. Edge   | tc                    |  |  |  |  |  |  |  |

| 111                  | Timer W/Capture Register              | TIO Neg. Edge   | tc                    |  |  |  |  |  |  |  |

FIGURE 10. Timer Capture Mode Block Diagram

#### TIMER PWM APPLICATION

Figure 11 shows how a minimal component D/A converter can be built out of the Timer-Register pair in the Auto-Reload mode. The timer is placed in the "Timer with auto reload" mode and the TIO pin is selected as the timer output. At the outset the TIO pin is set high, the timer T1 holds the on time and the register R1 holds the signal off time. Setting TRUN bit starts the timer which counts down at the instruction cycle rate. The underflow toggles the TIO output and copies the off time into the timer, which continues to run. By alternately loading in the on time and the off time at each successive interrupt a PWM frequency can be easily generated.

## **Control Registers**

#### CNTRL REGISTER (ADDRESS X'00EE)

The Timer and MICROWIRE/PLUS control register contains the following bits:

| SL1 & 3 | SL0 S  | elect t                                                                 | he MICR    | OWIRE/     | PLUS c    | lock di  | vide-by |  |  |

|---------|--------|-------------------------------------------------------------------------|------------|------------|-----------|----------|---------|--|--|

| IEDG    | E      | xterna                                                                  | l interrup | t edge p   | olarity s | elect    |         |  |  |

|         | (      | ) = ris                                                                 | ing edge   | o, 1 = fa  | lling edg | je)      |         |  |  |

| MSEL    | _      | inable<br>K                                                             | MICROV     | VIRE/PL    | US fund   | tions    | SO and  |  |  |

| TRUN    |        | Start/Stop the Timer/Counter (1 = run, 0 = stop)                        |            |            |           |          |         |  |  |

| тСЗ     |        | Timer input edge polarity select (0 = rising<br>edge, 1 = falling edge) |            |            |           |          |         |  |  |

| TC2     | S      | elects                                                                  | the capt   | ure mod    | 9         |          |         |  |  |

| TC1     | S      | elects                                                                  | the time   | r mode     |           |          |         |  |  |

| TC1     | TC2    | тсз                                                                     | TRUN       | MSEL       | IEDG      | SL1      | SL0     |  |  |

| BIT 7   |        |                                                                         |            |            |           |          | BIT 0   |  |  |

| PSW R   | EGIST  | ER (Al                                                                  | DDRESS     | X'00EF)    |           |          |         |  |  |

| The PS  | SW reg | ister co                                                                | ontains th | ne followi | ing sele  | ct bits: |         |  |  |

| GIE     | Globa  | ıl interr                                                               | upt enab   | le         |           |          |         |  |  |

| ENI     | Exter  | nal inte                                                                | rrupt ena  | able       |           |          |         |  |  |

| BUSY    | MICR   | OWIRE                                                                   | E/PLUS I   | busy shif  | ting      |          |         |  |  |

| IPND    | Exter  | nal inte                                                                | rrupt per  | nding      |           |          |         |  |  |

| ENTI    | Timer  | interru                                                                 | ipt enabl  | e          |           |          |         |  |  |

| TPND    | Timer  | interru                                                                 | pt pendi   | ng         |           |          |         |  |  |

| С       | Carry  | Flag                                                                    |            |            |           |          |         |  |  |

| HC Half carry Flag |  |

|--------------------|--|

|--------------------|--|

| нс    | С | TPND | ENTI | IPND | BUSY | ENI | GIE   |

|-------|---|------|------|------|------|-----|-------|

| Bit 7 |   |      |      | _    |      |     | Bit 0 |

## **Addressing Modes**

#### **REGISTER INDIRECT**

This is the "normal" mode of addressing. The operand is the memory addressed by the B register or X register.

#### DIRECT

The instruction contains an 8-bit address field that directly points to the data memory for the operand.

#### IMMEDIATE

The instruction contains an 8-bit immediate field as the operand.

#### **REGISTER INDIRECT** (AUTO INCREMENT AND DECREMENT)

This is a register indirect mode that automatically increments or decrements the B or X register after executing the instruction.

#### RELATIVE

This mode is used for the JP instruction, the instruction field is added to the program counter to get the new program location. JP has a range of from -31 to +32 to allow a one byte relative jump (JP + 1 is implemented by a NOP instruction). There are no 'pages' when using JP, all 15 bits of PC are used.

## **Memory Map**

All RAM, ports and registers (except A and PC) are mapped into data memory address space.

| Address  | Contents                                      |

|----------|-----------------------------------------------|

| 00 to 6F | On Chip RAM Bytes                             |

| 70 to 7F | Unused RAM Address Space (Reads as all Ones   |

| 80 to BF | Expansion Space for future use                |

| C0 to CF | Expansion Space for I/O and Registers         |

| D0 to DF | On Chip I/O and Registers                     |

| D0       | Port L Data Register                          |

| D1       | Port L Configuration Register                 |

| D2       | Port L Input Pins (Read Only)                 |

| D3       | Reserved for Port L                           |

| D4       | Port G Data Register                          |

| D5       | Port G Configuration Register                 |

| D6       | Port G Input Pins (Read Only)                 |

| D7       | Port I Input Pins (Read Only)                 |

| D8       | Port C Data Register                          |

| D9       | Port C Configuration Register                 |

| DA       | Port C Input Pins (Read Only)                 |

| DB       | Reserved for Port C                           |

| DC       | Port D Data Register                          |

| DD-DF    | Reserved for Port D                           |

| E0 to EF | On Chip Functions and Registers               |

| E0-E7    | Reserved for Future Parts                     |

| E8       | Reserved                                      |

| E9       | MICROWIRE/PLUS Shift Register                 |

| EA       | Timer Lower Byte                              |

| EB       | Timer Upper Byte                              |

| EC       | Timer Autoload Register Lower Byte            |

| ED       | Timer Autoload Register Upper Byte            |

| EE       | CNTRL Control Register                        |

|          | PSW Register                                  |

| EF       |                                               |

|          | On Chip RAM Mapped as Registers               |

|          | On Chip RAM Mapped as Registers<br>X Register |

| F0 to FF |                                               |

Reading unused memory locations below 7FH will return all ones. Reading other unused memory locations will return undefined data.

# Instruction Set

| REG      | ISTER AND SYMBOL DEFINITIONS                      |                                                                   |

|----------|---------------------------------------------------|-------------------------------------------------------------------|

| Regi     | sters                                             | Symbols                                                           |

| Α        | 8-bit Accumulator register                        | [B] Memory indirectly addressed by B register                     |

| в        | 8-bit Address register                            | [X] Memory indirectly addressed by X register                     |

| х        | 8-bit Address register                            | Mem Direct address memory or [B]                                  |

| SP       | 8-bit Stack pointer register                      | Meml Direct address memory or [B] or Immediate data               |

| PC       | 15-bit Program counter register                   | Imm 8-bit Immediate data                                          |

| PU<br>PL | upper 7 bits of PC<br>lower 8 bits of PC          | Reg Register memory: addresses F0 to FF (Includes B, X<br>and SP) |

| C        | 1-bit of PSW register for carry                   | Bit Bit number (0 to 7)                                           |

| HC       | Half Carry                                        | ← Loaded with                                                     |

| GIE      | 1-bit of PSW register for global interrupt enable | ←→ Exchanged with                                                 |

|          | Instru                                            | uction Set                                                        |

|          | ADD                                               |                                                                   |

| ADD    | add                          | A 🔶 A + Memi                                                      |

|--------|------------------------------|-------------------------------------------------------------------|

| ADC    | add with carry               | A ← A + MemI + C, C ← Carry                                       |

|        |                              | HC ← Half Carry                                                   |

| SUBC   | subtract with carry          | A ← A + Memi + C, C ← Carry                                       |

| 3000   | Subtract with carry          | HC $\leftarrow$ Half Carry                                        |

|        |                              |                                                                   |

| AND    | Logical AND                  | A - A and Memi                                                    |

| OR     | Logical OR                   | A 🔶 A or Memi                                                     |

| XOR    | Logical Exclusive-OR         | A 🔶 A xor Memi                                                    |

| IFEQ   | IF equal                     | Compare A and Meml, Do next if A = Meml                           |

| IFGT   | IF greater than              | Compare A and Meml, Do next if A > Meml                           |

| IFBNE  | IF B not equal               | Do next if lower 4 bits of B ≠ Imm                                |

| DRSZ   | Decrement Reg. ,skip if zero | Reg <- Reg - 1, skip if Reg goes to 0                             |

| SBIT   | Set bit                      | 1 to bit,                                                         |

| 0011   | Serbit                       |                                                                   |

|        |                              | Mem (bit = 0 to 7 immediate)                                      |

| RBIT   | Reset bit                    | 0 to bit,                                                         |

|        |                              | Mem                                                               |

| IFBIT  | lf bit                       | If bit,                                                           |

|        |                              | Mem is true, do next instr.                                       |

| X      | Exchange A with memory       | A ←→ Mem                                                          |

| LDA    |                              | A ← Memi                                                          |

|        | Load A with memory           |                                                                   |

| LD mem | Load Direct memory Immed.    | Mem 🔶 Imm                                                         |

| LD Reg | Load Register memory Immed.  | Reg ← Imm                                                         |

| х      | Exchange A with memory [B]   | $A \longleftrightarrow [B] (B \leftarrow B \pm 1)$                |

| x      | Exchange A with memory [X]   | $A \longleftrightarrow [X]  (X \leftarrow X \pm 1)$               |

|        | Load A with memory [B]       | $A \leftarrow [B]  (B \leftarrow B \pm 1)$                        |

| LDA    | Load A with memory [X]       | $A \leftarrow [X]$ $(X \leftarrow X \pm 1)$                       |

| LDM    |                              |                                                                   |

|        | Load Memory Immediate        | [B] ← Imm (B ← B±1)                                               |

| CLRA   | Clear A                      | A ← 0                                                             |

| INCA   | Increment A                  | A 🖛 A + 1                                                         |

| DECA   | Decrement A                  | A ← A - 1                                                         |

| LAID   | Load A indirect from ROM     | A - ROM(PU,A)                                                     |

| DCORA  | DECIMAL CORRECT A            | A ← BCD correction (follows ADC, SUBC)                            |

| RRCA   | ROTATE A RIGHT THRU C        | $C \rightarrow A7 \rightarrow \dots \rightarrow A0 \rightarrow C$ |

|        |                              |                                                                   |

| SWAPA  | Swap nibbles of A            | $A7A4 \leftrightarrow A3A0$                                       |

| SC     | Set C                        | C ← 1, HC ← 1                                                     |

| RC     | Reset C                      | $C \leftarrow 0, HC \leftarrow 0$                                 |

| IFC    | If C                         | If C is true, do next instruction                                 |

| IFNC - | If not C                     | If C is not true, do next instruction                             |

| JMPL   | Jump absolute long           | PC ← ii (ii = 15 bits, 0 to 32k)                                  |

| JMP    | Jump absolute                | PC110 $\leftarrow$ i (i = 12 bits)                                |

| JP     | •                            | $PC \leftarrow PC + r(ris - 31 to + 32, not 1)$                   |

| -      | Jump relative short          |                                                                   |

| JSRL   | Jump subroutine long         | [SP] ← PL,[SP-1] ← PU,SP-2,PC ← ii                                |

| JSR    | Jump subroutine              | [SP] ← PL,[SP-1] ← PU,SP-2,PC11 0 ← i                             |

| JID    | Jump indirect                | PL ← ROM(PU,A)                                                    |

| RET    | Return from subroutine       | SP+2,PL ← [SP],PU ← [SP-1]                                        |

| RETSK  | Return and Skip              | SP+2,PL ← [SP],PU ← [SP-1],Skip next instruction                  |

| RETI   | Return from Interrupt        | SP+2,PL ← [SP],PU ← [SP-1],GIE ← 1                                |

| INTR   | Generate an interrupt        | $[SP] \leftarrow PL[SP-1] \leftarrow PU,SP-2,PC \leftarrow OFF$   |

| NOP    | No operation                 | $PC \leftarrow PC + 1$                                            |

| NOF    |                              |                                                                   |

| OPC | ODEL             |                  | 0                |                  |                  | 10               | 6                |                  | s 3-0            |                  | -                | ~                | 0                |                  |                  |                  |

|-----|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|     | R<br>0           | + 2 1            | + 3 5            | + 4 3            | + 5 4            | + 6 5            | + 7 6            | + 8 +            | 8<br>6<br>+      | - 10 9           | - 11 A           | - 12 B           | +13 C            | + 14 D           | +15 E            | + 16 F           |