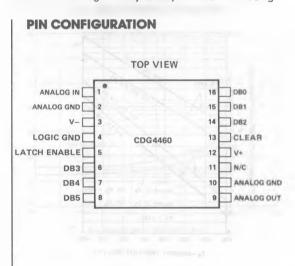

# 6-BIT VIDEO FREQUENCY DIGITAL CONTROLLED ATTENUATOR

### **ORDERING INFORMATION**

16-Pin Ceramic Package

CDG4460J

### **FEATURES**

- Data Latch

- Attenuation Range of 0 to 15.75dB

- Precise Attenuation, Selectable in 0.25dB steps

- Wide Frequency Range, up to 40MHz

- Wide Power Supply Range, ±6.0 to ±15V

- Lower Power Consumption, 0.5µW typ. with ±15V Power Supplies

### DESCRIPTION

CDG4460J remote controlled Video Attenuators feature Integrated Circuits with high OFF Isolation Lateral D-MOS FETs and low-power CMOS logic with data latches. CMOS/D-MOS ICs are mounted on ceramic substrates along with precision, trimmed resistors. A feature of this circuit is the ability to latch in the attenuator setting for easy microprocessor interfacing.

### **APPLICATIONS**

- Video Attenuation

- Wide Band Amplifier Gain Control

- Variable Burst Generation

- IF Amplifier Attenuation

- Frequency Synthesizers

### NOTE

All devices contain diodes to protect logic inputs against damage due to high static voltages or electric fields; however, it is advised that precautions be taken not to exceed maximum recommended logic or analog input voltages. All unused logic inputs must be connected to logic ground.

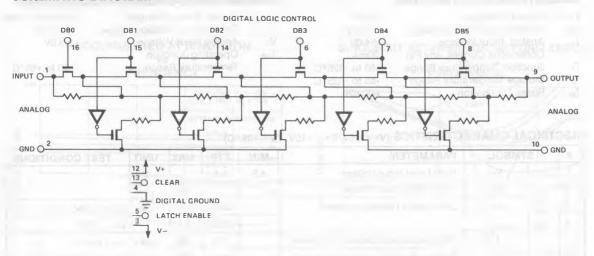

### **SCHEMATIC DIAGRAM**

### ATTENUATOR SETTING TABLE

Note: Examples only. Added attenuation can be set to any value between 0 and 15.75dB in 0.25dB steps.

| ADDED ATTENUATION | DATA BIT #—LOGIC SETTING |     |     |     |     |     |  |  |  |

|-------------------|--------------------------|-----|-----|-----|-----|-----|--|--|--|

| (dB)              | DB0                      | DB1 | DB2 | DB3 | DB4 | DB5 |  |  |  |

| 0                 | 0                        | 0   | 0   | 0   | 0   | 0   |  |  |  |

| 0.25              | 1                        | 0   | 0   | 0   | 0   | 0   |  |  |  |

| 0.50              | 0                        | 1   | 0   | 0   | 0   | 0   |  |  |  |

| 1.00              | 0                        | 0   | 1   | 0   | 0   | 0   |  |  |  |

| 2.00              | 0                        | 0   | 0   | 1   | 0   | 0   |  |  |  |

| 4.00              | 0                        | 0   | 0   | 0   | 1   | 0   |  |  |  |

| 8.00              | 0                        | 0   | 0   | 0   | 0   | 1   |  |  |  |

### **EXAMPLES OF OTHER ATTENUATION SETTINGS**

| 0.75  | 1 | 1 | 0 | 0 | 0 | 0 |

|-------|---|---|---|---|---|---|

| 1.75  | 1 | 1 | 1 | 0 | 0 | 0 |

| 3.75  | 1 | 1 | 1 | 1 | 0 | 0 |

| 7.75  | 1 | 1 | 1 | 1 | 1 | 0 |

| 15.25 | 1 | 0 | 1 | 1 | 1 | 1 |

| 15.75 | 1 | 1 | 1 | 1 | 1 | 1 |

### **ABSOLUTE MAXIMUM RATINGS**

| V-, V+ | Supply Voltages             | ±20V          |

|--------|-----------------------------|---------------|

| VIN    | Control Input Voltage Range | V- to V+      |

| VA     | Analog Input Voltage        | ±4.0V         |

| 1      | Continuous Current, any Pin | 20mA          |

| $T_J$  | Junction Temperature Range  | -55 to +125°C |

| Ta     | Storage Temperature Range   | -55 to +125°C |

| $P_D$  | Power Dissipation           | 600mW         |

|        |                             |               |

### **RECOMMENDED OPERATING CONDITIONS**

| RECO   | MIMENDED OPERATING C        | DUDITION2     |

|--------|-----------------------------|---------------|

| V-, V+ | Supply Voltage Ranges       | ±6.0V to ±15V |

| VIN    | Control Input Voltage Range | 0 to +5V      |

| VA     | Analog Input Voltage        | ±3.0V         |

| TOP    | Operating Junction          |               |

|        | Temperature Range           | -40 to +85°C  |

# ELECTRICAL CHARACTERISTICS (V-=-15V, V+=+15V, TA=+25°C)

| #  | S                  | SYMBOL PARAMETER                                                 |                                       | PARAMETER            |                 | TYP     | MAX  | UNIT | TEST CONDITIONS                                                   |

|----|--------------------|------------------------------------------------------------------|---------------------------------------|----------------------|-----------------|---------|------|------|-------------------------------------------------------------------|

| 1  |                    | VIH                                                              | High Level Input Voltage              |                      | 4.5             | 3.4     |      | ٧    |                                                                   |

| 2  | 2                  | VIL                                                              | Low Level Input Voltage               |                      |                 | and her | 1.0  | I LE |                                                                   |

| 3  | ATI                | IIN                                                              | Logic Input Le                        | ut Leakage Current   | Verific         | 0.01    | 0.1  | μΑ   | V <sub>IN</sub> = +5.0V                                           |

| 4  | ST                 |                                                                  |                                       |                      |                 | 0.02    | 0.1  |      | V <sub>IN</sub> = +15V                                            |

| 5  | PENN               | 1-                                                               | Negative Supp                         | ly Quiescent Current |                 | -0.5    | -100 | μΑ   | V <sub>IN</sub> = 0 or V+                                         |

| 6  | I+ Positive Supply |                                                                  | y Quiescent Current                   |                      | 0.5             | 100     |      |      |                                                                   |

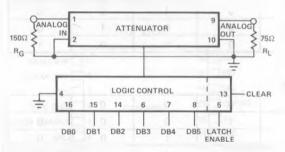

| 7  | U                  | 200                                                              | Insertion Loss                        |                      | ani             | 6.0     |      | dB   | $R_G = 150 \Omega$ , $R_L = 75 \Omega$<br>Attenuation Setting=0dE |

| 8  | Z                  | tpD                                                              | Propagation                           | Data to Attn. Set    | and a town or a | 140     | 250  | nS   | V <sub>IN</sub> = 5.0V                                            |

| 9  | N                  | t <sub>PD</sub> Propagation Delay  t <sub>S</sub> Set Up Time, D |                                       | Clear to Attn. Reset |                 | 100     | 220  | 110  | Control of the Control                                            |

| 10 | DY                 | ts                                                               | Set Up Time, Data to Latch Enable     |                      | 150             |         |      | nS   | (63)                                                              |

| 11 | g e                | tн                                                               | Hold Time<br>Latch Enable to Data OFF |                      | 150             |         |      | nS   |                                                                   |

### **FUNCTIONAL BLOCK DIAGRAM**

### **NOTES:**

- Analog Input Ground (pin 2) and Analog Output Ground (pin 10) must be connected to a common point.

- Logic Ground (pin 4) must be isolated from Analog Ground (pins 2 & 10).

### **TRUTH TABLE**

| LATCH<br>ENABLE | CLEAR | ATTENUATOR                                 |

|-----------------|-------|--------------------------------------------|

| 0               | 0     | Holds data pattern already set.            |

| x               | 1     | Sets all data bits high-max. attenuation   |

| 1               | 0     | Latch transparent, attenuation per setting |

x = don't care, Logic '0'  $\leq$  1.0V, Logic '1'  $\geq$  4.5V

### LATCH DATA

If Clear is High (Logic '1' on pin 13) all Data Bits are set to logic '1' for maximum attenuation.

If Latch Enable is High (logic '1' on pin 5) then Latch is transparent.

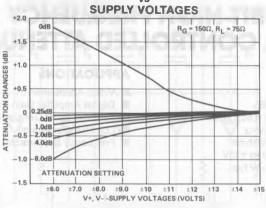

### TYPICAL PERFORMANCE CHARACTERISTICS (TA = +25°C)

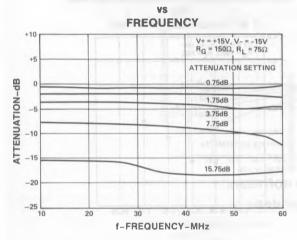

### **ACCUMULATED ATTENUATION**

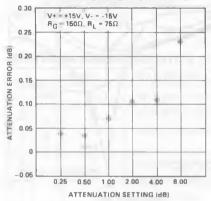

### SINGLE-BIT ATTENUATION SETTING ERROR

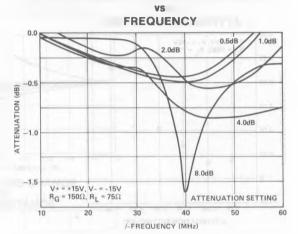

### SINGLE-BIT ATTENUATION CHANGE

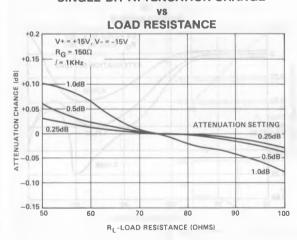

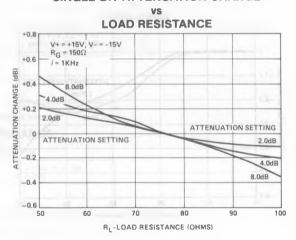

### SINGLE-BIT ATTENUATION CHANGE

NOTE— Attenuation settings are normalized to exclude insertion loss in all curves.

# TYPICAL PERFORMANCE CHARACTERISTICS (TA = +25°C)

SINGLE-BIT ATTENUATION ERROR

ATTENUATION SETTING

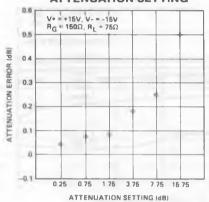

**ACCUMULATED ATTENUATION ERROR**

ATTENUATION SETTING

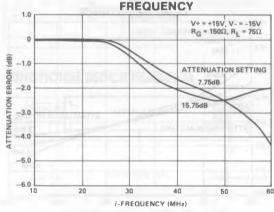

**ACCUMULATED ATTENUATION ERROR**

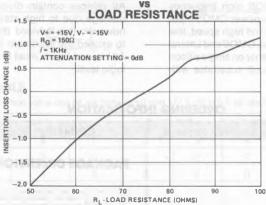

VS

# ACCUMULATED ATTENUATION ERROR

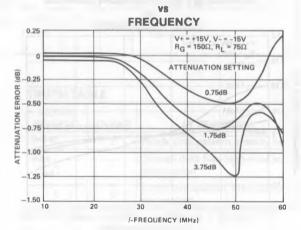

# TYPICAL PERFORMANCE CHARACTERISTICS (T<sub>A</sub> = +25°C)

# SINGLE-BIT ATTENUATION CHANGES

### **INSERTION LOSS CHANGE**

# INPUT IMPEDANCE VS FREQUENCY 180 V+ = +15V, V- = -15V RL = 75Ω 140 ATTENUATION SETTING = 0dB 100 60 40

20

10

/-FREQUENCY (MHz)

40