## Quad Sine-Wave Clock Buffer With LDO

Check for Samples: CDC3S04

### **FEATURES**

- 1:4 Low-Jitter Clock Buffer

- Single-Ended Sine-Wave Clock Input and Outputs

- Ultralow Phase Noise and Standby Current

- Individual Clock Request Inputs for Each Output

- On-Chip Low-Dropout Output (LDO) for Low-Noise TCXO Supply

- Serial I<sup>2</sup>C Interface (Compatible With High-Speed Mode, 3.4 Mbit/s)

- 1.8-V Device Power Supply

- Wide Temperature Range, –40°C to 85°C

- ESD Protection: 2 KV HBM, 750 V CDM, and 100 V MM

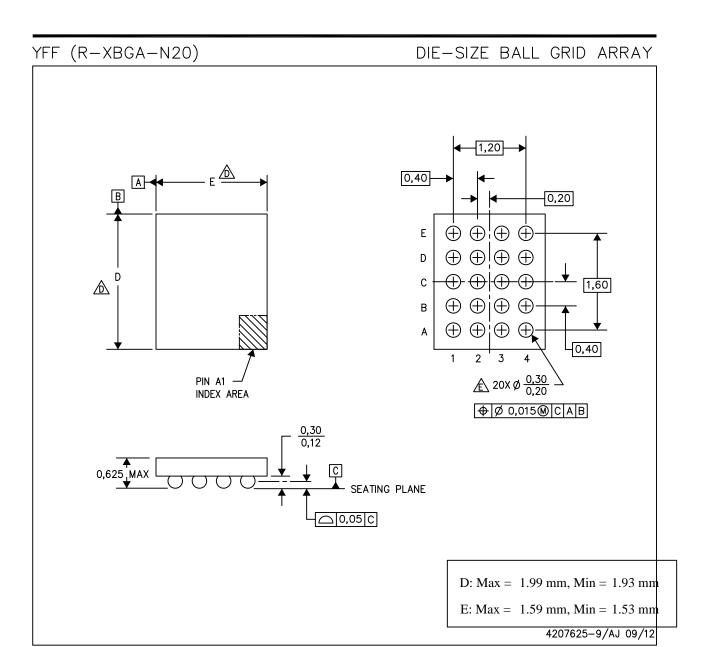

- Small 20-Pin Chip-Scale Package: 0.4-mm

Pitch WCSP (1.6 mm x 2 mm)

### **APPLICATIONS**

- Cellular Phones

- Smart Phones

- Mobile Handsets

- Portable Systems

- Wireless Modems Including GPS, WLAN, W-BT, D-TV, DVB-H, FM Radio, WiMAX, and System Clock

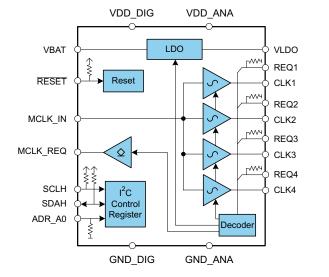

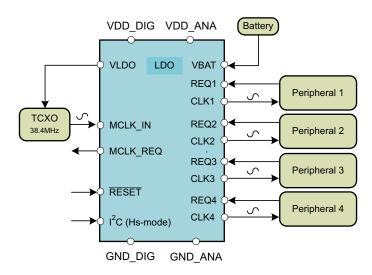

### DESCRIPTION

The CDC3S04 is a four-channel low-power low-jitter sine-wave clock buffer. It can be used to buffer a single master clock to multiple peripherals. The four sine-wave outputs (CLK1–CLK4) are designed for minimal channel-to-channel skew and ultralow additive output jitter.

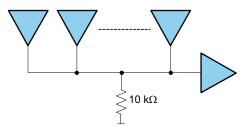

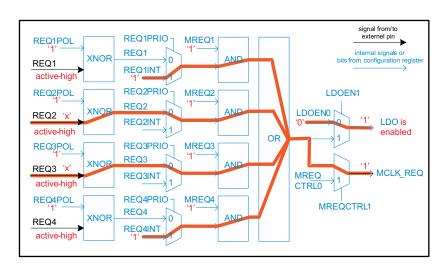

Each output has its own clock request inputs which enables the dedicated clock output. These clock requests are active-high (can also be changed to be active-low via I<sup>2</sup>C), and an output signal is generated that can be sent back to the master clock to request the clock (MCLK\_REQ). MCKL\_REQ is an open-source output and supports the wired-OR function (default mode). It needs an external pulldown resistor. MCKL\_REQ can be changed to wired-AND or push-pull functionality via I<sup>2</sup>C.

The CDC3S04 also provides an I<sup>2</sup>C interface (Hsmode) that can be used to enable or disable the outputs, select the polarity of the REQ inputs, and allow control of internal decoding.

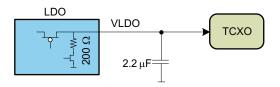

The CDC3S04 features an on-chip high-performance LDO that accepts voltages from 2.3 V to 5.5 V and outputs a 1.8-V supply. This 1.8-V supply can be used to power an external 1.8-V TCXO. It can be enabled or disabled for power saving at the TCXO.

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## **DESCRIPTION (CONTINUED)**

A low signal at the  $\overline{\text{RESET}}$  input switches the outputs CLK1 and CLK4 into the default state. In this <u>configur</u>ation, CLK1 and CLK4 are ON (see <u>Table 1</u>); the remaining device function is not affected. Also, the RESET input provides a glitch filter which rejects spikes of typical 300 ns on the RESET line to preserve false reset. A complete device reset to the default condition can be initiated by a power-up cycle of  $V_{DD\ DIG}$ .

The CDC3S04 operates from two 1.8-V supplies. There is a core supply (VDD\_DIG/GND\_DIG) for the core logic and a low-noise analog supply (VDD\_ANA/GND\_ANA) for the sine-wave outputs. The CDC3S04 is designed for sequence-less power up. Both supply voltages may be applied in any order.

The CDC3S04 is offered in a 0.4-mm pitch WCSP package (1.6 mm  $\times$  2 mm) and is optimized for low standby current (0.5  $\mu$ A). It is characterized for operation from  $-40^{\circ}$ C to 85°C.

### **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| NAME         | BALL NO. | TYPE         | FUNCTION                                                                                                                                                                                                                                  |

|--------------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR_A0       | D4       | Input        | Selectable address bit A0 of slave-address register; internal 500-kΩ pulldown resistor                                                                                                                                                    |

| CLK1         | A4       | Output       | Clock output 1                                                                                                                                                                                                                            |

| CLK2         | A2       | Output       | Clock output 2                                                                                                                                                                                                                            |

| CLK3         | C4       | Output       | Clock output 3                                                                                                                                                                                                                            |

| CLK4         | C2       | Output       | Clock output 4                                                                                                                                                                                                                            |

| GND_ANA      | B4       | Ground       | Ground for sine-wave buffer                                                                                                                                                                                                               |

| GND_DIG      | D2       | Ground       | Ground for core logic                                                                                                                                                                                                                     |

| MCLK_IN      | B1       | Input        | Master clock input                                                                                                                                                                                                                        |

| MCLK_RE<br>Q | D3       | Output       | Clock request to the master clock source; active-high; open-source output for wired-OR connection (default condition). Can be changed to push-pull output or wired-AND output via I <sup>2</sup> C.                                       |

| REQ1         | А3       | Input        | Clock request from peripheral 1; internal 500-kΩ pulldown resistor                                                                                                                                                                        |

| REQ2         | A1       | Input        | Clock request from peripheral 2; internal 500-kΩ pulldown resistor                                                                                                                                                                        |

| REQ3         | C3       | Input        | Clock request from peripheral 3; internal 500-kΩ pulldown resistor                                                                                                                                                                        |

| REQ4         | C1       | Input        | Clock request from peripheral 4; internal 500-kΩ pulldown resistor                                                                                                                                                                        |

| RESET        | B2       | Input        | Peripheral reset signal provided by application processor. The signal is active-low and switches CLK1 and CLK4 outputs to ON (see Table 1). On-chip LDO is enabled. Internal 1-M $\Omega$ pullup resistor and 300-ns (typ) glitch filter. |

| SCLH         | E4       | Input        | $I^2C$ clock input – Hs-mode. Internal 1-M $\Omega$ pullup resistor                                                                                                                                                                       |

| SDAH         | E3       | Input/output | I <sup>2</sup> C data input/output – Hs-mode. Internal 1-MΩ pullup resistor                                                                                                                                                               |

| VBAT         | E2       | Power        | Supply pin to internal LDO                                                                                                                                                                                                                |

| VDD_ANA      | В3       | Power        | 1.8-V power supply for sine-wave buffer                                                                                                                                                                                                   |

| VDD_DIG      | D1       | Power        | 1.8-V power supply for core logic. Power up of VDD_DIG resets the whole device to the default condition.                                                                                                                                  |

| VLDO         | E1       | Output       | 1.8-V supply for external TCXO; LDO is enabled if RESET (default mode) or REQx is active. LDO is not enabled if only VBAT is on.                                                                                                          |

Product Folder Links : CDC3S04

Copyright © 2009-2012, Texas Instruments Incorporated

#### **FUNCTION SELECTION TABLES**

Table 1. Reset and Request (REQx) Conditions for Clock Outputs (1)

| RESET <sup>(2)</sup> | PRIORITY BIT <sup>(3)</sup> | CLK1                  | CLK2                  | CLK3                  | CLK4                  |

|----------------------|-----------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0                    | 0                           | On                    | Controlled by REQ2    | Controlled by REQ3    | 05                    |

| 0                    | 1                           | On                    | Controlled by REQ2INT | Controlled by REQ3INT | On                    |

| 4                    | 0                           | Controlled by REQ1    | Controlled by REQ2    | Controlled by REQ3    | Controlled by REQ4    |

| '                    | 1                           | Controlled by REQ1INT | Controlled by REQ2INT | Controlled by REQ3INT | Controlled by REQ4INT |

## Table 2. Request Signal Condition for Clock Outputs (1)

| REQ-Signals (2) | REQx<br>(REQ1/2/3/4) | CLKx<br>(CLK1/2/3/4) | MCLK_REQ                   | LDO <sup>(3)</sup>         |

|-----------------|----------------------|----------------------|----------------------------|----------------------------|

| Active-low      | 0                    | Clock                | High                       | On                         |

|                 | 1                    | Disabled to high     | Low (if all REQx are high) | Off (if all REQx are high) |

| A ations binds  | 0                    | Disabled to high (4) | Low (if all REQx are low)  | Off (if all REQx are low)  |

| Active-high     | 1                    | Clock <sup>(4)</sup> | High                       | On                         |

Shaded cells show the default setting after power up.

The LDO is controlled by an on-chip decoder, but can also be SW controlled (see Table 3, Byte 2, Bits 4-5).

### **POWER GROUPS**

| NAME    | DESCRIPTION                                                                                                                                                                                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT    | Supply pin for LDO provided by main battery. LDO is not working if only VBAT is on.                                                                                                                                                                                                     |

| VLDO    | 1.8-V low-drop output voltage for external TCXO. LDO is enabled if VBAT and VDD_DIG are on and REQx or RESET is active (see Table 2).                                                                                                                                                   |

| VDD_DIG | 1.8-V power supply for core logic and I <sup>2</sup> C logic. VDD_DIG must be supplied for correct device operation. Power up of VDD_DIG resets the whole device to the default condition.                                                                                              |

| VDD_ANA | 1.8-V power supply for sine-wave buffers. For correct sine-wave buffer function, all three power supplies (VBAT, $V_{DD\_DIG}$ and $V_{DD\_ANA}$ ) must be on. But, $V_{DD\_ANA}$ can be switched on and off at any time. If off, the sine-wave outputs are switched to high-impedance. |

### POWER-UP SEQUENCE

The CDC3S04 is designed for sequence-less power up. VBAT,  $V_{DD\_DIG}$ , and  $V_{DD\_ANA}$  may be applied in any order. Recommended power-on sequence is VBAT first, followed by V<sub>DD DIG</sub> and V<sub>DD ANA</sub>. Recommended poweroff sequence is in reverse order.

Product Folder Links: CDC3S04

<sup>(1)</sup> Shaded cells show the default setting after power up.

(2) RESET resets REQ1PRIO/REQ4PRIO and REQ1INT/REQ4INT bits to their default values (CLK1/4 is ON) but does not change the remaining internal SW bits. During RESET, any I<sup>2</sup>C operation is blocked until RESET is deactivated. A minimum pulse duration of 500 ns must be applied to activate RESET (the internal glitch-filter suppresses spikes of typical 300 ns).

Priority bit defines if the external control pins (HW controlled) or the SW bits (SW controlled) have priority. It can be set in the configuration register, Byte 2, Bits 0-3.

Polarity of REQ1, REQ2, REQ3, and REQ4 are register-configurable via I<sup>2</sup>C (see Table 3, Byte 0, Bits 0–3). Default setting is active-

CLK1 and CLK4 are ON after device power up (default condition). CLK2 and CLK3 are controlled by external REQ2 and REQ3, respectively.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                             |                                         | VALUE                          | UNIT |

|-----------------------------|-----------------------------------------|--------------------------------|------|

| $V_{DD\_ANA} \ V_{DD\_DIG}$ | Supply voltage range                    | -0.5 to 2.5                    | V    |

| $V_{BAT}$                   | Battery supply voltage range            | -0.5 to 6.5                    | ٧    |

| VI                          | Input voltage range <sup>(2) (3)</sup>  | -0.5 to V <sub>DD</sub> + 0.5  | V    |

| Vo                          | Output voltage range <sup>(2)</sup> (3) | -0.5 to V <sub>DD</sub> + 0.5  | V    |

| $V_{LDO}$                   | Output voltage range                    | -0.5 to V <sub>BAT</sub> + 0.5 | ٧    |

|                             | Input current $(V_I < 0, V_I > V_{DD})$ | ±20                            | mA   |

| Io                          | Continuous output current               | ±20                            | mA   |

| I <sub>LDO</sub>            | Continuous output current               | ±20                            | mA   |

| T <sub>stg</sub>            | Storage temperature range               | -65 to 150                     | °C   |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

- (2) The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- (3) The input V<sub>I</sub> and output V<sub>O</sub> positive voltages are limited to the absolute maximum rating for V<sub>DD</sub> = 2.5 V.

## THERMAL CHARACTERISTICS for 20-pin WCSP (YFF)(1)

|                | PARAMETER                               | AIRFLOW<br>(Ifm) | 20-PIN<br>WCSP | UNIT |

|----------------|-----------------------------------------|------------------|----------------|------|

|                |                                         | 0                | 71             |      |

| $T_{JA}$       | Thermal resistance, junction-to-ambient | 200              | 62             | °C/W |

|                |                                         | 400              | 59             |      |

| $T_{JC}$       | Thermal resistance, junction-to- case   | _                | 17.5           | °C/W |

| $T_{JB}$       | Thermal resistance, junction-to-board   | _                | 20.5           | °C/W |

| T <sub>J</sub> | Maximum junction temperature            | _                | 125            | °C   |

<sup>(1)</sup> The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

## RECOMMENDED OPERATING CONDITIONS

|                  |                                                              | MIN                      | NOM | MAX                | UNIT     |

|------------------|--------------------------------------------------------------|--------------------------|-----|--------------------|----------|

| $V_{DD\_ANA}$    | Device supply voltage                                        | 1.65                     | 1.8 | 1.95               | V        |

| $V_{DD\_DIG}$    | Device supply voltage                                        | 1.65                     | 1.8 | 1.95               | V        |

| V <sub>IH</sub>  | Input voltage ADD AO DEOV DESET                              | 0.65 V <sub>DD_DIG</sub> |     |                    | V        |

| $V_{IL}$         | Input voltage ADR_A0, REQx, RESET                            |                          |     | $0.35~V_{DD\_DIG}$ | V        |

| V <sub>IS</sub>  | Sine-wave input voltage – MCLK_IN; ac-coupled amplitude      | 0.5                      |     | 1.2                | $V_{PP}$ |

| C <sub>L</sub>   | Sine-wave output load <sup>(1)</sup>                         |                          | 10  | 30                 | pF       |

| C <sub>OUT</sub> | LDO output capacitance (stabilize the internal control loop) | 0.8                      | 2.2 |                    | μF       |

| T <sub>A</sub>   | Operating free-air temperature                               | -40                      |     | 85                 | °C       |

|                  |                                                              |                          |     |                    |          |

(1) 10 pF is the typical load-driving capability. The drive capability can be optimized for 30 pF by the I<sup>2</sup>C register (Byte 3, Bits 7–4).

Product Folder Links: CDC3S04

### **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER            |                                                                             | TEST CONDITIONS                                                                                                                                                      |                | MIN                        | TYP  | MAX               | UNIT |

|----------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------|------|-------------------|------|

|                      |                                                                             | OVERALL PARAM                                                                                                                                                        | METER          | 1                          |      |                   |      |

|                      |                                                                             | V <sub>BAT</sub> = 5.5 V;                                                                                                                                            | Off (no REQ)   |                            | 0.1  | 0.2               |      |

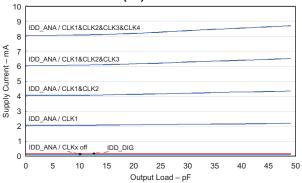

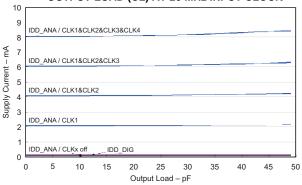

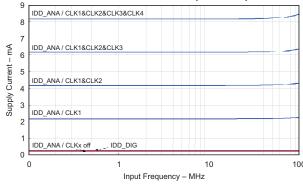

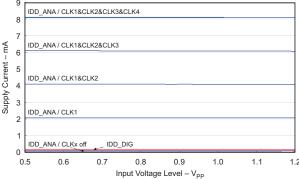

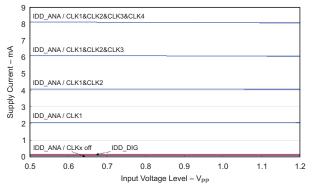

| I <sub>DD_ANA</sub>  | Analog supply current <sup>(1)</sup> (seeFigure 8 through Figure 12)        |                                                                                                                                                                      |                |                            | 2    | 2.6               | mA   |

| I <sub>DD_DIG</sub>  | Digital supply current<br>(see Figure 8 through<br>Figure 12)               | $V_{BAT} = 5.5 \text{ V}; V_{DD\_DIG} = 1$<br>= off;<br>LDO = off; $V_{IS} = 1 \text{ Vpp}; f_{M}$<br>MHz;<br>$C_{L} = 10 \text{ pF}; R_{L} = 10 \text{ k}\Omega$    | _              |                            |      | 0.1               | mA   |

| I <sub>SB</sub>      | Standby current                                                             | V <sub>BAT</sub> = 5.5 V; V <sub>DD_DIG</sub> /V <sub>DL</sub><br>All outputs disabled (no in<br>off; no REQ; RESET is ina<br>idle mode); includes 1-MΩ<br>and RESET |                | 0.5                        | 10   | μΑ                |      |

| f <sub>MCLK_IN</sub> | Input frequency                                                             | Sine wave                                                                                                                                                            |                | 0.01                       | 38.4 | 52                | MHz  |

| V <sub>OH</sub>      | MCLK_REQ high-level output voltage                                          | $\begin{array}{c} \text{Wired-OR output;} \\ \text{IOH} = -2 \text{ mA; V}_{\text{DD}\_\text{DIG}} = 1.65 \text{ V (See} \\ \text{Figure 3.)} \end{array}$           |                | V <sub>DD_DIG</sub> – 0.45 |      |                   | V    |

|                      | Push-pull output; $V_{DD\_DIG} = 1.65 \text{ V}$ , $I_{OH} = -2 \text{ mA}$ |                                                                                                                                                                      |                |                            |      |                   |      |

| V                    | MCLK_REQ low-level output                                                   | Wired-AND output; $I_{OL} = 2 \text{ mA}$<br>$V_{DD\_DIG} = 1.65 \text{ V}$                                                                                          |                |                            |      | 0.45              | V    |

| V <sub>OL</sub>      | voltage                                                                     | Push-pull output; $V_{DD\_DIG} = 1.65 \text{ V}$ , $I_{OL} = 2 \text{ mA}$                                                                                           |                | 0.45                       |      | 0.45              | ٧    |

| $V_{IK}$             | LVCMOS input voltage                                                        | $V_{DD\_DIG} = 1.65 \text{ V}; I_I = -18 \text{ mA}$                                                                                                                 |                |                            |      | -1.2              | >    |

| L.                   | Input current ADR_A0, REQx (500-kΩ pulldown)                                | _                                                                                                                                                                    |                |                            |      | 6                 | μA   |

| I <sub>IH</sub>      | Input current $\overline{\text{RESET}}$ (1-M $\Omega$ pullup)               | $V_I = V_{DD\_DIG}$ ; $V_{DD\_DIG} = 1$ .                                                                                                                            | .90 V          |                            |      | 2                 | μΛ   |

| L.                   | Input current ADR_A0, REQx (500- $k\Omega$ pulldown)                        | V <sub>I</sub> = 0 V; V <sub>DD DIG</sub> = 1.95 V                                                                                                                   | /              |                            |      | -2                | μA   |

| I <sub>IL</sub>      | Input current $\overline{\text{RESET}}$ (1-M $\Omega$ pullup)               | V  = 0 V, VDD_DIG = 1.33 V                                                                                                                                           |                |                            |      | -3                | μΛ   |

| C <sub>I</sub>       | Input capacitance ADR_A0, REQx, RESET                                       | $V_I = 0 \text{ V or } V_{DD\_DIG}$                                                                                                                                  |                |                            | 3    |                   | pF   |

|                      |                                                                             | SDAH/SCLH PARAM                                                                                                                                                      | METER (Hs-Mode | e)                         |      |                   |      |

| $V_{IK}$             | SCLH/SDAH input clamp voltage                                               | $V_{DD\_DIG} = 1.65 \text{ V}; I_I = -18$                                                                                                                            | mA             |                            |      | -1.2              | V    |

| I <sub>I</sub>       | SCLH/SDAH input current                                                     | 0.1 V <sub>DD_DIG</sub> < V <sub>I</sub> < 0.9 V <sub>DD_DIG</sub>                                                                                                   |                |                            |      | 10                | μΑ   |

| $V_{IH}$             | SDA/SCL input high voltage                                                  |                                                                                                                                                                      |                | 0.7 V <sub>DD_DIG</sub>    |      |                   | V    |

| $V_{IL}$             | SDAH/SCLH input low voltage                                                 |                                                                                                                                                                      |                |                            |      | $0.3~V_{DD\_DIG}$ | V    |

| $V_{hys}$            | Hysteresis of Schmitt-trigger inputs                                        |                                                                                                                                                                      |                | 0.1 V <sub>DD_DIG</sub>    |      |                   | V    |

| $V_{OL}$             | SDAH low-level output voltage                                               | $I_{OL} = 3 \text{ mA}, V_{DD\_DIG} = 1.6$                                                                                                                           | 5 V            |                            |      | $0.2~V_{DD\_DIG}$ | V    |

| Cı —                 | SCLH input capacitance                                                      | $V_I = 0 \text{ V or } V_I = V_{DD\_DIG}^{(3)}$                                                                                                                      |                |                            | 3    | 5                 | pF   |

| Cı                   | SDAH input capacitance                                                      | $V_I = 0 \text{ V or } V_I = V_{DD\_DIG}^{(3)}$                                                                                                                      |                |                            | 8    | 10                | ρΓ   |

<sup>(1)</sup> The total current consumption when no output is active is calculated by  $I_{DD\_ANA}(off) + I_{DD\_DIG}$ .

Copyright © 2009–2012, Texas Instruments Incorporated

<sup>(2)</sup> For C<sub>L</sub> = 30 pF, the typical current for one output is 2.2 mA (see Figure 8).

(3) The I<sup>2</sup>C standard specifies a maximum C<sub>I</sub> of 10 pF.

over recommended operating free-air temperature range (unless otherwise noted)

|                          | PARAMETER                                                          | TEST CONDITIONS                                                                 |                                                | MIN                           | TYP  | MAX  | UNIT              |  |

|--------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------|-------------------------------|------|------|-------------------|--|

|                          | SINE-WAV                                                           | E PARAMETER (MCLK_IN                                                            | is sine-wave si                                | gnal, C <sub>L</sub> = 10 pF  | =)   |      |                   |  |

| f <sub>OUT</sub>         | Output frequency                                                   |                                                                                 |                                                |                               |      | 52   | MHz               |  |

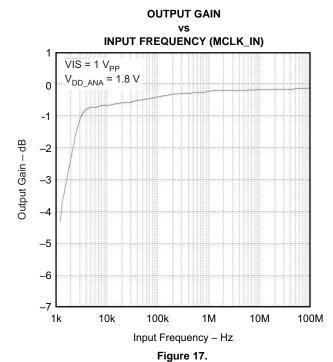

| V <sub>OS</sub>          | Output gain level (see Figure 17)                                  | MCLK_IN-to-CLKx; 10 kΩ, 10 pF; ac-coupled;                                      | 0.5 ≤ V <sub>IS</sub> ≤<br>1.2 V <sub>PP</sub> | -1                            | -0.3 | 0    | dB                |  |

|                          | Output voltage                                                     | f <sub>MCLK_IN</sub> > 1 MHz                                                    | $V_{IS} = 0.5 V_{PP}$                          | 445                           | 490  | 500  | $mV_{PP}$         |  |

|                          | Additive was litter(4)                                             | 10 Hz to 10 MHz; f <sub>OUT</sub> = 38                                          | B.4 MHz                                        |                               | 0.3  | 0.6  |                   |  |

| <sup>T</sup> jitadd(rms) | Additive rms jitter <sup>(4)</sup>                                 | 10 kHz to 10 MHz; f <sub>OUT</sub> = 3                                          | 88.4 MHz                                       |                               | 0.1  | 0.2  | ps <sub>RMS</sub> |  |

|                          |                                                                    | At offset = 1 kHz                                                               |                                                |                               | -142 | -135 |                   |  |

| pn <sub>add</sub>        | Additive phase noise at f <sub>OUT</sub> = 38.4 MHz <sup>(5)</sup> | At offset = 10 kHz                                                              |                                                |                               | -152 | -145 | dBc/Hz            |  |

|                          | 00.4 WHZ                                                           | At offset = 100 kHz                                                             |                                                |                               | -157 | -150 |                   |  |

| R <sub>IN</sub>          | Input resistance                                                   | At dc level                                                                     |                                                | 12                            | 15   |      | kΩ                |  |

| C <sub>IN</sub>          | Input capacitance                                                  | f <sub>MCLK_IN</sub> = 38.4 MHz                                                 |                                                | 5                             | 7    | pF   |                   |  |

|                          | ELECTR                                                             | ICAL CHARACTERISTIC of                                                          | of LDO (C <sub>OUT</sub> = 0                   | ).8 to 2.7 μF) <sup>(6)</sup> |      |      | ·                 |  |

| V <sub>BAT</sub>         | Input voltage range                                                |                                                                                 |                                                | 2.3                           |      | 5.5  | V                 |  |

| $V_{LDO}$                | LDO output voltage <sup>(7)</sup>                                  | $2.3 \text{ V} < \text{V}_{\text{BAT}} < 5.5 \text{ V}, \text{I}_{\text{LOAD}}$ | = 5 mA                                         | 1.72                          | 1.8  | 1.9  | V                 |  |

|                          | Maximum line regulation                                            | 2.3 V < V <sub>BAT</sub> ≤ 5.5 V, I <sub>LOAD</sub> = 5 mA                      |                                                |                               | 0.5% |      |                   |  |

| $\Delta V_{LDO}$         | Maximum load regulation                                            | $0 < I_{LOAD} < 5 \text{ mA}, V_{BAT} = 2$<br>$T_{J} = 25^{\circ}\text{C}$      | .3 V or 5.5 V;                                 |                               | 0.5% |      |                   |  |

| I <sub>LOAD</sub>        | Load current                                                       | $C_{OUT} = 0.8 \mu\text{F}$ to 2.7 $\mu\text{F}$                                |                                                | 0                             | 5    |      | mA                |  |

| I <sub>LCL</sub>         | LDO output current limit                                           | $V_{LDO} = 0.9 \times V_{LDO(TYP)}$                                             |                                                | 10                            |      | 60   | mA                |  |

| I <sub>LGND</sub>        | LDO ground pin current <sup>(8)</sup>                              | $V_{BAT} = 3.6 \text{ V}; 0 < I_{LOAD} < 5$                                     | mA                                             |                               | 50   | 150  | μA                |  |

| I <sub>LSHDN</sub>       | LDO shutdown current                                               | 2.3 V < V <sub>BAT</sub> < 5.5 V                                                |                                                |                               |      | 0.2  | μA                |  |

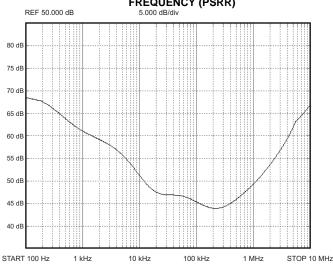

|                          |                                                                    |                                                                                 | 100 Hz                                         | 60                            | 68   |      |                   |  |

|                          |                                                                    | $V_{BAT} = 2.3 \text{ V (for min)}$                                             | 1 kHz                                          | 55                            | 62   |      |                   |  |

| DCDD                     | Power-supply rejection ratio                                       | $V_{BAT} = 2.5 \text{ V (for typ)}$                                             | 10 kHz                                         | 45                            | 52   |      |                   |  |

| PSRR                     | (ripple rejection) (see Figure 20)                                 | $V_{LDO} = 1.8 \text{ V}$<br>$I_{LOAD} = 5 \text{ mA}$                          | 100 kHz                                        | 33                            | 40   |      | dB                |  |

|                          |                                                                    | $V_{ripple} = 0.1 \text{ Vpp}$                                                  | 1 MHz                                          | 37                            | 46   |      |                   |  |

|                          |                                                                    |                                                                                 | 10 MHz                                         | 60                            | 67   |      |                   |  |

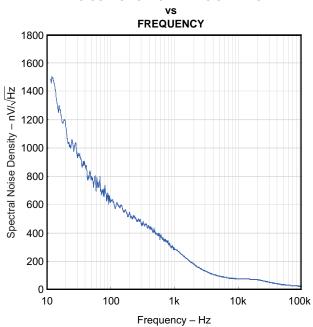

| V <sub>N</sub>           | Output noise voltage (see Figure 21)                               | BW = 10 Hz to 100 kHz; $V_L$<br>$I_{LOAD}$ = 5 mA                               | <sub>DO</sub> = 1.8 V;                         |                               |      | 30   | μV <sub>RMS</sub> |  |

(4) Additive rms jitter is the integrated rms jitter that the device adds to the signal chain. It is calculated by t<sub>j</sub>itadd(rms) = √(t<sub>j</sub>itout(rms)<sup>2</sup> - t<sub>j</sub>itin(rms)<sup>2</sup>). Specified with the supply ripple noise of 30 μV(rms) from 10 Hz to 100 kHz.

(5) Additive phase noise is the amount of phase noise that the device adds to the signal chain. It is calculated by L<sub>add</sub> (dB) = 10 log (10<sup>0.1 Lout</sup> - 10<sup>0.1 Lin</sup>).

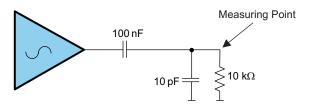

(6) Minimum C<sub>OUT</sub> should be 100 nF to allow for stable LDO operation.

(8) LDO ground pin current does not change over V<sub>BAT</sub>.

LDO output voltage includes maximum line and load regulation.

### TIMING REQUIREMENTS

over operating free-air temperature range (unless otherwise noted)  $V_{LDO} = 1.8 \text{ V}$ ;  $C_{L} = 10 \text{ pF}$ ;  $R_{L} = 10 \text{ k}\Omega$

| PARAMETER                       |                                                                                    | TEST CONDITIONS                                                                                                                                                                                                                  | MIN TYP | 1) MAX | UNIT |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|------|--|--|--|

| TIMING PARAMETER                |                                                                                    |                                                                                                                                                                                                                                  |         |        |      |  |  |  |

| t <sub>PD</sub>                 | Propagation delay time                                                             | MCLK_IN-to-CLKx; f <sub>MCLK_IN</sub> = 38.4 MHz                                                                                                                                                                                 |         | 3      | ns   |  |  |  |

| t <sub>LH</sub>                 | Propagation delay time, low-to-high                                                | REQx-to-MCLK_REQ (wired-OR, $C_L$ = 15 pF, $R_L$ = 10 k $\Omega$ );                                                                                                                                                              |         | 15     | ns   |  |  |  |

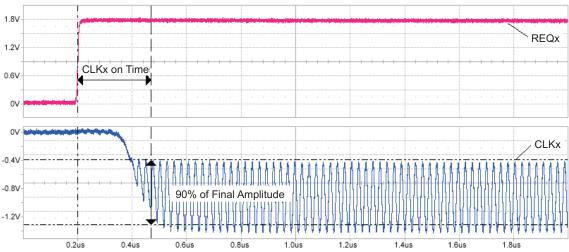

|                                 | CLKx on-time – REQ-to-CLKx                                                         | f <sub>MCLK IN</sub> = 38.4 MHz; V <sub>VDD ANA</sub> is on;                                                                                                                                                                     | 0       | .3 0.4 | μs   |  |  |  |

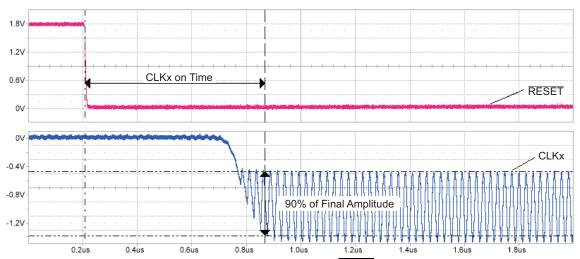

|                                 | CLKx on-time – RESET-to-CLKx <sup>(3)</sup>                                        | $V_{IS} = 1 \text{ V}$ ; $V_{OS} = -1 \text{ dB}$ (see Figure 5 and                                                                                                                                                              | 0       | .6 0.8 | μs   |  |  |  |

| t <sub>CLK</sub> <sup>(2)</sup> | CLKx off-time – REQ-to-CLKx                                                        | Figure 6)                                                                                                                                                                                                                        |         | 25     | ns   |  |  |  |

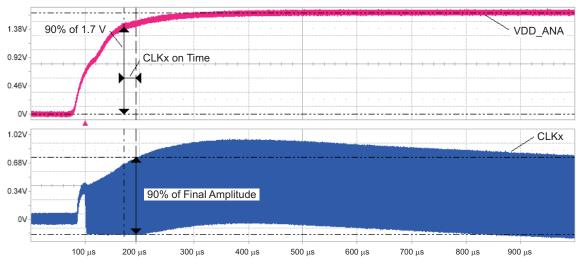

| -OLK                            | CLKx on-time – V <sub>DD_ANA</sub> to-CLKx V <sub>OS</sub> =                       | $\begin{split} f_{MCLK\_IN} &= 38.4 \text{ MHz} \; ; \; V_{IS} = 1 \; V; \\ V_{OS} &= -1 \; dB; \; \text{measurement starts when} \\ V_{DD\_ANA} \; \text{is } 90\% \; \text{of } 1.7 \; V \; \text{(see Figure 7)} \end{split}$ | 2       | 20 50  | μs   |  |  |  |

| t <sub>SP</sub>                 | Pulse duration of spikes that must be suppressed by the input filter for RESET (3) |                                                                                                                                                                                                                                  |         | 100    | ns   |  |  |  |

| t <sub>sk(o)</sub>              | Output skew <sup>(4)</sup>                                                         | f <sub>MCLK_IN</sub> = 38.4 MHz; CLK1-to-CLK4                                                                                                                                                                                    | 2       | 25 50  | ps   |  |  |  |

| t <sub>LDO</sub>                | LDO on-time <sup>(5)</sup> – REQ-to-LDO; – RESET-to-LDO                            | $V_{LDO} = 1.7 \text{ V}, I_{LDO} = 5 \text{ mA}, \\ 2.3 \text{ V} < V_{BAT} < 5.5 \text{ V}; C_{OUT} = 2.7 \mu\text{F}$                                                                                                         | 10      | 00 300 | μs   |  |  |  |

- All typical values are at nominal  $V_{DD\_ANA}$  and  $V_{DD\_DIG}$ . CLK on-time is measured with valid input signal ( $\overline{V}_{IS}=1$  Vpp). In case a TXCO is used, the LDO and TCXO are already on. Pulses above 500 ns are interpreted as a valid reset signal. Total time from RESET-to-CLKx is the sum of tsp + tclk\_/RESET.

- Output skew is calculated as the greater of the difference between the fastest and the slowest tpl.H or the difference between the fastest and the slowest  $t_{\text{PHL}}$ . LDO off-time depends on the discharge time of the R-C components (seeFigure 4).

|                        | PARAMETER                                                                                                                      | MIN              | MAX | UNIT |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------|--|--|--|

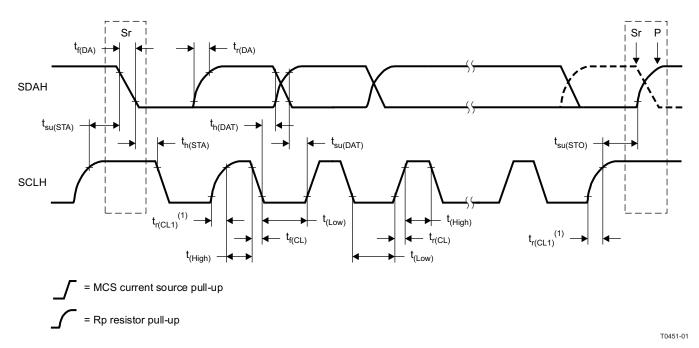

| 5                      | SDAH/SCLH TIMING REQUIREMENTS, Hs-Mode (C <sub>BUS</sub> = 100 pF for each I <sup>2</sup> C line; see Figure 24 and Figure 25) |                  |     |      |  |  |  |

| f <sub>SCLH</sub>      | SCLH clock frequency                                                                                                           | 0                | 3.4 | MHz  |  |  |  |

| t <sub>su(START)</sub> | START setup time (SCLH high before SDAH low)                                                                                   | 160              |     | ns   |  |  |  |

| t <sub>h(START)</sub>  | START hold time (SCLH low after SDAH low)                                                                                      | 160              |     | ns   |  |  |  |

| t <sub>LOW</sub>       | Low period of the SCLH clock                                                                                                   | 160              |     | ns   |  |  |  |

| t <sub>HIGH</sub>      | High period of the SCLH clock                                                                                                  | 60               |     | ns   |  |  |  |

| t <sub>h(SDAH)</sub>   | SDAH hold time (SDAH valid after SCLH low)                                                                                     | 0 <sup>(1)</sup> | 70  | ns   |  |  |  |

| t <sub>su(SDAH)</sub>  | SDAH setup time                                                                                                                | 10               |     | ns   |  |  |  |

|                        | SCLH rise time                                                                                                                 | 10               | 40  | ns   |  |  |  |

| t <sub>r</sub>         | SDAH rise time                                                                                                                 | 10               | 80  |      |  |  |  |

|                        | SCLH fall time                                                                                                                 | 10               | 40  | ns   |  |  |  |

| t <sub>f</sub>         | SDAH fall time                                                                                                                 | 10               | 80  |      |  |  |  |

| t <sub>su(STOP)</sub>  | STOP setup time                                                                                                                | 160              |     | ns   |  |  |  |

| t <sub>SP</sub>        | Pulse duration of spikes that must be suppressed by the input filter for SDAH and SCLH                                         | 0                | 10  | ns   |  |  |  |

(1) A device must internally provide a data hold time to bridge the undefined period between V<sub>IH</sub> and V<sub>IL</sub> of the falling edge of the SCLH signal. An input circuit with a threshold as low as possible for the falling edge of the SCLH signal minimizes this hold time.

Product Folder Links: CDC3S04

## PARAMETER MEASUREMENT INFORMATION

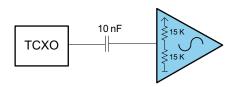

Figure 1. Input Circuit

Figure 3. Wired OR

Figure 2. Output Circuit

i.e. time constant(RxC) is 440  $\mu s$  for 63% discharge.

Figure 4. LDO Output Circuit

### **TYPICAL CHARACTERISTICS**

Figure 5. CLKx On-Time From RESET Off-to-On

Figure 6. CLKx On-Time From REQ Off-to-On

Figure 7. CLKx On-Time From  $V_{DD\_ANA}$  Off-to-On

Copyright © 2009–2012, Texas Instruments Incorporated

## SUPPLY CURRENT (IDD\_ANA, IDD\_DIG)

### vs OUTPUT LOAD (CL) AT 38.4 MHz INPUT CLOCK

#### Figure 8.

## SUPPLY CURRENT (IDD\_ANA, IDD\_DIG)

### **OUTPUT LOAD (CL) AT 26 MHz INPUT CLOCK**

Figure 9.

# SUPPLY CURRENT (IDD\_ANA, IDD\_DIG) vs

### INPUT FREQUENCY (MCLK\_IN)

Figure 10.

SUPPLY CURRENT (IDD\_ANA, IDD\_DIG)

#### vs

Figure 11.

## ${\bf SUPPLY\ CURRENT\ (IDD\_ANA,\ IDD\_DIG)}$

## INPUT VOLTAGE LEVEL AT 26 MHz INPUT CLOCK

Figure 12.

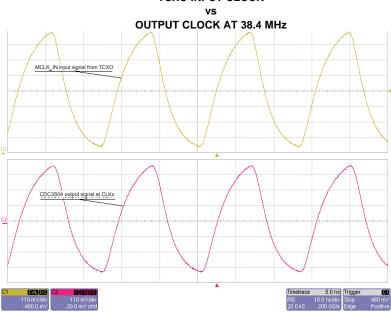

## TCXO INPUT CLOCK

Figure 13.

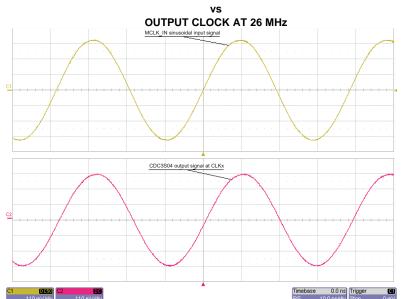

## TCXO INPUT CLOCK

### vs OUTPUT CLOCK AT 26 MHz

Figure 14.

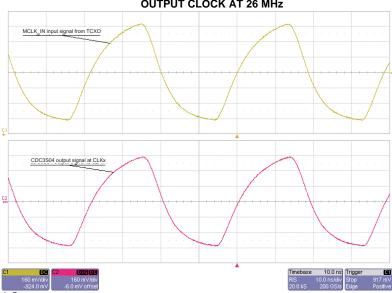

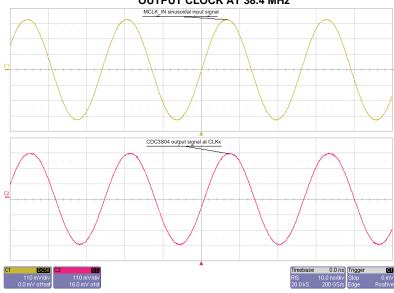

### SINE WAVE INPUT CLOCK

#### vs OUTPUT CLOCK AT 38.4 MHz

Figure 15.

SINE WAVE INPUT CLOCK

Figure 16.

**INPUT**

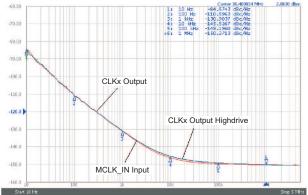

### **OUTPUT PHASE-NOISE PERFORMANCE WITH 38.4-MHz TCXO**

Figure 18.

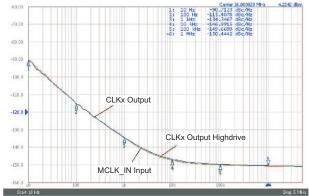

### INPUT vs

### **OUTPUT PHASE-NOISE PERFORMANCE WITH 26-MHz TCXO**

Figure 19.

### LDO POWER SUPPLY REJECTION

FREQUENCY (PSRR)

Figure 20.

## LDO OUTPUT SPECTRAL NOISE DENSITY

Figure 21.

#### DETAILED DESCRIPTION

## SDAH/SCLH SERIAL INTERFACE (Hs-Mode)

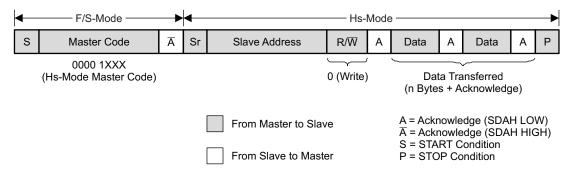

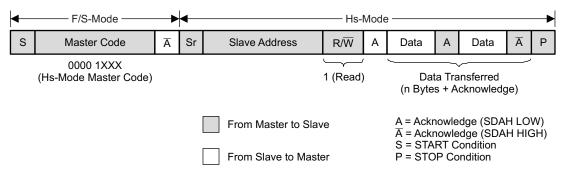

This section describes the SDAH/SCLH interface of the CDC3S04 device. The CDC3S04 operates as a slave device of the two-wire serial SDAH/SCLH bus, compatible with the popular I<sup>2</sup>C specification (UM10204-I<sup>2</sup>C-bus specification and user manual Rev. 03-19 June 2007). It operates in the high-speed mode (up to 3.4 Mbit/s) and supports 7-bit addressing. The CDC3S04 is fully downward compatible with fast- and standard-mode (F/S) devices for bidirectional communication in a mixed-speed bus system.

#### Data Protocol

The device supports byte-write and byte-read operations only. There is no block-write or block-read operation supported; therefore, no command code byte is needed.

When a byte has been sent, it is written into the internal register and is immediately effective.

## Slave Receiver Address (7 bits)

| Device  | A6 | A5 | A4 | A3 | A2 | A1 | A0 <sup>(1)</sup> | R/W |

|---------|----|----|----|----|----|----|-------------------|-----|

| CDC3S04 | 1  | 1  | 0  | 1  | 1  | 0  | 0                 | 1/0 |

<sup>(1)</sup> Address bit A0 is selectable by the ADR\_A0 input (pin D1). This allows addressing of two devices connected to the same I<sup>2</sup>C bus. The default value is 0, set by an internal pulldown resistor.

## **Byte-Write Programming Sequence**

Figure 22. Byte-Write Protocol

## **Byte-Read Programming Sequence**

Figure 23. Byte-Read Protocol

Product Folder Links: CDC3S04

(1) First rising edge of the SCLH signal after Sr and after each acknowledge bit.

Figure 24. Definition of Timing for a Complete Hs-Mode Transfer

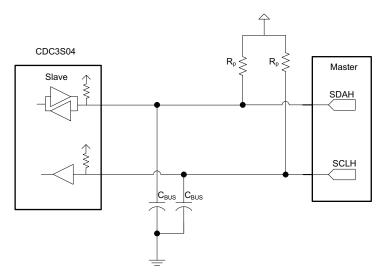

The following diagram shows how the CDC3S04 clock buffer is connected to the SDAH/SCLH serial interface bus. Multiple devices can be connected to the bus, but the speed may need to be reduced (3.4 MHz is the maximum) if many devices are connected.

Note that the pullup resistors ( $R_P$ ) depend on the supply voltage, bus capacitance, and number of connected devices. For more details, see the  $I^2C$  bus specification.

Figure 25. SDAH/SCLH Hardware Interface

## **SDAH/SCLH Configuration Registers**

The output stages are user configurable. Table 3 explains the programmable functions of the CDC3S04.

## Table 3. Configuration Register (Shaded Cells Marks Power-Up/Default Setting)

| Offset                | BIT <sup>(1)</sup> | Acronym    | Default (2) | RESET (3)                                                                                      | Description                                                         | 0            | 1                 | Туре |  |  |

|-----------------------|--------------------|------------|-------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------|-------------------|------|--|--|

|                       | 7                  | REQ4INT    | 1b          | 1b                                                                                             | CLK4 off/on <sup>(4)</sup>                                          | Off          | On                |      |  |  |

|                       | 6                  | REQ3INT    | 0b          | _                                                                                              | CLK3 off/on <sup>(4)</sup>                                          | Off          | On                | 1    |  |  |

| 00h                   | 5                  | REQ2INT    | 0b          | _                                                                                              | CLK2 off/on <sup>(4)</sup>                                          | Off          | On                | Ī    |  |  |

|                       | 4                  | REQ1INT    | 1b          | 1b                                                                                             | CLK1 off/on <sup>(4)</sup>                                          | Off          | On                | R/W  |  |  |

|                       | 3                  | REQ4POL    | 1b          | -                                                                                              | Selects polarity of REQ4                                            | Active-low   | Active-high       | R/VV |  |  |

|                       | 2                  | REQ3POL    | 1b          | _                                                                                              | Selects polarity of REQ3                                            | Active-low   | Active-high       |      |  |  |

|                       | 1                  | REQ2POL    | 1b          | _                                                                                              | Selects polarity of REQ2                                            | Active-low   | Active-high       |      |  |  |

|                       | 0                  | REQ1POL    | 1b          | _                                                                                              | Selects polarity of REQ1                                            | Active-low   | Active-high       |      |  |  |

|                       | 7                  | MREQ4      | 1b          | -                                                                                              | Defines if REQ4 is used to decode MCLK_REQ                          |              | Used for decoding |      |  |  |

|                       | 6                  | MREQ3      | 1b          | -                                                                                              | Defines if REQ3 is used to decode MCLK_REQ                          | Not used for |                   |      |  |  |

|                       | 5                  | MREQ2      | 1b          | -                                                                                              | Defines if REQ2 is used to decode MCLK_REQ                          | decoding     |                   |      |  |  |

| 01h                   | 4                  | MREQ1      | 1b          | -                                                                                              | Defines if REQ1 is used to decode MCLK_REQ                          |              | R/W               |      |  |  |

|                       | 3                  | MCLKOUT1   |             |                                                                                                | Selects MCLK_REQ output type                                        |              |                   | 1    |  |  |

|                       | 2                  | MCLKOUT0   | 00b         | _                                                                                              | 00 = wired-OR (default setting)<br>01 = wired-AND<br>1x = push-pull |              |                   |      |  |  |

|                       | 0–1                | _          | 00b         | _                                                                                              | Reserved                                                            |              |                   |      |  |  |

|                       | 7                  | MREQCTRL1  |             |                                                                                                | MCLK_REQ generation (see Figure 27)                                 |              |                   |      |  |  |

|                       | 6                  | MREQCTRL0  | 00b         | _                                                                                              | 0x = decoder controlled (default setting)<br>10 = low<br>11 = high  |              |                   |      |  |  |

|                       | 5                  | LDOEN1     |             |                                                                                                | Switches LDO on or off:                                             |              |                   |      |  |  |

| 02h                   | 4 LDOEN0 00b       |            | -           | 00 = LDO is on (default setting)<br>01 = LDO is off<br>1x = decoder controlled (see Figure 27) |                                                                     |              | R/W               |      |  |  |

|                       | 3                  | REQ4PRIO   | 1b          | 1b                                                                                             | Defines external vs internal REQ4 priority                          | REQ4         | REQ4INT           |      |  |  |

|                       | 2                  | REQ3PRIO   | 0b          | _                                                                                              | Defines external vs internal REQ3 priority                          | REQ3         | REQ3INT           |      |  |  |

|                       | 1                  | REQ2PRIO   | 0b          | _                                                                                              | Defines external vs internal REQ2 priority                          | REQ2         | REQ2INT           |      |  |  |

|                       | 0                  | REQ1PRIO   | 1b          | 1b                                                                                             | Defines external vs internal REQ1 priority                          | REQ1INT      |                   |      |  |  |

|                       | 7                  | HIGHDRIVE4 | 0b          | -                                                                                              | Enables high-drive capability CLK4                                  | Typical      | High              |      |  |  |

|                       | 6                  | HIGHDRIVE3 | 0b          | -                                                                                              | Enables high-drive capability CLK3                                  | High         | R/W               |      |  |  |

| 03h                   | 5                  | HIGHDRIVE2 | 0b          | -                                                                                              | Enables high-drive capability CLK2                                  | High         |                   |      |  |  |

|                       | 4                  | HIGHDRIVE1 | 0b          | -                                                                                              | Enables high-drive capability CLK1                                  | Typical      | High              |      |  |  |

|                       | 0–3                | _          | 0b          | -                                                                                              | Reserved                                                            |              |                   |      |  |  |

| 04h-Bh <sup>(5)</sup> |                    | _          |             | _                                                                                              | Reserved                                                            |              |                   | R/W  |  |  |

|                       |                    |            |             |                                                                                                |                                                                     |              |                   |      |  |  |

All data is transferred with the MSB first.

<sup>(2)</sup> A device reset to default condition is initiated by a V<sub>DD DIG</sub> power-up sequence.

(3) "-" means that dedicated bits do not change at RESET.

(4) Inactive as long as the REQxPRIO bit is low, external REQx pins are valid (see Figure 26)

(5) Writing data beyond 03h may affect device function.

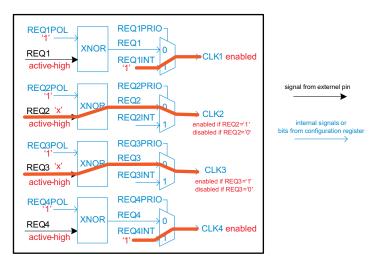

Figure 26. Clock Output Enable Signal (Shaded Line Marks Power-Up/Default Setting)

Figure 27. Decoding Scheme for MCLK\_REQ and LDOEN (Shaded Line Marks Power-Up/Default Setting)

## **APPLICATION INFORMATION**

Figure 28. Clock Distribution Scheme

## **REVISION HISTORY**

| Changes from Original (October 2009) to Revision A                                  | Page   |

|-------------------------------------------------------------------------------------|--------|

| Changed the format on page 1 (moved 2 paragraphs from page 2 to page 1)             | 1      |

| Changed the X axis from 0.1us to 100us900us                                         |        |

| Changed Offset 00h Bit 4 Default value from 0h to 1b                                |        |

| Changes from Revision A (July 2010) to Revision B                                   | Page   |

| Changed Table 3 "Offset" values listed in "Default" and "RESET" columns from "h" to | "b" 18 |

| Changes from Revision B (May 2011) to Revision C                                    | Page   |

| Changed from Rev B, 2011 to Rev C, 2012                                             |        |

| Changed the 8th Feature item from -30°C to -40°C                                    | 1      |

| • Changed in the last paragraph of description from -30°C to -40°C                  | 2      |

| <ul> <li>Changed in the ROC table last row, from –30°C to –40°C</li> </ul>          | 4      |

## PACKAGE OPTION ADDENDUM

25-Jul-2012

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| CDC3S04YFFR      | ACTIVE                | DSBGA        | YFF                | 20   | 3000        | Green (RoHS<br>& no Sb/Br) | SNAGCU               | Level-1-260C-UNLIM           |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com 25-Jul-2012

## TAPE AND REEL INFORMATION

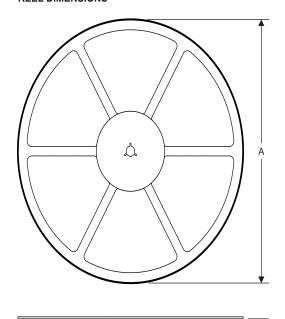

### **REEL DIMENSIONS**

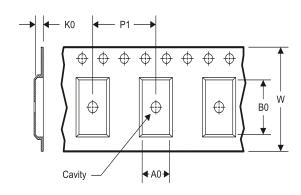

### **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### TAPE AND REEL INFORMATION

## \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CDC3S04YFFR | DSBGA           | YFF                | 20 | 3000 | 180.0                    | 8.4                      | 1.63       | 2.08       | 0.69       | 4.0        | 8.0       | Q1               |

www.ti.com 25-Jul-2012

### \*All dimensions are nominal

| Device      | F | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-------------|---|--------------|-----------------|------|------|-------------|------------|-------------|--|

| CDC3S04YFFR |   | DSBGA        | YFF             | 20   | 3000 | 210.0       | 185.0      | 35.0        |  |

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

- The package size (Dimension D and E) of a particular device is specified in the device Product Data Sheet version of this drawing, in case it cannot be found in the product data sheet please contact a local TI representative.

- E. Reference Product Data Sheet for array population. 5 x 4 matrix pattern is shown for illustration only.

- F. This package contains Pb-free balls.

NanoFree is a trademark of Texas Instruments

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

#### Products Applications

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers DI P® Products Consumer Electronics www.dlp.com www.ti.com/consumer-apps

DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface Medical www.ti.com/medical interface.ti.com Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors <u>www.ti.com/omap</u> TI E2E Community <u>e2e.ti.com</u>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>