# National Semiconductor

# 93L00 **4-Bit Universal Shift Register**

# **General Description**

The 93L00 is a 4-bit universal shift register. As a high speed multifunctional sequential logic block, it is useful in a wide variety of register and counter applications. It may be used in serial-serial, shift left, shift right, serial-parallel, parallelserial, and parallel-parallel data register transfers.

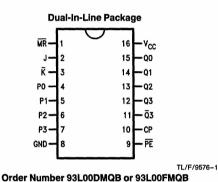

# **Connection Diagram**

See NS Package Number J16A or W16A

#### **Features**

- Asynchronous master reset

- J. K inputs to first stage

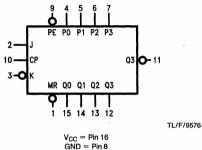

# **Logic Symbol**

TL/F/9576-2

| Pin Names | Description                            |  |  |  |  |  |  |

|-----------|----------------------------------------|--|--|--|--|--|--|

| PE        | Parallel Enable Input (Active LOW)     |  |  |  |  |  |  |

| P0-P3     | Parallel Inputs                        |  |  |  |  |  |  |

| J         | First Stage J Input (Active HIGH)      |  |  |  |  |  |  |

| ĸ         | First Stage K Input (Active LOW)       |  |  |  |  |  |  |

| CP        | Clock Pulse Input (Active Rising Edge) |  |  |  |  |  |  |

| MR        | Master Reset Input                     |  |  |  |  |  |  |

| Q0-Q3     | Parallel Outputs                       |  |  |  |  |  |  |

| Q3        | Complementary Last Stage Output        |  |  |  |  |  |  |

#### Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                       | 7V              |

|--------------------------------------|-----------------|

| Input Voltage                        | 5.5V            |

| Operating Free Air Temperature Range |                 |

| MIL                                  | -65°C to +125°C |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

| Symbol                                   | Parameter                                                 |          | Units |      |    |  |

|------------------------------------------|-----------------------------------------------------------|----------|-------|------|----|--|

| Symbol                                   | Farameter                                                 | Min      | Nom   | Max  | V  |  |

| V <sub>CC</sub>                          | Supply Voltage                                            | 4.5      | 5     | 5.5  |    |  |

| V <sub>IH</sub>                          | High Level Input Voltage                                  | 2        |       |      | v  |  |

| VIL                                      | Low Level Input Voltage                                   |          |       | 0.7  | v  |  |

| ЮН                                       | High Level Output Voltage                                 |          |       | -0.4 | mA |  |

| IOL                                      | Low Level Output Current                                  |          |       | 4.8  | mA |  |

| T <sub>A</sub>                           | Free Air Operating Temperature                            | -55      |       | 125  | °C |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW, J, $\overline{K}$ and P0–P3 to CP | 60<br>60 |       |      | ns |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW, J, $\overline{K}$ and P0–P3 to CP  | 0<br>0   |       |      | ns |  |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW,<br>PE to CP                       | 68<br>68 |       |      | ns |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW,<br>PE to CP                        | 0        |       |      | ns |  |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse Width<br>HIGH or LOW                             | 38<br>38 |       |      | ns |  |

| t <sub>w</sub> (L)                       | MR Pulse Width LOW                                        | 53       |       |      | ns |  |

| trec                                     | Recovery Time, MR to CP                                   | 70       |       |      | ns |  |

# **Recommended Operating Conditions**

#### **Electrical Characteristics**

Over recommended operating free air temperature range (unless otherwise noted)

| Symbol             | Parameter                            | Conditions                                                                                                                                       | Min    | Typ<br>(Note 1) | Max  | Units |    |

|--------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|------|-------|----|

| VI                 | Input Clamp Voltage                  | $V_{CC} = Min$ , $I_I = -10 mA$                                                                                                                  |        |                 | -1.5 | v     |    |

| V <sub>OH</sub>    | High Level Output Voltage            | $\label{eq:VCC} \begin{split} V_{CC} &= \text{Min}, \text{I}_{OH} = \text{Max}, \\ V_{IL} &= \text{Max}, \text{V}_{IH} = \text{Min} \end{split}$ | 2.4    | 3.4             |      | v     |    |

| V <sub>OL</sub>    | Low Level Output Voltage             | $V_{CC} = Min, I_{OL} = Max,$<br>$V_{IH} = Min, V_{IL} = Max$                                                                                    |        |                 |      | 0.3   | v  |

| l;                 | Input Current @ Max<br>Input Voltage | $V_{CC} = Max, V_I = 5.5V$                                                                                                                       |        |                 |      | 1     | mA |

| Чн                 | High Level Input Current             | $V_{CC} = Max, V_1 = 2.4V$                                                                                                                       | Inputs |                 |      | 20    |    |

|                    |                                      |                                                                                                                                                  | СР     |                 |      | 40    | μA |

|                    |                                      |                                                                                                                                                  | PE     |                 |      | 46    |    |

| l <sub>IL</sub> Lo | Low Level Input Current              | $V_{CC} = Max, V_I = 0.3V$                                                                                                                       | Inputs |                 |      | -400  |    |

|                    |                                      |                                                                                                                                                  | CP     |                 |      | -800  | μΑ |

|                    |                                      |                                                                                                                                                  | PE     |                 |      | -920  |    |

| los                | Short Circuit<br>Output Current      | V <sub>CC</sub> = Max<br>(Note 2)                                                                                                                |        | -2.5            |      | -25   | mA |

| Icc                | Supply Current                       | V <sub>CC</sub> = Max                                                                                                                            |        |                 |      | 23    | mA |

Note 1: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 2: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Switching Characteristics  $V_{CC}$  = +5.0V,  $T_A$  = +25°C (See Section 1 for waveforms and load configurations)

| Symbol           |                                             | 9                | Units    |     |

|------------------|---------------------------------------------|------------------|----------|-----|

|                  | Parameter                                   | C <sub>L</sub> = |          |     |

|                  |                                             | Min              | Max      |     |

| f <sub>max</sub> | Maximum Shift Frequency                     | 10               |          | MHz |

| tpLH<br>tpHL     | Propagation Delay<br>CP to Q <sub>n</sub>   |                  | 35<br>51 | ns  |

| t <sub>PHL</sub> | Propagation Delay, $\overline{MR}$ to $Q_n$ |                  | 60       | ns  |

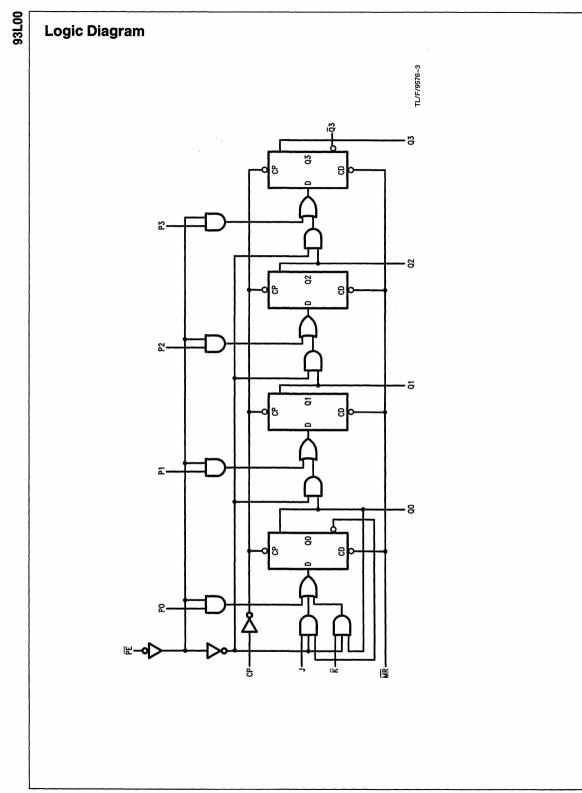

### **Functional Description**

The Logic Diagrams and Truth Table indicate the functional characteristics of the 93L00 4-bit shift register. The device is useful in a wide variety of shifting, counting and storage applications. It performs serial, parallel, serial-to-parallel, or parallel-to-serial data transfers.

The 93L00 has two primary modes of operation, shift right (Q0  $\rightarrow$  Q1) and parallel load, which are controlled by the state of the Parallel Enable (PE) input. When the PE input is HIGH, serial data enters the first flip-flop Q0 via the J and K inputs and is shifted one bit in the direction Q0  $\rightarrow$  Q1  $\rightarrow$  Q2  $\rightarrow$  Q3 following each LOW-to-HIGH clock transition. The JK inputs provide the flexibility of the JK type input for special applications, and the simple D-type input for general applications by tying the two pins together.

When the  $\overline{\text{PE}}$  input is LOW, the 93L00 appears as four common clocked D flip-flops. The data on the parallel inputs P0–P3 is transferred to the respective Q0–Q3 outputs following the LOW-to-HIGH clock transition. Shift left operation (Q3  $\rightarrow$  Q2) can be achieved by tying the Qn outputs to the Pn–1 inputs and holding the  $\overline{\text{PE}}$  input LOW.

All serial and parallel data transfers are synchronous, occuring after each LOW-to-HIGH clock transition. Since the 93L00 utilizes edge triggering, there is no restriction on the activity of the J,  $\vec{K}$ , Pn and  $\vec{PE}$  inputs for logic operation—except for the setup and release time requirements. A LOW on the asynchronous Master Reset (MR) input sets all Q outputs LOW, independent of any other input condition.

# Truth Table

| Operating<br>Mode | Inputs ( $\overline{MR} = H$ ) |   |   |    |    |    |    | Outputs @ t <sub>n + 1</sub> |    |    |    |    |

|-------------------|--------------------------------|---|---|----|----|----|----|------------------------------|----|----|----|----|

|                   | PE                             | j | ĸ | P0 | P1 | P2 | P3 | QO                           | Q1 | Q2 | Q3 | Q3 |

| Shift Mode        | н                              | L | L | х  | х  | х  | х  | L                            | Q0 | Q1 | Q2 | Q2 |

|                   | н                              | L | н | х  | х  | х  | х  | QO                           | Q0 | Q1 | Q2 | Q2 |

|                   | н                              | н | L | х  | х  | х  | х  | QO                           | Q0 | Q1 | Q2 | Q2 |

|                   | н                              | н | н | х  | х  | х  | х  | н                            | Q0 | Q1 | Q2 | Q2 |

| Parallel          | L                              | x | х | L  | L  | L  | L  | L                            | L  | L  | L  | н  |

| Entry Mode        | L                              | x | x | н  | н  | н  | н  | н                            | н  | н  | н  | L  |

$t_{n+1} =$  Indicates state after next LOW-to-HIGH clock transition.

H = HIGH Voltage Level L = LOW Voltage Level

X = Immaterial