### REFER TO PAGE 18 FOR A, F AND Q PACKAGE PIN CONFIGURATIONS.

# DIGITAL 8000 SERIES TTL/MSI

#### DESCRIPTION

The 8T09 is a high speed quad bus driver device for applications requiring up to 25 loads interconnected on a single bus.

The outputs present a high impedance to the bus when disabled, (control input "1") and active drive when enabled

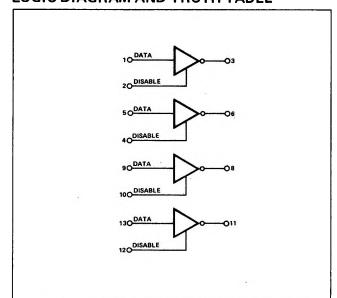

### LOGIC DIAGRAM AND TRUTH TABLE

| Data | Disable | Output         |  |  |

|------|---------|----------------|--|--|

| 0    | o       | 1              |  |  |

| 1    | 0       | 0              |  |  |

| 0    | 1       | Hi- Z          |  |  |

| 1    | 1       | Hi- Z<br>Hi- Z |  |  |

(control input "0"). This eliminates the resistor pull-up requirement while providing performance superior to open collector schemes. Each output can sink 40mA and drive 300pF loading with guaranteed propagation delay less than 22 nanoseconds.

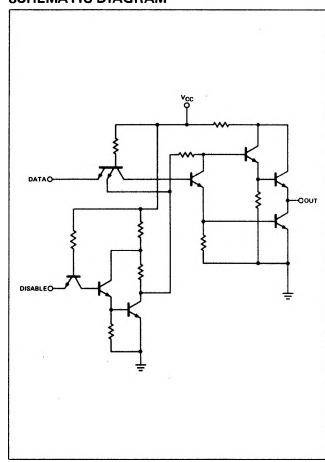

#### SCHEMATIC DIAGRAM

## **ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS              |      | LIMITS |        |       | TEST CONDITIONS |         |              | 410770 |

|------------------------------|------|--------|--------|-------|-----------------|---------|--------------|--------|

|                              | MIN. | TYP.   | MAX.   | UNITS | DATA            | DISABLE | OUTPUTS      | NOTES  |

| "1" Output Voltage           | 2.4  | 3.0    |        | V     | 0.8V            | 0.8∨    | -5.2mA       | 7      |

| "0" Output Voltage           |      | 0.2    | 0.4    | - v   | 2.0V            | 0.8∨    | 40mA         | 8      |

| Output Leakage Current       | -40  |        | +40    | μΑ    |                 | 2.0V    | 0.4V or 2.4V | 3      |

| "1" Input Current            |      | ļ      | 40     | μΑ    |                 | 4.5V    |              |        |

| "0" Input Current            | 100  |        | -2.0   | mA    | 0.4V            | 0.4V    |              |        |

| Input Latch Voltage          | 5.5  |        |        | V     | 10mA            | 10mA    |              |        |

| Power/Current Consumption    |      | 236/45 | 340/65 | mW/mA |                 |         |              | 11     |

| Output Short Circuit Current | -40  |        | -120   | mA    | 0V -            | 0∨      | 0V           |        |

$T_A = 25^{\circ} C$  and  $V_{CC} = 5.0 V$

| CHARACTERISTICS                     |      | LIMITS |      |       | TEST CONDITIONS |            |            |       |

|-------------------------------------|------|--------|------|-------|-----------------|------------|------------|-------|

|                                     | MIN. | TYP.   | MAX. | UNITS | DATA            | DISABLE    | OUTPUTS    | NOTES |

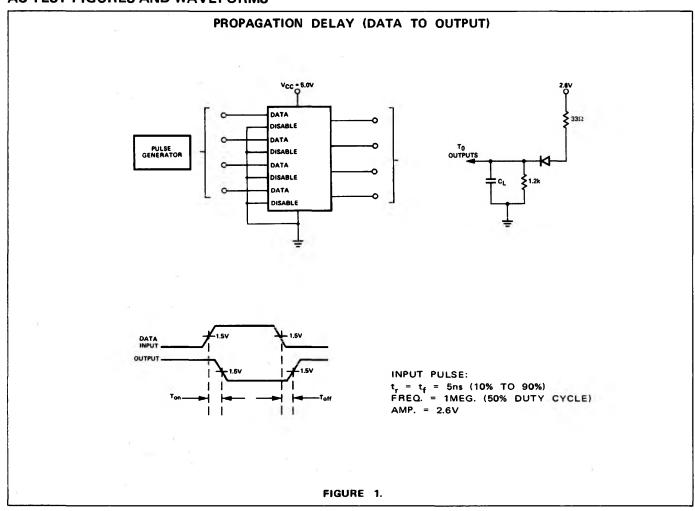

| Propagation Delay                   |      |        |      |       |                 |            |            |       |

| Data to Output                      |      |        |      |       |                 |            |            |       |

| t <sub>pd+</sub> , t <sub>pd-</sub> |      | l      | 10   | ns    |                 |            | 30pF load  | 9     |

| po pu                               |      | •      | 20   | ns    |                 |            | 300pF load | 9     |

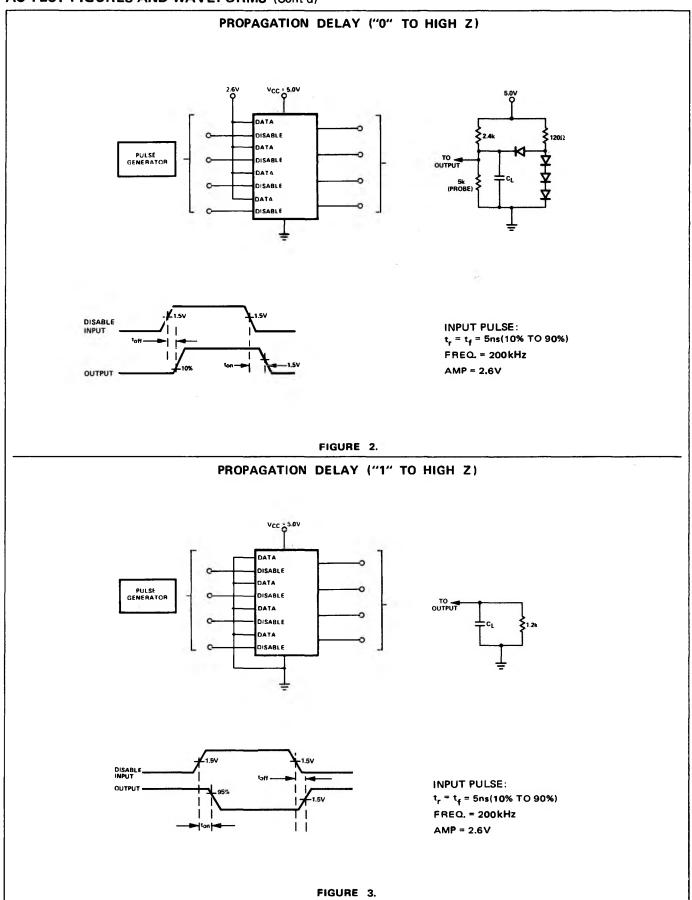

| Disable to Output                   |      | Į.     |      |       |                 | )          | ļ          | l     |

| High Z to 0, 0 to High Z            |      |        | 14   | ns    |                 |            | 30pF load  | 9     |

|                                     | -    | 22     | ns   |       |                 | 300pF load | 9          |       |

| High Z to 1, 1 to High Z            |      |        | 14   | ns    |                 |            | 30pF load  | 9     |

|                                     |      | 22     | ns   |       |                 | 300pF load | 9          |       |

#### NOTES:

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- All measurements are taken with ground pin tied to zero volts.

- 3. Positive current flow is defined as into the terminal referenced.

- 4. Positive NAND Logic definition:

- "UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings

- should the isolation diodes become forward biased.

- Measurements apply to each output and the associated data input independently.

- Output source current is supplied through a resistor to ground.

- 8. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 9. Refer to AC Test Figures.

- Manufacturer reserves the right to make design and process changes and improvements.

- 11.  $V_{CC} = 5.25 \text{ volts.}$

### **AC TEST FIGURES AND WAVEFORMS**

### AC TEST FIGURES AND WAVEFORMS (Cont'd)

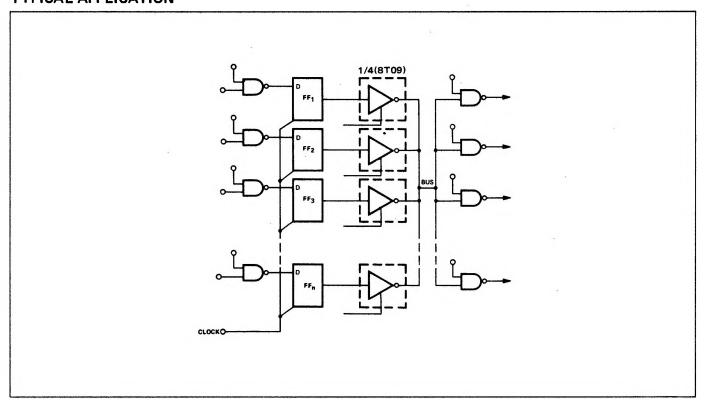

### TYPICAL APPLICATION

The above figure illustrates usage of the 8T09 in data processing logic. For example,  $FF_1$  thru  $FF_n$  may represent bit X in each of several functions in a minicomputer (accumulators, MQ register, index registers, indirect address

registers, etc.). Transfer from any source to any load, including transfers from one register to another, can take place along the single path labeled "BUS".