# DIGITAL 8000 SERIES TTL/MEMORY

#### DESCRIPTION

The 82S214 and 82S215 are Schottky-clamped Read Only Memories, incorporating on-chip data output registers.

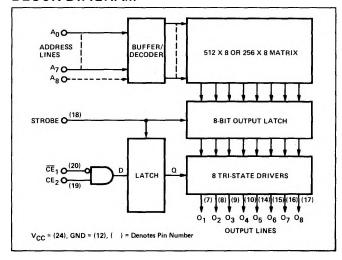

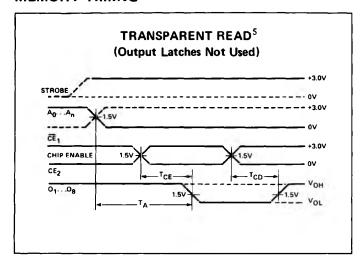

The 82S214 and 82S215 are fully TTL compatible, and include on-chip decoding and two chip enable inputs for ease of memory expansion. They feature Tri-State outputs for optimization of word expansion in bussed organizations. A D-type latch is used to enable the Tri-State output d ivers. In the TRANSPARENT READ mode, stored data is addressed by applying a binary code to the address inputs while holding STROBE high. In this mode the bit drivers will be controlled solely by CE1 and CE2 lines.

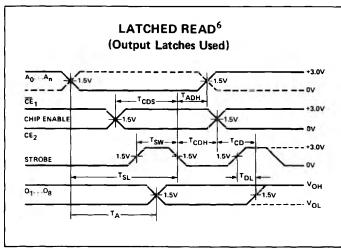

In the LATCHED READ mode, outputs are held in their previous state (1, 0, or high Z) as long as STROBE is low, regardless of the state of address or chip enable. A positive STROBE transition causes data from the applied address to reach the outputs if the chip is enabled, and causes outputs to go to the high Z state if the chip is disabled.

A negative STROBE transition causes outputs to be locked into their last Read Data condition if the chip was enabled, or causes outputs to be locked into the high Z condition if the chip was disabled.

Both 82S214 and 82S215 devices are available in the commercial and military temperature ranges. For the commercial temperature range (0°C to +75°C) specify N82S214/215 I. For the military temperature range (-55°C to +125°C) specify S82S214/215 I.

#### **FEATURES**

• ORGANIZATION:

82S214 - 256 X 8 82S215 - 512 X 8

ADDRESS ACCESS TIME:

S82S214/215 - 90ns, MAXIMUM N82S214/215 - 60ns, MAXIMUM

- **POWER DISSIPATION 165μW/BIT, TYPICAL**

- **INPUT LOADING:**

$$82$214/215 - (-150\mu A) MAXIMUM$  $N82S214/215 - (-100\mu A) MAXIMUM$

- **ON-CHIP STORAGE LATCHES**

- TRI-STATE OUTPUTS

- FULLY COMPATIBLE WITH 82S114 AND 82S115 **SIGNETICS PROMS**

### **APPLICATIONS**

**MICROPROGRAMMING** HARDWIRE ALGORITHMS **CHARACTER GENERATION** CONTROL STORE SEQUENTIAL CONTROLLERS

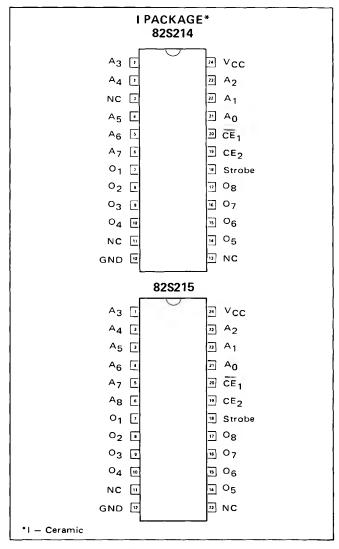

#### PIN CONFIGURATION

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER                                                     | RATING                      | UNIT     |

|------------------|---------------------------------------------------------------|-----------------------------|----------|

| V <sub>CC</sub>  | Power Supply Voltage                                          | +7                          | Vdc      |

| V <sub>IN</sub>  | Input Voltage                                                 | +5.5                        | Vdc      |

| TA               | Operating Temperature Range<br>(N82S214/215)<br>(S82S214/215) | 0° to +75°<br>-55° to +125° | °C<br>°C |

| T <sub>stg</sub> | Storage Temperature Range                                     | -65° to +150°               | °c       |

# **ELECTRICAL CHARACTERISTICS** N82S214/215 $-55^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +125 $^{\circ}$ C, 4.5V $\leq$ V<sub>CC</sub> $\leq$ 5.5 S82S214/215 $0^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +75 $^{\circ}$ C, 4.75V $\leq$ V<sub>CC</sub> $\leq$ 5.25

|   | PARAMETER        |                                | TEST CONDITIONS                                                                      | N82S214/215 |                  |      | S82S214/215 |                  |      |          |

|---|------------------|--------------------------------|--------------------------------------------------------------------------------------|-------------|------------------|------|-------------|------------------|------|----------|

|   |                  |                                |                                                                                      | MIN         | TYP <sup>2</sup> | MAX  | MIN         | TYP <sup>2</sup> | MAX  | UNIT     |

|   | l <sub>IL</sub>  | "0" Input Current              | V <sub>IN</sub> = 0.45V                                                              |             |                  | -100 |             |                  | -150 | μΑ       |

|   | I <sub>IH</sub>  | "1" Input Current              | V <sub>IN</sub> = 5.5V                                                               |             |                  | 25   |             |                  | 50   | μΑ       |

|   | VIL              | "0" Level Input Voltage        |                                                                                      |             |                  | .85  |             |                  | .8   | V        |

|   | V <sub>IH</sub>  | "1" Level Input Voltage        |                                                                                      | 2.0         |                  |      | 2.0         |                  |      | <b>v</b> |

|   | V <sub>IC</sub>  | Input Clamp Voltage            | I <sub>IN</sub> = - 18mA                                                             |             | -0.8             | -1.2 |             | -0.8             | -1.2 | V        |

|   | VOL              | "0" Output Voltage             | I <sub>OUT</sub> = 9.6mA                                                             |             |                  | 0.5  |             |                  | 0.5  | V        |

|   | V <sub>OH</sub>  | "1" Output Voltage             | CE <sub>1</sub> = "0", CE <sub>2</sub> = "1",<br>I <sub>OUT</sub> = -2mA, "1" STORED | 2.7         | 3.3              |      | 2.4         | 3.3              |      | V        |

|   | lo(off)          | HI-Z State Output Current      | CE <sub>1</sub> = "1" or CE <sub>2</sub> = 0,<br>V <sub>OUT</sub> = 5.5V             | i           |                  | 40   |             |                  | 100  | μΑ       |

|   |                  |                                | $\overline{CE_1}$ = "1" or $CE_2$ = 0,<br>$V_{OUT}$ = 0.5V                           |             |                  | -40  |             |                  | -100 | μΑ       |

| } | C <sub>IN</sub>  | Input Capacitance              | $V_{CC} = 5.0V, V_{IN} = 2.0V$                                                       |             | 5                | i    | }           | 5                |      | ρF       |

| , | C <sub>OUT</sub> | Output Capacitance             | $V_{CC}$ = 5.0V, $V_{OUT}$ = 2.0V<br>$\overline{CE}_1$ = "1" or $CE_2$ = 0           |             | 8                |      |             | 8                |      | ρF       |

|   | Icc              | V <sub>CC</sub> Supply Current |                                                                                      |             | 130              | 175  | {           | 130              | 185  | mA       |

|   | los              | Output Short Circuit Current   | $V_{OUT} = 0V$ (Note 3)                                                              | -20         |                  | -70  | - 15        |                  | -85  | mA       |

# **SWITCHING CHARACTERISTICS** N82S214/215 $-55^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +125 $^{\circ}$ C, 4.5V $\leq$ V<sub>CC</sub> $\leq$ 5.5V 882S214/215 $0^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +75 $^{\circ}$ C, 4.75V $\leq$ V<sub>CC</sub> $\leq$ 5.25V

|                  | DADAMETER               | TEST CONDITIONS                                              | N82S214/215 |                  |     | S82S214/215 |                  |     |      |

|------------------|-------------------------|--------------------------------------------------------------|-------------|------------------|-----|-------------|------------------|-----|------|

|                  | PARAMETER               |                                                              | MIN         | TYP <sup>2</sup> | MAX | MIN         | TYP <sup>2</sup> | MAX | UNIT |

| TAA              | Address Access Time     | LATCHED or TRANSPARENT READ                                  |             | 35               | 60  |             | 35               | 90  | ns   |

| T <sub>CE</sub>  | Chip Enable Access Time | $R_1 = 470\Omega$ , $R_2 = 1k\Omega$ , $C_L = 30pF$ (Note 4) |             | 20               | 40  |             | 20               | 50  | ns   |

| T <sub>CD</sub>  | Chip Disable Time       |                                                              |             | 20               | 40_ |             | 20               | 50  | ns   |

| TADH             | Address Hold Time       |                                                              | 0           | -10              |     | 5           | -10              |     | ns   |

| T <sub>CDH</sub> | Chip Enable Hold Time   |                                                              | 10          | 0                |     | 10          | 0                |     | ns   |

| $T_{SW}$         | Strobe Pulse Width      | LATCHED READ ONLY                                            | 30          | 20               |     | 40          | 20               |     | ns   |

| T <sub>SL</sub>  | Strobe Latch Time       | $R_1 = 470\Omega$ , $R_2 = 1k\Omega$ , $C_L = 30pF$          | 60          | 35               |     | 90          | 35               |     | ns   |

| TDL              | Strobe Delatch Time     | (Note 5)                                                     |             |                  | 30  |             |                  | 35  | ns   |

| T <sub>CDS</sub> | Chip Enable Set-up Time |                                                              | 40          |                  |     | 50          |                  |     | ns   |

#### NOTES

- 1. Positive current is defined as into the terminal referenced.

- 2. Typical values are at  $V_{CC} = +5.0V$  and  $T_A = +25^{\circ}C$ .

- 3. No more than one output should be grounded at the same time and strobe should be disabled. Strobe is in "1" state.

- 4. If the strobe is high, the device functions in a manner idential to conventional bipolar ROMs. The timing diagram shows valid data will appear T<sub>A</sub> nanoseconds after the address has changed and T<sub>CE</sub> nanoseconds after the output circuit is enabled. T<sub>CD</sub> is the time required to disable the output and switch it to an "off" or high impedance state after it has been enabled.

- 5. In Latched Read Mode data from any selected address will be held on the output when strobe is lowered. Only when strobe is raised will new location data be transferred and chip enable conditions be stored. The new data will appear on the outputs if the chip enable conditions enable the outputs.

## **MEMORY TIMING**

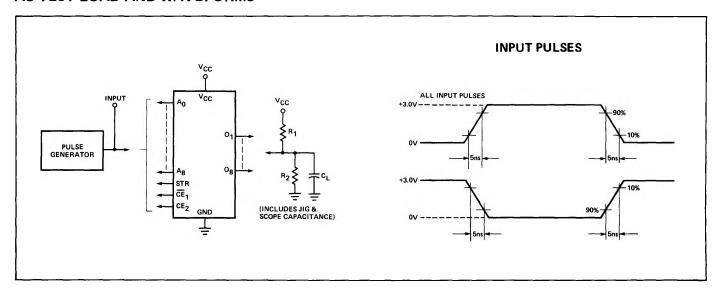

## **AC TEST LOAD AND WAVEFORMS**