# DIGITAL 8000 SERIES TTL/MEMORY

## DESCRIPTION

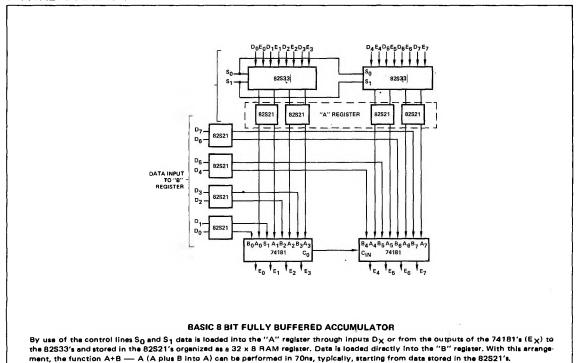

The 82S21 is a TTL 64 bit Write-While-Read Random Access Memory organized in 32 words of 2 bits each. The 82S21 is ideally suited for high speed buffers and as the memory element in high speed accumulators.

Words are selected through a 5 input decoder when the Read-Write enable input, CE is at logic "1".  $\overline{W_0}$  and  $\overline{W_1}$  are the write inputs for bit 0 and bit 1 of the word selected.  $\overline{C}$  is the write control input. When  $\overline{W_X}$  and  $\overline{C}$  are both at logic "0" data on the  $I_0$  and  $I_1$  data lines are written into the addressed word. The read function is enabled when either  $\overline{W_X}$  or  $\overline{C}$  is at logic "1".

An internal latch is on the chip to provide the Write-While-Read capability. When the latch control line,  $\overline{L}$ , is logic "1" and data is being read from the 82S21, the latch is effectively bypassed. The data at the output will be that of the addressed word. When  $\overline{L}$  goes from a logic "1" to logic "0" the outputs are latched and will remain latched regardless of the state of any other address or control line. When  $\overline{L}$  goes from "0" to "1" the outputs unlatch and the outputs will be that of the present address word.

#### FEATURES

- BUFFERED ADDRESS LINES

- ON CHIP LATCHES

- ON CHIP DECODING

- BIT MASKING CONTROL LINES

- ENABLE CONTROL LINE

- OPEN COLLECTOR OUTPUTS WITH 40mA CAPABILITY

- PROTECTED INPUTS

- VERY HIGH SPEEDS (25ns TYP)

# APPLICATIONS SCRATCH PAD MEMORY BUFFER MEMORY ACCUMULATOR REGISTER CONTROL STORE

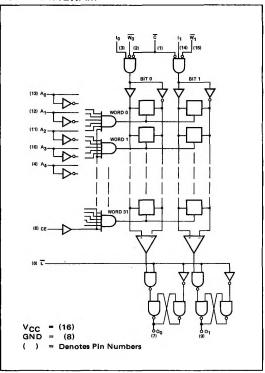

#### LOGIC DIAGRAM

# TRUTH TABLE

| CE | $\overline{C}$ $\overline{W_0}$ $\overline{W_1}$ $\overline{L}$ Mode |   | Mode | Outputs |                            |                                                                                                                  |

|----|----------------------------------------------------------------------|---|------|---------|----------------------------|------------------------------------------------------------------------------------------------------------------|

| X  | Х                                                                    | × | х    | 0       | Output Hold                | Data from last addressed word when CE = "1"                                                                      |

| 0  | х                                                                    | × | ×    | 1       | Read & Write Disabled      | Disabled logic "1"                                                                                               |

| 1  | 1                                                                    | х | ×    | x       | Read                       | Data stored in addressed word                                                                                    |

| 1  | 0                                                                    | 1 | 1    | x       | Read                       | Data stored in addressed word                                                                                    |

| 1  | 0                                                                    | 0 | 0    | 0       | Write Data                 | Data from last word address when L went from "1" to "0"                                                          |

| 1  | 0                                                                    | 0 | 0    | 1       | Write Data                 | Data being written into memory                                                                                   |

| 1  | 0                                                                    | 0 | 1    | ×       | Write Data into Bit 0 Only | If $\overline{L}$ = 0: Data from last word address when L went from "1" to "0"                                   |

| 1  | 0                                                                    | 1 | 0    | ×       | Write Data into Bit 1 Only | If $\overline{L} = 1$ : Data being written into the selected bit location and stored in other addressed location |

# ELECTRICAL CHARACTERISTICS (0°C < TA < 75°C; 4.75V < VCC < 5.25)

|                                | LIMITS |      |         |       |                         |       |

|--------------------------------|--------|------|---------|-------|-------------------------|-------|

| CHARACTERISTICS                | MIN.   | TYP. | MAX.    | UNITS | TEST CONDITIONS         | NOTES |

| "0" Output Voltage             |        |      | .45     | ٧     | V <sub>out</sub> = 40mA |       |

| "1" Output Leakage Current     |        |      | 40      | μА    | V <sub>out</sub> = 5.5V |       |

| "0" Input Current (All Inputs) | ł      |      | -1.6    | mA    | V <sub>in</sub> = 0.5V  |       |

| "1" Input Current (All Inputs  |        |      | 25      | μΑ    | V <sub>in</sub> = 2.4V  |       |

|                                | )      | Ì    | 100     | μА    | V <sub>in</sub> = 5.5V  |       |

| Input "0" Threshold Voltage    |        |      | 0.85    | v     |                         |       |

| Input "1" Threshold Voltage    | 2.0    | ļ    |         | V     |                         |       |

| Power Consumption              |        |      | 130/683 | mA/mW |                         |       |

# ELECTRICAL CHARACTERISTICS (TA = 25°C; VCC = 5.0V)

|                                    |                | LIMITS  |            |       |                 |       |          |

|------------------------------------|----------------|---------|------------|-------|-----------------|-------|----------|

| CHARACTERISTICS                    | MIN.           | TYP. 25 | MAX.<br>50 | UNITS | TEST CONDITIONS | NOTES |          |

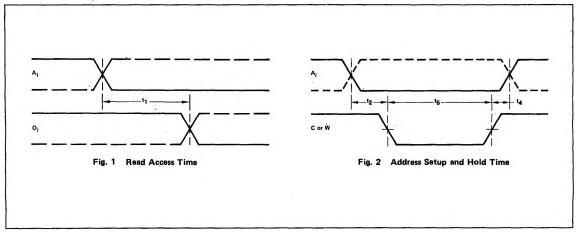

| Read Access Time Address to Output | t <sub>1</sub> |         |            |       |                 |       |          |

| Address Set-Up Time                | t <sub>2</sub> |         | 8          | 15    | ns              |       | <b>!</b> |

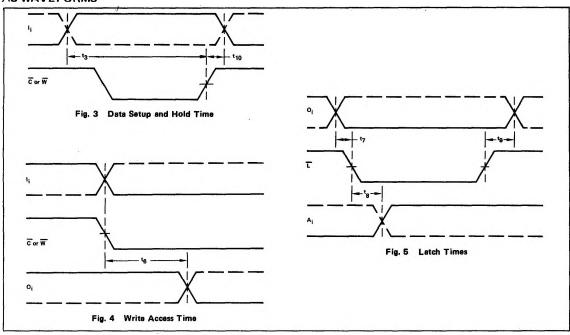

| Data Set-Up Time                   | tg             |         | 15         | 20    | ns              |       |          |

| Address to Address Hold Time       | t4             |         | 0          | 0     | ns              |       |          |

| Control or Write Pulse Width       | t <sub>5</sub> | 20      | 15         | ĺ     | ns              |       | ł        |

| Write Access Time                  | t <sub>6</sub> |         | 20         | 25    | ns              |       |          |

| Address to Latch Set-Up Time       | t7             |         | 25         | 50    | ns              | İ     | 1        |

| Latch Address to Address Hold Time | tg             |         | 7          | 10    | ns              |       |          |

| Delatch Access Time                | tg.            |         | 15         | 25    | ns              |       |          |

| Data Hold Time Earliest            | t10            |         | 0          | 5     | ns              |       |          |

## NOTES:

- 1. Positive current is defined as into the Terminal.

- No more than one output should be grounded at the same time.

- Applied voltages must not exceed 5.5V.

Input current must not exceed ±12 mA.

- Output current must not exceed  $\pm 100$  mA. Storage temperature must be within the  $-60^{\circ}$ C to  $+150^{\circ}$ C range.

- Manufacturer reserves the right to make design and process changes and improvements.

# **AC WAVEFORMS**

# **AC WAVEFORMS**

# **EYPICAL APPLICATION**