82S130-F.N • 82S131-F.N

#### DESCRIPTION

The 82S130 and 82S131 are field programmable, which means that custom patterns are immediately available by following the fusing procedure given in this data sheet. The standard 82S130 and 82S131 are supplied with all outputs at logical low. Outputs are programmed to a logic high level at any specified address by fusing a Ni-Cr link matrix.

These devices include on-chip decoding and 1 chip enable input for ease of memory expansion. They feature either open collector or tri-state outputs for optimization of word expansion in bused organizations.

Both 82S130 and 82S131 devices are available in the commercial and military temperature ranges. For the commercial temperature range (0° to +75°C) specify N82S130/131, F or N, and for the military temperature range (-55°C to +125°C) specify S82S130/131, F.

## **FEATURES**

- Address access time: N82S130/131: 50ns max S82S130/131: 70ns max

- Power dissipation: 0.3mW/bit typ

- Input loading:

- N82S130/131: -100μA max S82S130/131: -150μA max

- On-chip address decoding

- Output options: 82S130: Open collector

- 82S131: Tri-state

- No separate fusing pins

- Unprogrammed outputs are low level

- Fully TTL compatible

# **APPLICATIONS**

- Prototyping/volume production

- Sequential controllers

- Microprogramming

- Hardwired algorithms

- Control store

- Random logic

- Code conversion

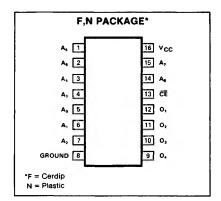

## PIN CONFIGURATION

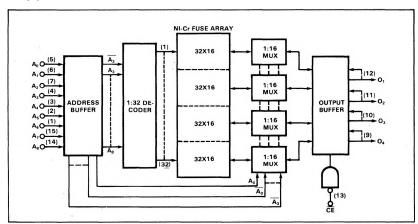

## **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

|       | PARAMETER          | RATING      | UNIT |

|-------|--------------------|-------------|------|

| Vcc   | Supply voltage     | +7          | Vdc  |

| VIN   | Input voltage      | +5.5        | Vdc  |

|       | Output voltage     | ]           | Vdc  |

| Vон   | High (82S130)      | +5.5        |      |

| Vo    | Off-state (82S131) | +5.5        |      |

|       | Temperature range  |             | l °c |

| $T_A$ | Operating          |             | 1    |

|       | N82S130/131        | 0 to +75    |      |

|       | S82S130/131        | -55 to +125 | }    |

| TSTG  | Storage            | -65 to +150 |      |

82S130-F,N • 82S131-F,N

DC ELECTRICAL CHARACTERISTICS N82S130/131:  $0^{\circ}C \le T_{A} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

S82S130/131:  $-55^{\circ}$ C  $\leq T_{A} \leq +125^{\circ}$ C, 4.5V  $\leq V_{CC} \leq 5.5$ V

| PARAMETER                           |                                                                                     | TEST CONDITIONS                                                                                                                                                                                     | N82S130/131 |              |                        | S82S130/131 |        |                        |                |

|-------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|------------------------|-------------|--------|------------------------|----------------|

|                                     |                                                                                     | TEST CONDITIONS                                                                                                                                                                                     |             | Min Typ¹ Max |                        | Min Typ1    |        | Max                    | UNIT           |

| VIL<br>VIH<br>VIC                   | Input voltage<br>Low<br>High<br>Clamp                                               | I <sub>IN</sub> = -18mA                                                                                                                                                                             | 2.0         | -0.8         | .85<br>-1.2            | 2.0         | 0.8    | .80<br>-1.2            | V              |

| V <sub>OL</sub><br>V <sub>OH</sub>  | Output voltage<br>Low<br>High (82S131)                                              | I <sub>OUT</sub> = 16mA<br><del>CE</del> = low, I <sub>OUT</sub> = -2mA high stored                                                                                                                 | 2.4         |              | 0.45                   | 2.4         |        | 0.5                    | ٧              |

| liL<br>liH                          | Input current<br>Low<br>High                                                        | V <sub>IN</sub> = 0.45V<br>V <sub>IN</sub> = 5.5V                                                                                                                                                   |             | 40<br>.85    |                        |             |        | -150<br>50             | μА             |

| IOLK<br>IO(OFF)                     | Output current<br>Leakage (82S130)<br>Hi-Z state (82S131)<br>Short circuit (82S131) | $\overline{\text{CE}}$ = high, $V_{\text{OUT}}$ = 5.5V<br>$\overline{\text{CE}}$ = high, $V_{\text{OUT}}$ = 5.5V<br>$\overline{\text{CE}}$ = high, $V_{\text{OUT}}$ = 0.5V<br>$V_{\text{OUT}}$ = 0V | -20         | <i>9</i> 2   | 40<br>40<br>-40<br>-70 | -15         |        | 60<br>60<br>-60<br>-85 | μA<br>μA<br>mA |

| Icc                                 | V <sub>CC</sub> supply current                                                      |                                                                                                                                                                                                     |             | 120          | 140                    |             | 120    | 140                    | mA             |

| C <sub>IN</sub><br>C <sub>OUT</sub> | Capacitance<br>Input<br>Output                                                      | V <sub>IN</sub> = 2.0V, V <sub>CC</sub> = 5.0V                                                                                                                                                      |             | 5<br>8       |                        |             | 5<br>8 |                        | pF             |

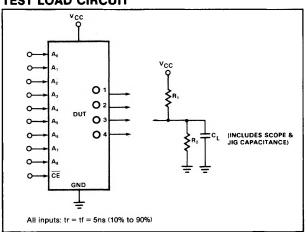

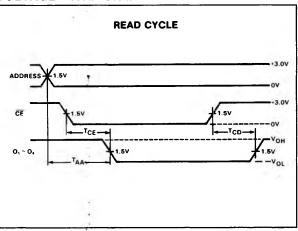

# AC ELECTRICAL CHARACTERISTICS $R_1 = 270\Omega, R_2 = 600\Omega, C_L = 30 pF^2$

N82S130/131:  $0^{\circ} \le T_A \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

S82S130/131:  $-55^{\circ}$ C  $\leq T_{A} \leq +125^{\circ}$ C, 4.5V  $\leq V_{CC} \leq 5.5$ V

| PARAMETER       |              | то     | FROM         | N82S130/131 |          |     | S82S130/131 |      |     |      |

|-----------------|--------------|--------|--------------|-------------|----------|-----|-------------|------|-----|------|

|                 |              |        |              | Min         | Typ¹ Ma: | Max | Min         | Typ1 | Max | UNIT |

|                 | Access time  |        | <del></del>  | 1           |          |     |             |      |     | ns   |

| TAA             |              | Output | Address      |             | 40       | 50  |             | 40   | 70  |      |

| TCE             |              | Output | Chip enable  |             | 20       | 30  |             | 20   | 40  |      |

|                 | Disable time |        |              | 1           |          |     |             |      |     | ns   |

| T <sub>CD</sub> |              | Output | Chip disable |             | 20       | 30  |             | 20   | 40  |      |

### NOTES

- 1. Typical values are at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = +25°C.

- 2. Positive current is defined as into the terminal referenced.

# **TEST LOAD CIRCUIT**

## **VOLTAGE WAVEFORM**

82S130-F,N • 82S131-F,N

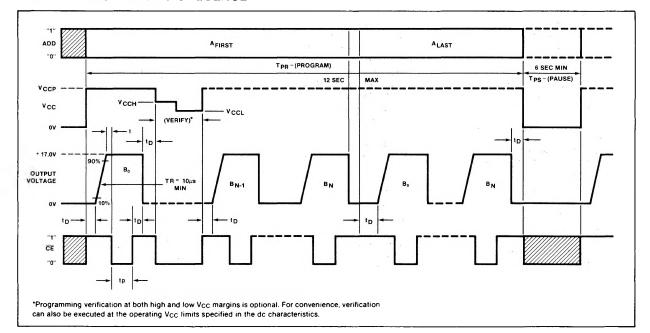

## PROGRAMMING SYSTEMS SPECIFICATIONS (Testing of these limits may cause programming of device.) T<sub>A</sub> = +25°C

|                                      |                                                 | TEAT CONDITIONS                                             |            |            |            |       |  |

|--------------------------------------|-------------------------------------------------|-------------------------------------------------------------|------------|------------|------------|-------|--|

| PARAMETER                            |                                                 | TEST CONDITIONS                                             | Min        | Тур        | Max        | UNIT  |  |

| VCCP                                 | Power supply voltage<br>To program <sup>1</sup> | I <sub>CCP</sub> = 375 ± 75mA,<br>Transient or steady state | 8.5        | 8.75       | 9.0        | ٧     |  |

| V <sub>CCH</sub><br>V <sub>CCL</sub> | Verify limit<br>Upper<br>Lower                  |                                                             | 5.3<br>4.3 | 5.5<br>4.5 | 5.7<br>4.7 | V     |  |

| Vs                                   | Verify threshold <sup>2</sup>                   |                                                             | 1.4        | 1.5        | 1.6        | V     |  |

| ICCP                                 | Programming supply current                      | $V_{CCP} = +8.75 \pm .25V$                                  | 300        |            | 450        | mA    |  |

| V <sub>IH</sub><br>V <sub>IL</sub>   | Input voltage<br>High<br>Low                    |                                                             | 2.4<br>0   | 0.4        | 5.5<br>0.8 | V     |  |

| lın<br>lır                           | Input current<br>High<br>Low                    | V <sub>IH</sub> = +5.5V<br>V <sub>IL</sub> = +0.4V          |            |            | 50<br>-500 | μΑ    |  |

| Vout                                 | Output programming voltage <sup>3</sup>         | I <sub>OUT</sub> = 200 ± 20mA,<br>Transient or steady state | 16.0       | 17.0       | 18.0       | ٧     |  |

| lout                                 | Output programming current                      | $V_{OUT} = +17 \pm 1V$                                      | 180        | 200        | 220        | mA    |  |

| $T_{R}$                              | Output pulse rise time                          |                                                             | 10         |            | 50         | μs    |  |

| tp                                   | CE programming pulse width                      |                                                             | 0.3        | 0.4        | 0.5        | ms    |  |

| tD                                   | Pulse sequence delay                            |                                                             | 10         |            |            | μs    |  |

| TPR                                  | Programming time                                | V <sub>CCP</sub> = V <sub>CCP</sub>                         |            |            | 12         | sec   |  |

| T <sub>PSI</sub>                     | Initial programming pause                       | V <sub>CC</sub> = 0V                                        | 6          |            |            | sec   |  |

| T <sub>PR</sub>                      | Programming duty cycle4                         |                                                             |            |            | 50         | %     |  |

| FL                                   | Fusing attempts per link                        |                                                             |            |            | 2          | cycle |  |

### NOTES

- 1. Bypass VCC to GND with a 0.01 µF capacitor to reduce voltage spikes.

- VS is the sensing threshold of the PROM output voltage for a programmed bit. It normally constitutes the reference voltage applied to a comparator circuit to verify a successful fusing attempt.

- Care should be taken to insure the 17± 1V output voltage is maintained during the entire fusing cycle.

The recommended supply is a constant current source clamped at the specified voltage limit.

- 4. Programming duty cycle is 50% after continuous programming at 100% duty cycle.

- This is an updated method of programming and does not obsolete any programming systems presently being used.

# PROGRAMMING PROCEDURE

- Terminate all device outputs with a 10K resistor to V<sub>CC</sub>. Apply CE<sub>1</sub> = High.

- 2. Select the Address to be programmed, and raise Vcc to Vccp = 8.75 ± .25V.

- 3. After  $10\mu$ s delay, apply  $V_{OUT} = +17 \pm 1V$  to the output to be programmed. Program one output at the time.

- 4. After 10μs delay, pulse the CE<sub>1</sub> input to

- logic low for 0.3 to 0.5ms.

- After 10µs delay, remove +17V from the programmed output.

- 6. To verify programming, after 10µs delay, lower V<sub>CC</sub> to V<sub>CCH</sub> = +5.5 ± .2V, and apply a logic low level to the CE input. The programmed output should remain in the high state. Again, lower V<sub>CC</sub> to V<sub>CCL</sub> = +4.5 ± .2V, and verify that the pro-

- grammed output remains in the high state.

- Raise V<sub>CC</sub> to V<sub>CCP</sub> = 8.75 ± .25V, and repeat steps 3 through 6 to program other bits at the same address.

- After 10 μs delay, repeat steps 2 through 7 to program all other address locations.

82S130-F,N • 82S131-F,N

# **TYPICAL PROGRAMMING SEQUENCE**