### DESCRIPTION

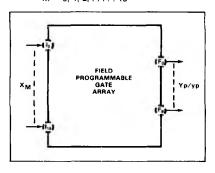

The 82S102 and 82S103 are Bipolar programmable AND/NAND gate arrays, containing 9 gates sharing 16 common inputs. On-chip input buffers enable the user to individually program for each gate either the True ( $I_m$ ), Complement ( $\overline{I_m}$ ), or Don't Care (X) logic state of each input. In addition, the polarity of each gate output is individually programmable to implement either AND or NAND logic functions.

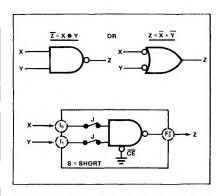

Alternately, if desired, OR/NOR logic functions can also be realized by programming for each gate the complement of its input variables, and output (DeMorgan theorem).

Both devices are field-programmable, which means that custom patterns are immediately available by following the fusing procedure outlined in this data sheet.

The 82S102 and 82S103 include chipenable control for output strobing and inhibit. They feature either open collector or tri-state outputs for ease of expansion of input variables and application in busorganized systems.

Both devices are available in the commercial and military temperature ranges. For the commercial range (0°C to +75°C) specify N82S102/103, I or N, and for the military range (-55°C to +125°C) specify S82S102/103, I.

#### **FEATURES**

- Field programmable (Ni-Cr link)

- 16 input variables

- 9 output functions

- Chip enable input

- I/O propagation delay: N82S102/103: 30ns max S82S102/103: 50ns max

- Power dissipation: 600mW typ

- . Input loading:

- N82S102/103: -100μA max S82S102/103: -150μA max

- Output options:

- 82S102: Open collector 82S103: Tri-state

- Output disable function:

82\$102: HI

82\$103: HI-Z

- Fully TTL compatible

#### **APPLICATIONS**

- Random logic

- Address decoders

- Code detectors

- Peripheral selectors

- Fault monitors

- Machine state decoders

# PIN CONFIGURATION

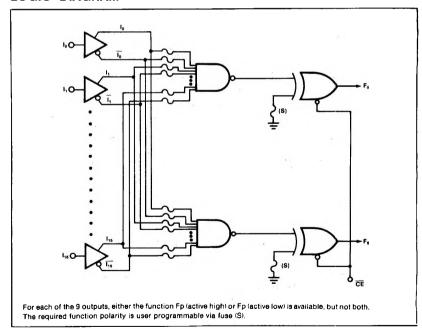

#### LOGIC DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**

|      | PARAMETER          | RATING      | UNIT |

|------|--------------------|-------------|------|

| v    | cc Supply voltage  | +7          | Vdc  |

| v    | in Input voltage   | +5.5        | Vdc  |

| 1    | Output voltage     |             | Vdc  |

| V.   | он High (82S102)   | +5.5        |      |

| V.   | Off-state (82S103) | +5.5        |      |

| l tu | N Input current    | ±30         | mA   |

| lo   | Output current     | +100        | mA   |

|      | Temperature range  |             | °C   |

| Т.   | A Operating        |             |      |

| 1    | N82S102/103        | 0 to +75    |      |

|      | S82S102/103        | -55 to +125 |      |

| Т:   | STG Storage        | -65 to +150 |      |

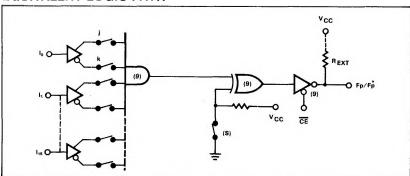

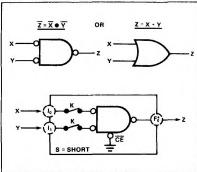

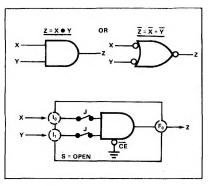

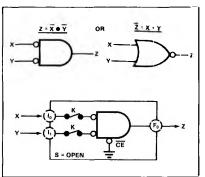

### **EQUIVALENT LOGIC PATH**

The Field Programmable Gate Array consists of 9 gates with individually programmable inputs and outputs.

The inputs to each gate can be programmed either True (Im), Complement (Im), or Don't Care via corresponding links (j) and (k). The outputs of each gate can be programmed active-high (Fp) or active-low (Fp) via corresponding links (S). Thus, each gate provides either of 2 output logic functions in terms of external input logic variables Xm as defined below (positive logic):

$$\begin{array}{l} \text{At S} = \text{Open:} \\ Fp = \overline{CE} + (X_0 \bullet X_1 \bullet X_2 \bullet \ldots Xm) = \text{Yp} \\ \text{At S} = \underline{Closed:} \\ F\mathring{p} = \overline{CE} + (\overline{X}_0 + \overline{X}_1 + \overline{X}_2 + \ldots X_m) = \text{yp} \\ m = 0, 1, 2, \ldots ... 15 \end{array}$$

$p = 0, 1, 2, \ldots, 8$ and where  $X_m = I_m$ ,  $\overline{I_m}$ , Don't Care, as assigned by programming polarity of inputs

When CE = low, all gates are enabled, and  $F_{o}^{*} = \overline{F}_{p}$  giving  $y_{p} = \overline{Y}_{p}$ .

# **PROGRAMMABLE LOGIC FUNCTIONS**

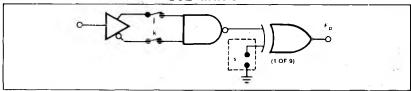

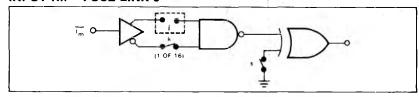

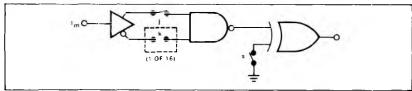

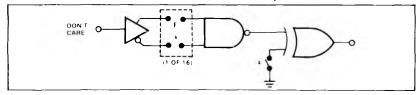

All internal links of virgin FPGAs are intact. Therefore, as shown in the Equivalent Logic Path, all symbolic switches are initially closed. Selective programming (opening) of links (J), (K), and (S) enables the user to assign input and output polarities to each gate for implementing NAND, NOR, AND, OR logic functions without changing the routing of input and output wires. This is shown in the following diagrams for a typical gate in terms of 2 input variables, which can be readily extended up to 16.

# BIPOLAR FIELD PROGRAMMABLE GATE ARRAY (16X9) 82S102 (0.C.)/82S103 (T.S.)

82S102-I,N • 82S103-I,N

DC ELECTRICAL CHARACTERISTICS N82S102/103:  $0^{\circ}$ C  $\leq$  TA  $\leq$  +75 $^{\circ}$ C, 4.75V  $\leq$  VcC  $\leq$  5.25V S82S102/103:  $-55^{\circ}$ C  $\leq T_{A} \leq +125^{\circ}$ C, 4.5V  $\leq V_{CC} \leq 5.5$ V

|                                    | DADAMETER                                                                                                                     | TEST COMPLETIONS                                                                                                                 | NE  | 325102/1         | 03                     | SE  | 325102/1         | 03                     | UNIT           |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------------------|------------------------|-----|------------------|------------------------|----------------|

|                                    | PARAMETER <sup>1</sup>                                                                                                        | TEST CONDITIONS                                                                                                                  | Min | Typ <sup>2</sup> | Max                    | Min | Typ <sup>2</sup> | Max                    | UNIT           |

| V <sub>IL</sub><br>V <sub>IH</sub> | Input voltage<br>Low <sup>1</sup><br>High <sup>1</sup>                                                                        | V <sub>CC</sub> = Min<br>V <sub>CC</sub> = Max                                                                                   | 2.0 |                  | 0.85                   | 2.0 |                  | 0.8                    | V              |

| VIC                                | Clamp <sup>1,3</sup>                                                                                                          | $V_{CC} = Min, I_{IN} = -18mA$                                                                                                   | 2.0 | -0.8             | -1.2                   | 1   | -0.8             | -1.2                   | ļ              |

| V <sub>OL</sub><br>V <sub>OH</sub> | Output voltage<br>Low1,4<br>High (82S103)1,5                                                                                  | $V_{CC} = Min$ $I_{OL} = 9.6mA$ $I_{OH} = -2mA$                                                                                  | 2.4 | 0.35             | 0.45                   | 2.4 | 0.35             | 0.50                   | ٧              |

| lit<br>lin                         | Input current<br>Low<br>High                                                                                                  | V <sub>IN</sub> = 0.45V<br>V <sub>IN</sub> = 5.5V                                                                                |     | -10<br><1        | -100<br>25             |     | -10<br><1        | -150<br>50             | μΑ             |

| IOLK<br>IO(OFF)<br>IOS             | Output current<br>Leakage (82S102) <sup>6</sup><br>Hi-Z state (82S103) <sup>6</sup><br>Short circuit (82S103) <sup>3</sup> ,7 | V <sub>CC</sub> = Max<br>V <sub>OUT</sub> = 5.5V<br>V <sub>OUT</sub> = 5.5V<br>V <sub>OUT</sub> = 0.45V<br>V <sub>OUT</sub> = 0V | -20 | 1 1 -1           | 40<br>40<br>-40<br>-70 | -15 | 1<br>1<br>-1     | 60<br>60<br>-60<br>-85 | μΑ<br>μΑ<br>mA |

| lcc                                | V <sub>CC</sub> supply current <sup>8</sup>                                                                                   | V <sub>CC</sub> = Max                                                                                                            |     | 120              | 170                    |     | 120              | 180                    | mA             |

| C <sub>IN</sub><br>Cout            | Capacitance<br>Input<br>Output <sup>s</sup>                                                                                   | $V_{CC} = 5.0V$ $V_{IN} = 2.0V$ $V_{OUT} = 2.0V$                                                                                 |     | 8<br>15          |                        |     | 8<br>15          |                        | pF             |

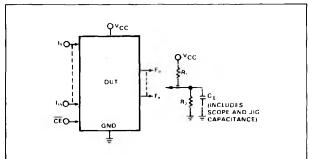

# AC ELECTRICAL CHARACTERISTICS $R_1 = 470\Omega, R_2 = 1k\Omega, C_L = 30pF$

N82S102/103:  $0^{\circ}$  C  $\leq$  T<sub>A</sub>  $\leq$  +75 $^{\circ}$  C, 4.75V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V S82S102/103:  $-55^{\circ}$ C  $\leq T_{A} \leq +125^{\circ}$ C, 4.5V  $\leq V_{CC} \leq 5.5$ V

|                 |                                     |                  |                      | N8  | 2S102/1          | 03       | S8  | UNIT             |          |      |

|-----------------|-------------------------------------|------------------|----------------------|-----|------------------|----------|-----|------------------|----------|------|

| P.              | ARAMETER                            | то               | FROM                 | Min | Typ <sup>2</sup> | Max      | Min | Typ <sup>2</sup> | Max      | ואטן |

| T <sub>IA</sub> | Access time<br>Input<br>Chip enable | Output<br>Output | Input<br>Chip enable |     | 20<br>15         | 30<br>30 |     | 20<br>15         | 50<br>40 | ns   |

| T <sub>CD</sub> | Disable time<br>Chip disable        | Output           | Chip enable          |     | 15               | 30       |     | 15               | 40       | ns   |

#### NOTES

- 1. All voltage values are with respect to network ground terminal.

- 2. All typical values are at Vcc = 5V, TA = 25°C.

- 3. Test each output one at a time.

- Measured with a programmed logic condition for which the output under test is at a low logic level. Output sink current is supplied through a resistor to Vcc.

- Measured with VIL applied to CE and a logic high at the output.

- 6. Measured with VIH applied to CE.

- Duration of short circuit should not exceed 1 second.

- 8. Icc is measured with the chip enable input grounded, all other inputs at 4.5V and the outputs open.

# **TEST LOAD CIRCUIT**

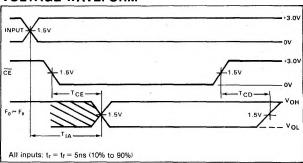

# **VOLTAGE WAVEFORM**

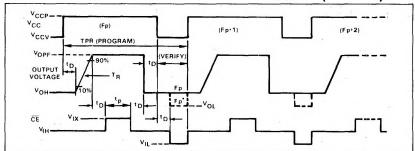

# **OUTPUT POLARITY PROGRAM-VERIFY SEQUENCE (TYPICAL)**

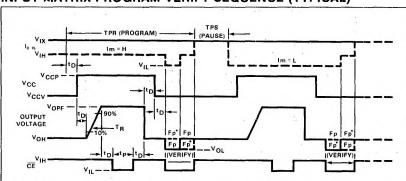

# INPUT MATRIX PROGRAM-VERIFY SEQUENCE (TYPICAL)

### **VIRGIN DEVICE**

The 82S102/103 are shipped in an unprogrammed state, characterized by:

- 1. All internal Ni-Cr links are intact.

- Each gate contains both true and complement values of every input variable I<sub>m</sub> (logic Null state).

- 3. The polarity of each output is set to active low (F<sub>0</sub>\* function).

- 4. All outputs are at a high logic level.

# RECOMMENDED PROGRAMMING PROCEDURE

To program each of 9 Boolean logic functions of 16 True, Complement, or Don't Care input variables follow the program/verify procedures for the Input Matrix and Output Polarity outlined below. To maximize recovery from programming errors, leave all links of unused gates intact.

#### SET-UP

Terminate all device outputs with a 10K $\Omega$  resistor to +5V.

# **Output Polarity**

PROGRAM ACTIVE HIGH (Fp FUNCTION)

Program output polarity before programming inputs (for convenience). Program one output at a time. (S) links of unused outputs are not required to be fused.

- 1 . Set GND (pin 14) to 0V, and V<sub>CC</sub> (pin 28) to V<sub>CC</sub>V.

- 2. Disable all device outputs by setting  $\overline{\text{CE}}$  (pin 19) to V<sub>IH</sub>.

- 3. Disable all input variables by applying V<sub>IX</sub> to inputs I<sub>0</sub> through I<sub>15</sub>.

- A.Raise Vcc (pin 28) from Vccv to Vccp.

- B After to delay, force output to be programmed to VOPF.

- C . After  $t_D$  delay, pulse the  $\overline{CE}$  input from  $V_{IH}$  to  $V_{IX}$  for a period  $t_p$ .

- D.After t<sub>D</sub> delay, remove V<sub>OPF</sub> voltage source from output being programmed.

- E. After to delay, return VCC (pin 28) to VCCV, and verify.

- F. Repeat steps A through E for any other output.

# **VERIFY OUTPUT POLARITY**

- 1. Set GND (pin 14) to 0V, and V<sub>CC</sub> (pin 28) to V<sub>CCV</sub>.

- 2. Disable all input variables by applying  $V_{IX}$  to inputs  $I_0$  through  $I_{15}$ .

- A .After t<sub>D</sub> delay, set the CE input to V<sub>IL</sub>.

- B. Verify output polarity by sensing the logic state of outputs F<sub>0</sub> through F<sub>8</sub>. All outputs at a low logic level are programmed active low (F<sub>p</sub> function), while all outputs at a high logic level are programmed active high (F<sub>p</sub> function).

# Input Matrix PROGRAM INPUT VARIABLE

Program one input at a time for one gate at a time. Input variable links of unused gates are not required to be fused. However, unused input variables must be programmed at Don't Care for all used gates.

- 1. Set GND (pin 14) to 0V, and V<sub>CC</sub> (pin 28) to V<sub>CCV</sub>.

- Disable all device outputs by setting <del>CE</del> (pin 19) to V<sub>IH</sub>.

- 3. Disable all input variables by applying  $V_{1X}$  to inputs  $I_0$  through  $I_{15}$ .

- A-1.If a gate contains nether  $l_0$  nor  $\overline{l_0}$  (input is a Don't Care), fuse both j and k links by executing both steps A-2 and A-3, before continuing with step C.

- A-2.If a gate contains  $I_0$ , set to fuse the k link by lowering the input voltage at  $I_0$  from  $V_{IX}$  to  $V_{IH}$ . Execute step B.

- A -3.If a gate contains  $\overline{l_0}$ , set to fuse the j link by lowering the input voltage at  $l_0$  from  $V_{IX}$  to  $V_{IL}$ . Execute step B.

- B-1.After to delay, raise Vcc from Vccv to Vccp.

- B-2.After to delay, force output of gate to be programmed to VOPF.

- B-3.After t<sub>D</sub> delay, pulse the CE input from V<sub>IH</sub> to V<sub>IL</sub> for a period t<sub>p</sub>.

- B-4.After t<sub>D</sub> delay, remove V<sub>OPF</sub> voltage source from output of gate being programmed.

- B-5.After to delay, return V<sub>CC</sub> (pin 28) to V<sub>CCV</sub>, and verify.

- C. Disable programmed input by returning I<sub>0</sub> to V<sub>IX</sub>.

- Repeat steps A through C for all other input variables.

- E. Repeat steps A through D for all other gates to be programmed.

- F. Remove V<sub>IX</sub> from all input variables.

# **VERIFY INPUT VARIABLE**

Unambiguous verification of the logic state programmed for the inputs of each gate requires prior knowledge of its programmed output polarity. Therefore, the output polarity verify procedure must precede input variable verify.

- 1. Set GND (pin 14) to 0V, and V<sub>CC</sub> (pin 28) to V<sub>CC</sub>V.

- 2. Enable all outputs by setting  $\overline{CE}$  (pin 19) to  $V_{II}$ .

- 3. Disable all input variables by applying  $V_{IX}$  to inputs  $I_0$  through  $I_{15}$ .

- A .Interrogate input variable  $I_0$  as follows: Lower the input voltage to  $I_0$  from  $V_{IX}$  to  $V_{IL}$ , and sense the logic state of outputs  $F_{0-8}$ .

Raise the input voltage to  $I_0$  from  $V_{IL}$  to  $V_{IH}$  and sense the logic state of outputs  $F_{0-8}$ .

# BIPOLAR FIELD PROGRAMMABLE GATE ARRAY (16X9)

82\$102 (O.C.)/82\$103 (T.S.)

82S102-I,N • 82S103-I,N

The state of I<sub>0</sub> contained in each gate is determined in accordance with the given truth table. Note that 2 tests are required to uniquely determine the state of the input variable contained in each gate.

- B.Disable verified input by returning  $I_0$  to  $V_{IX}$ .

- C Repeat steps A and B for all other input variables.

- D.Remove VIX from all input variables.

# TRUTH TABLE FOR INPUT VERIFICATION

| 10 | Fp  | Fρ     | INPUT VARIABLE STATE     | LINK FUSED |

|----|-----|--------|--------------------------|------------|

| 0  | 1 0 | 0      | Īo                       | J          |

| 0  | 0   | 1 0    | lo                       | k          |

| 0  | 1 1 | 0<br>0 | Don't care               | Both       |

| 0  | 0   | 1 1    | (1 <sub>0</sub> ), (1  0 | Neither    |

# PROGRAMMING SYSTEMS SPECIFICATIONS1 TA = 25°C

|                                  | DADAMETED                          | TEST COMPLETIONS                                              | 1    | LIMITS |      |       |  |  |

|----------------------------------|------------------------------------|---------------------------------------------------------------|------|--------|------|-------|--|--|

|                                  | PARAMETER                          | TEST CONDITIONS                                               | Min  | Тур    | Max  | UNIT  |  |  |

| VCCP                             | Vcc supply<br>Program <sup>2</sup> | I <sub>CCP</sub> = 350 ± 50mA,<br>Transient or steady state   | 8.5  | 8.75   | 9.0  | V     |  |  |

| Vccv                             | Verify                             |                                                               | 4.75 | 5.0    | 5.25 |       |  |  |

| ICCP                             | (cc (imit (program)                | V <sub>CCP</sub> = +8.75 ± .25V,<br>Transient or steady state | 400  | 450    | 500  | mA    |  |  |

| VOPF                             | Forced output voltage3 (program)   | IOP = 150 ± 25mA, Transient or steady state                   | 16.0 | 17.0   | 18.0 | \ \   |  |  |

| IOPF                             | Output current limit (program)     | $V_{OP} = +17 \pm 1V$ ,<br>Transient or steady state          | 125  | 150    | 175  | mA    |  |  |

|                                  | Input voltage                      |                                                               |      |        |      | V     |  |  |

| VIH                              | High                               |                                                               | 2.4  |        | 5.5  | }     |  |  |

| VIL                              | Low                                |                                                               | 0    | 0.4    | 8.0  |       |  |  |

|                                  | Input current                      |                                                               |      | ĺ      |      | μA    |  |  |

| lін                              | High                               | $V_{IH} = +5.5V$                                              |      |        | 50   |       |  |  |

| h <u>L</u>                       | Low                                | $V_{IL} = 0V$                                                 |      |        | -500 |       |  |  |

| Vix                              | CE program enable level            |                                                               | 9.5  | 10     | 10.5 | V     |  |  |

| lix1                             | Input variables current            | $V_{IX} = +10V$                                               |      |        | 5.0  | mA    |  |  |

| lıx2                             | CE input current                   | V <sub>IX</sub> = +10V                                        |      |        | 10.0 | mA    |  |  |

| TR                               | Output pulse rise time             |                                                               | 10   | 1      | 50   | μS    |  |  |

| tp                               | CE programming pulse width         |                                                               | 0.3  | 0.4    | 0.5  | ms    |  |  |

| $t_D$                            | Pulse sequence delay               |                                                               | 10   |        |      | μs    |  |  |

| TPR                              | Programming time                   |                                                               | l l  | 0.6    | }    | ms    |  |  |

| TPR                              | Programming duty cycle             |                                                               |      |        | 100  | %     |  |  |

| T <sub>PR</sub> +T <sub>PS</sub> | Frogramming duty cycle             |                                                               |      | 1      | 100  | 70    |  |  |

| FL                               | Fusing attempts per link           |                                                               |      |        | 2    | cycle |  |  |

| Vs                               | Verify threshold <sup>4</sup>      |                                                               | 1.4  | 1.5    | 1.6  | ľv    |  |  |

### NOTES

These are specifications which a Programming System must satisfy in order to be qualified by Signetics.

<sup>2.</sup> Bypass Vcc to GND with a 0.01μF capacitor to reduce voltage spikes.

Care should be taken to ensure that the voltage is maintained during the entire fusing cycle. The recommended supply is a constant current source clamped at the specified voltage limit.

Vs is the sensing threshold of a gate output voltage for a programmed link. It normally constitutes the

reference voltage applied to a comparator circuit to verify a successful fusing attempt.

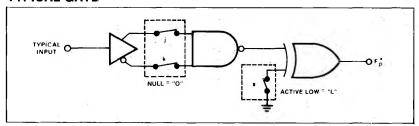

### **PROGRAMMING**

In a virgin device all Ni-Cr links are intact. The initial programmed state of each gate is shown in the Typical Gate illustration.

To program inputs and outputs of each gate for implementing the desired logic function, fuse Ni-Cr links as indicated in the fuse link diagrams.

# **TYPICAL GATE**

# **OUTPUT ACTIVE HIGH = FUSE LINK S**

# INPUT Im = FUSE LINK J

# INPUT Im = FUSE LINK K

# INPUT DON'T CARE = FUSE BOTH LINKS J, K

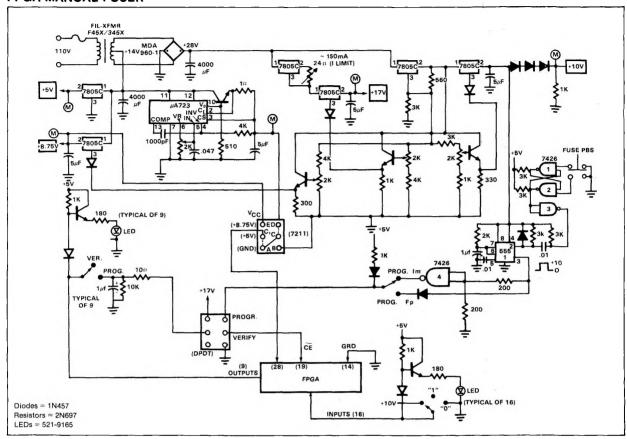

# **FPGA MANUAL FUSER**

# BIPOLAR FIELD PROGRAMMABLE GATE ARRAY (16X9) 82S102 (0.C.)/82S103 (T.S.)

82S102-I,N • 82S103-I,N

# **16X9 FPGA PROGRAM TABLE**

| CUSTOMER NAME         | THIS PORTION TO BE COMPLETED BY SIGNETICS |

|-----------------------|-------------------------------------------|

| PURCHASE ORDER #      | CF (XXXX)                                 |

| SIGNETICS DEVICE #    | CUSTOMER SYMBOLIZED PART #                |

| TOTAL NUMBER OF PARTS | DATE RECEIVED                             |

| PROGRAM TABLE #       | COMMENTS                                  |

|                       |                                           |

|                       |                                           |

| )=                    |                                           |

|                       |                                           |

| =                     |                                           |

| =                     |                                           |

| 2 =                   |                                           |

| 2 =                   |                                           |

| 1 =                   |                                           |

| OUTF           | PUT  |                                                        |                |     |                |     | _              | INI | PUT VA         | RIABL          | E              |     |     |     |     |     |    |

|----------------|------|--------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|----------------|----------------|----------------|-----|-----|-----|-----|-----|----|

| POLA           | RITY | I <sub>0</sub>                                         | l <sub>1</sub> | 12  | l <sub>3</sub> | 14  | l <sub>5</sub> | 16  | l <sub>7</sub> | l <sub>a</sub> | l <sub>9</sub> | IA  | lB  | lc  | ΙD  | lE  | lF |

| F <sub>o</sub> | 0    | 0                                                      | 1              | 2   | 3              | 4   | 5              | 6   | 7              | 8              | 9              | 10  | 11  | 12  | 13  | 14  |    |

| F <sub>1</sub> | 16   | 16                                                     | 17             | 18  | 19             | 50  | 21             | 22  | 23             | 24             | 25             | 26  | 27  | 28  | 29  | 30  |    |

| F <sub>2</sub> | 32   | 35                                                     | 33             | 34  | 35             | 36  | 37             | 38  | 39             | 40             | 41             | 42  | 43  | 44  | 45  | 46  | 4  |

| F <sub>3</sub> | 48   | 48                                                     | 49             | 50  | 51             | 52  | 53             | 54  | 55             | 56             | 57             | 58  | 59  | 60  | 61  | 62  | ŕ  |

| F <sub>4</sub> | 64   | 64                                                     | 65             | 66  | 67             | 68  | 69             | 70  | 71             | 72             | 73             | 74  | 75  | 76  | 77  | 78  |    |

| F <sub>5</sub> | 80   | 80                                                     | 81             | 82  | 83             | 84  | 85             | 86  | 87             | 88             | 89             | 90  | 91  | 92  | 93  | 94  |    |

| F <sub>6</sub> | 96   | 96                                                     | 97             | 98  | 99             | 100 | 101            | 102 | 103            | 104            | 105            | 106 | 107 | 108 | 109 | 110 | 1  |

| F <sub>7</sub> | 112  | 112                                                    | 113            | 114 | 115            | 116 | 117            | 118 | 119            | 120            | 121            | 122 | 123 | 124 | 125 | 126 | 1  |

| F <sub>8</sub> | 128  | 128                                                    | 129            | 130 | 131            | 132 | 133            | 134 | 135            | 136            | 137            | 138 | 139 | 140 | 141 | 142 | 1- |

| Active-hi      |      | I <sub>m</sub> = H<br>I <sub>m</sub> = L<br>Don't Care | = -            |     |                |     |                |     |                |                |                |     |     |     |     |     |    |

The number in each cell in the table denotes its address for programmers with a decimal address display.