# DIGITAL 8000 SERIES TTL/MEMORY

### DESCRIPTION

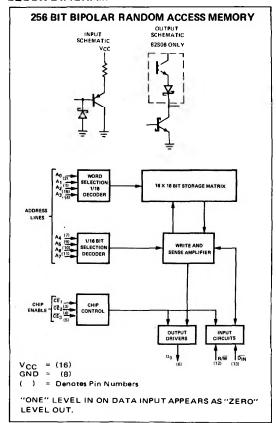

The 82S06 and 82S07 are ideal devices for use in Control Stores, small buffers, scratch pads, "cache" type buffer stores, memory maps, etc. The typical read time (the time between applying an address and obtaining valid output data) is 45ns. The typical write time (the time between applying one address and storing data) is 20ns. The circuit has 3 chip enable inputs which greatly simplifies the circuit configuration when used in large memories. The 82S06 and 82S07 also feature very low input loadings, 25 microamperes for a "1" state and -100 microamperes for "0".

The memories are TTL compatible and operate from single 5 volt supply.

### APPLICATIONS

**BUFFER MEMORY** WRITABLE CONTROL STORE **MEMORY MAPPING** PUSH DOWN STACK

#### EATURES

- 256 X 1 ORGANIZATION

- 30 NANOSECOND ACCESS TIME TYPICAL

- LOW 1.5 mw/BIT POWER DISSIPATION TYPICAL

- LOW 100 HA INPUT LOADING

- TRI-STATE (82S06) OR OPEN COLLECTOR (82S07) OUTPUT

- ON CHIP DECODING

### **BLOCK DIAGRAM**

## OBJECTIVE ELECTRICAL CHARACTERISTICS (TA = 0 to 75°C, VCC = 5.0V ±5) Note 1, 2, 3

| CHARACTERISTICS                |      | LIN     | MITS    |       |                                                                                                          | NOTES |

|--------------------------------|------|---------|---------|-------|----------------------------------------------------------------------------------------------------------|-------|

|                                | MIN. | TYP.    | MAX.    | UNITS | TEST CONDITIONS                                                                                          |       |

| "0" Input Current              |      | -10     | -100    | μА    | V <sub>in</sub> = 0.5V                                                                                   |       |

| "1" Input Current              |      | <1.0    | 25      | μА    | V <sub>in</sub> = 5.25V                                                                                  |       |

| "0" Output Voltage             |      | .35     | .5      | V     | I <sub>out</sub> = 16mA                                                                                  |       |

| Output Leakage Current (82S07) |      | <1.0    | 100     | μА    | CE <sub>1</sub> , CE <sub>2</sub> , CE <sub>3</sub> = "1", V <sub>out</sub> = 2.7V                       |       |

| Output "off" Current (82S06)   |      | <1.0    | ±100    | μΑ    | $\overline{CE}_1$ , $\overline{CE}_2$ , $\overline{CE}_3$ = "1", 0.5 $\leq$ V <sub>out</sub> $\leq$ 2.7V |       |

| "1" Output Voltage (82S06)     | 2.6  |         |         | V     | $\overline{CE}_1 = \overline{CE}_2 = \overline{CE}_3 = "0"  _{out} = -3.2 \text{mA}$                     |       |

| "O" Input Threshold            | 1    |         | .85     | V     |                                                                                                          |       |

| "1" Input Threshold            | 2.0  |         |         | V     |                                                                                                          | Į     |

| Power Consumption              | Ì    | 110/550 | 130/683 | mA/mW |                                                                                                          |       |

| Input Clamp Voltage            | -1.5 | 8       |         | V     | I <sub>in</sub> = - 12mA                                                                                 |       |

| Input Capacitance              | ļ    | 5       |         | ρF    |                                                                                                          |       |

| Output Capacitance             |      | 8       |         | pF    |                                                                                                          |       |

# OBJECTIVE ELECTRICAL CHARACTERISTICS (TA = 25°C, VCC = 5.0V)

| CHARACTERISTICS                      |                 | L          | LII  | VIITS |       | TEST CONDITIONS       | NOTES |

|--------------------------------------|-----------------|------------|------|-------|-------|-----------------------|-------|

|                                      |                 | MIN.       | TYP. | MAX.  | UNITS |                       | NOTES |

| Access Time-Address to Output        |                 |            | 45   | 65    | ns    |                       | 4,5   |

| Address Set-Up Time (read)           | t <sub>1</sub>  | ł          | 10   |       | ns    | 1                     | 1     |

| Propagation Delay                    | •               | 1          | }    |       |       |                       | 4,5   |

| Chip Enable to Output Enable         | t <sub>2</sub>  |            | 25   | 40    | ns    |                       |       |

| Propagation Delay                    | _               | ļ          |      |       |       | İ                     | • 4,5 |

| Chip Enable to Output Disable        | t <sub>3</sub>  | 1          | 25   | 40    | ns    |                       |       |

| Address to Write Enable              | •               | ĺ          |      |       |       |                       | 4,5   |

| Set-Up Time                          | t <sub>4</sub>  | 25         | 5    |       | ns    |                       |       |

| Chip Enable to Write Enable          | ·               | İ          |      |       |       |                       | 4,5   |

| Set-Up Time                          | t <sub>5</sub>  | 10         | . 0  |       | ns    |                       |       |

| Data Input to Write Enable           | _               | 1          | 1    |       |       |                       | 4,5   |

| Set-Up Time                          | t <sub>6</sub>  | 10         | 0    |       | ns    |                       |       |

| Write Enable Pulse Width             | t <sub>7</sub>  | 30         | 15   |       | ns    | ì                     | 4,5   |

| Address Hold Time                    | t <sub>8</sub>  | 10         | 0    |       | ns    |                       | 4,5   |

| Chip Enable Hold Time                | t <sub>9</sub>  | 10         | 0    |       | ns    |                       | 4,5   |

| Data Input Hold Time                 | <sup>t</sup> 10 | 10         | 0    |       | ns    | 1                     | 4,5   |

| Write Enable Propagation Delay       | <sup>‡</sup> 11 |            | 30   | 40    | ns    |                       | 4,5   |

| Output Short Circuit Current (82S06) | ••              | <b>−20</b> |      | -100  | mA    | V <sub>out</sub> = 0V | 4,5   |

#### NOTES:

- 1. Positive current is defined as into the terminal referenced.

- 2. Manufacturer reserves the right to make design and process changes and improvements.

- 3. Applied voltages must not exceed 6.0V,

Input currents must not exceed ±30mA, Output currents must not exceed ±100mA, Storage temperature must be between -60°C to +150°C.

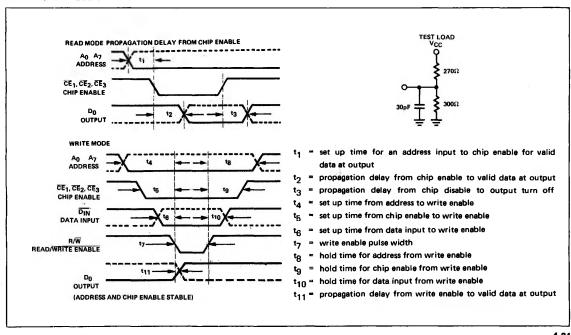

- 4. Refer to Timing Diagram for definition of terms and test load.

- 5. Rise and fall times for this test must be less than 5ns. Input amplitudes are 2.8V and all measurements are made at 1.5 volts.

## TIMING DIAGRAM