# DIVIDE-BY-TWELVE | 8288 COUNTER/STORAGE ELEMENT

A.F.W PACKAGES

# DIGITAL 8000 SERIES TTL/MSI

#### DESCRIPTION

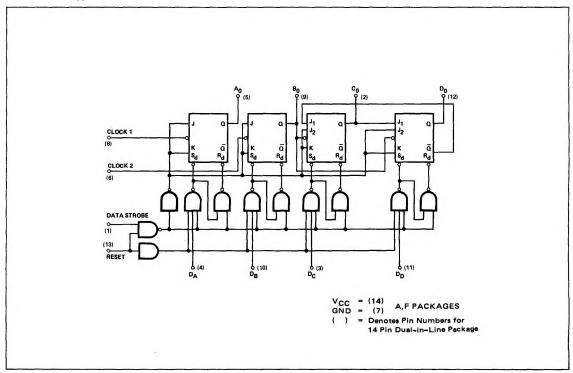

The 8288 Divide by Twelve Counter is a four-bit subsystem consisting of divide by two and divide by six counters in a 14 pin package. For Divide-by-Twelve operation, output A is connected externally to the clock 2 input.

The 8288 has strobed paralleled data entry capability so that the counter may be preset to any desired output state. A "1" or "0" at a data input will be transferred to the associated output when the strobe input is put at a "0" level. For additional flexibility, the 8288 is provided with a common reset. A "0" on the reset line produces "0" at all four outputs.

The counting operation is performed on the falling (negative going) edge of the input clock pulse, however, there is no restriction on transition time since the individual binaries are level sensitive. The data strobe and reset functions are asynchronous with respect to the clock.

#### **TRUTH TABLE\***

| , |        |   |    |     |   |  |  |  |  |

|---|--------|---|----|-----|---|--|--|--|--|

| 1 | OUTPUT |   |    |     |   |  |  |  |  |

|   | Count  | D | С  | В   | Α |  |  |  |  |

|   | 0      | 0 | 0  | 0   | 0 |  |  |  |  |

|   | 1      | 0 | 0  | 0   | 1 |  |  |  |  |

| - | 2<br>3 | 0 | 0  | 1   | 0 |  |  |  |  |

| 1 | 3      | 0 | 0  | 1   | 1 |  |  |  |  |

|   | 4      | 0 | 1  | 0   | 0 |  |  |  |  |

| - | 5      | 0 | 1  | 0   | 1 |  |  |  |  |

|   | 6      | 0 | 1  | 1   | 0 |  |  |  |  |

| ŀ | 7      | 0 | 1  | 1   | 1 |  |  |  |  |

|   | 8      | 1 | 0  | 0   | 0 |  |  |  |  |

| 1 | 9      | 1 | 0  | 0   | 1 |  |  |  |  |

| Į | 10     | 1 | 0  | 1   | 0 |  |  |  |  |

|   | 11     | 1 | 10 | 1 1 | 1 |  |  |  |  |

\*Connected for Divide-by-Tweive operation (output A connected to CP2)

#### LOGIC DIAGRAM

**ELECTRICAL CHARACTERISTICS** (Over Recommended Operating Temperature and Voltage)

| CHARACTERISTICS              | LIMITS |         |        |       | TEST CONDITIONS |                |       |            |            |         | NOTES  |

|------------------------------|--------|---------|--------|-------|-----------------|----------------|-------|------------|------------|---------|--------|

| OHARAO I ERISTIOS            | MIN.   | I. TYP. | MAX.   | UNITS | DATA<br>STROBE  | DATA<br>INPUTS | RESET | CLOCK<br>1 | CLOCK<br>2 | OUTPUTS | NOTES  |

| "1" Output Voltage           | 2.6    | 3.5     |        | V     | 0.8∨            | 2.0V           | 2.0V  |            | Output A   | -800µA  | 6, 7   |

| "0" Output Voltage           |        |         | 0.4V   | l v   | 0.8∨            | 0.8∨           | 0.8∨  | )          | Output A   | 16mA    | 6,8    |

| "0" Input Current            |        | 1       |        |       | }               |                |       |            |            |         | ·      |

| Data Strobe                  | -0.1   |         | -1.6   | mA    | 0.4V            |                | 5.25V | 1          |            | [       | ĺ      |

| Data Inputs                  | -0.1   |         | -1.2   | mA    | [               | 0.4V           |       | 1          | 1          |         |        |

| Reset                        | -0.1   |         | -3.2   | mA    | 5.25V           |                | 0.4V  | ł          | }          | ł       |        |

| Clock 1                      | -0.1   |         | -3.2   | mA    | ł               |                |       | 0.4V       | }          |         |        |

| Clock 2                      | -0.1   |         | -1.6   | mA    | }               |                | ,     | 1          | 0.4V       | ļ       |        |

| "1" Input Current            |        |         |        | ]     |                 |                |       |            | 1          |         | 1      |

| Data Strobe                  |        |         | 40     | μА    | 4.5V            |                | ov    | 1          | 1          |         |        |

| Data Input                   |        |         | 40     | μА    | [               | 4.5V           | ľ     | (          | <b>{</b>   |         | ł      |

| Reset                        |        |         | 80     | μА    | ĺ               |                | 4.5V  |            |            |         | }      |

| Clock 1                      |        |         | 80     | μА    | 1               |                | 1     | 4.5V       | ļ          |         | 1      |

| Clock 2                      |        |         | 80     | μА    | )               |                |       |            | 4.5V       |         |        |

| Power/Current Consumption    |        | 184/35  | 236/45 | mW/mA |                 |                | ov    | ov         | ov         |         | 11     |

| Input Voltage Rating         |        |         |        |       | Q.              |                |       | [          | 1          |         | Ì      |

| Data Strobe                  | 5.5    |         | * 1    | l v   | 10mA            |                | l     | 1          |            | )       | ì      |

| Data Inputs                  | 5.5    |         | 1      | V     | Ì               | 10mA           | l     | 1          |            |         | }      |

| Reset                        | 5.5    | 1       | }      | V     | }               |                | 10mA  | }          | }          |         |        |

| Output Short Circuit Current | -10    |         | -60    | mA    | ov              |                |       |            |            | 0V      | 10, 11 |

$T_A = 25^{\circ}C$  and  $V_{CC} = 5.0V$

| CHARACTERISTICS        |      | LIMITS       |      |       | TEST CONDITIONS |                |       |            |            |         |       |

|------------------------|------|--------------|------|-------|-----------------|----------------|-------|------------|------------|---------|-------|

| CHARACTERISTICS        | MIN. | MIN. TYP. MA | MAX. | UNITS | DATA<br>STROBE  | DATA<br>INPUTS | RESET | CLOCK<br>1 | CLOCK<br>2 | OUTPUTS | NOTES |

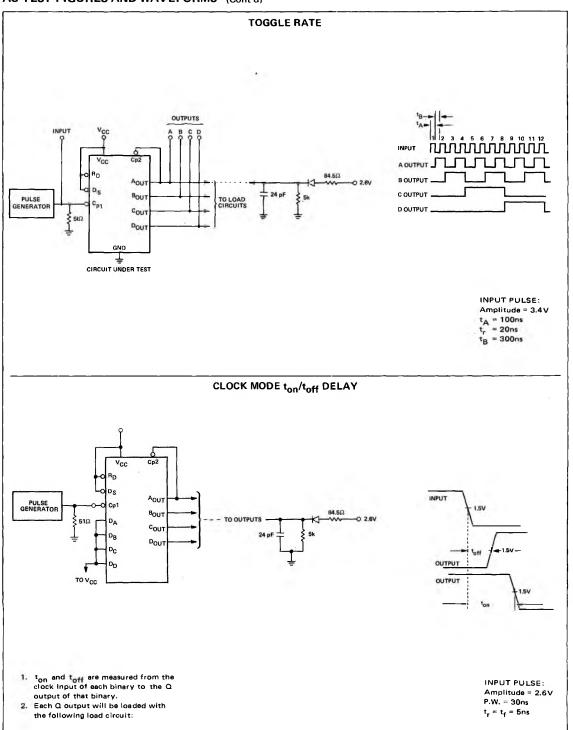

| Clock Mode ton Delay   |      |              |      |       | 1               |                |       |            |            |         |       |

| Bit A, B, C, D         | 1    | 15           | 25   | ns    |                 |                | 1     |            |            |         | 9     |

| Clock Mode toff Delay  |      | ]            | j    | }     |                 |                | l     |            |            |         | (     |

| Bit A, B, C, D         |      | 15           | 25   | ns    |                 |                |       |            | [          | 1       | 9     |

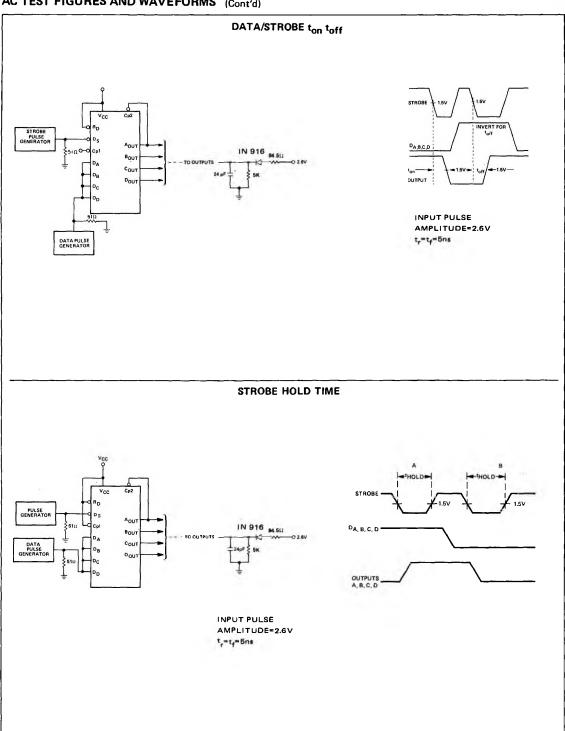

| Data/Strobe ton Delay  | i    | 1            | 1    | ĺ     |                 |                | i     | ĺ          | 1          |         |       |

| Bit A, B, C, D         | ì    | 20           | 35   | ns    |                 |                | 1     |            |            |         | 9     |

| Data/Strobe toff Delay | ł    | ł            | 1    | 1     | }               |                | 1     | }          |            |         | }     |

| Bit A, B, C, D         | ļ    | 25           | 40   | ns    |                 |                | 1     | ļ          |            |         | 9     |

| Toggle Rate            | 20   | 25           | ļ    | MHz   | 1               |                |       | 1          |            | 1       | 9     |

| Strobe Hold Time       | -    | 25           | 35   | ns    |                 | 0.8V           | 2.0V  | 2.0∨       | Output A   |         | 1     |

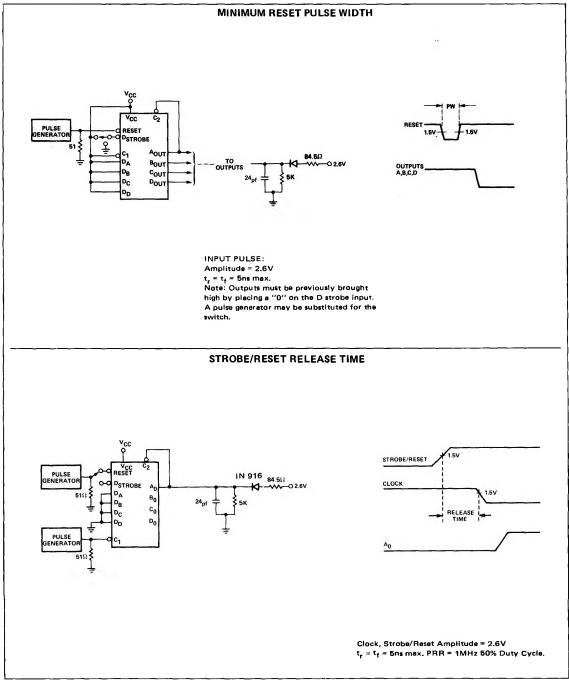

| Reset Hold Time        | 1    | 20           | 35   | ns    | 2.0V            | 0.8∨           |       | 2.0V       | Output A   |         |       |

| Strobe Release Time    | {    | 30           | 40   |       |                 |                |       |            |            |         | 1     |

| Reset Release Time     | 1    | 50           | 75   | ns    | 1               |                |       |            |            |         | ĺ     |

#### NOTES:

- All voltage measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- All measurements are taken with ground pin tied to zero 2. volts.

- 3. Positive current flow is defined as into the terminal referenced.

- Positive NAND Logic definition:

"UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current

- limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased.

- Measurements apply to each output and the associated data 6. input independently.

- Output source current is supplied through a resistor to ground. 7.

- Output sink current is supplied through a resistor to V<sub>CC</sub>. Refer to AC Test Figures, 8.

- 9.

- 10. Not more than one output should be shorted at a time.

- $V_{CC} = 5.25$  volts. 11.

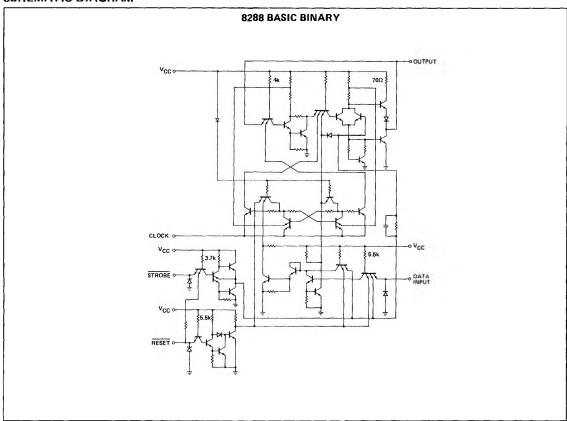

#### SCHEMATIC DIAGRAM

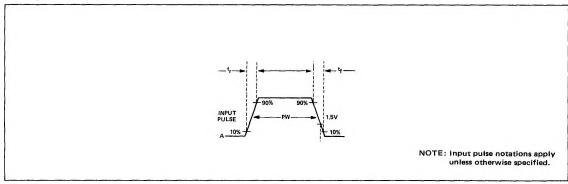

### **AC TEST FIGURES AND WAVEFORMS**

### AC TEST FIGURES AND WAVEFORMS (Cont'd)

# AC TEST FIGURES AND WAVEFORMS (Cont'd)

## AC TEST FIGURES AND WAVEFORMS (Cont'd)

#### NOTES:

- 1. All resistor values are in ohms.

- 2. All capacitance values are in picofarads and include jig and probe capacitance.