PRODUCT AVAILABLE IN 0°C TO +75°C TEMP RANGE ONLY.

B,F PACKAGES

# DIGITAL 8000 SERIES TTL/MSI

#### DESCRIPTION

The 8277 is a dual 8-Bit Shift Register which provides the designer with sixteen (16) bits of serial storage operating at a typical shift rate of 20MHz. Features of the 8277 are:

- TRUE and COMPLEMENT outputs are provided on each register's eighth bit.

- 2. Positive edge triggering on clock input.

- SEPARATE CLOCK lines (pins 7 and 10) for each 8-bit register are provided as well as a COMMON CLOCK line (pin 9) for all sixteen storage bits.

- 4. Common RESET (pin 1).

- AND-OR gating to the input of each 8-bit register is provided to accomplish the multiplex function.

- 6. Direct replacement for 9328.

#### **TRUTH TABLE**

| DS | D <sub>0</sub> | D <sub>1</sub> | Reset | Function         |  |  |  |

|----|----------------|----------------|-------|------------------|--|--|--|

| 0  | 0              | ×              | 1     | Shift in "0"     |  |  |  |

| o  | 1              | ×              | 1     | Shift in "1"     |  |  |  |

| 1  | ×              | 0              | 1     | Shift in "O"     |  |  |  |

| 1  | ×              | 1              | 1     | Shift in "1"     |  |  |  |

| ×  | ×              | ×              | 0     | Reset "Q" to "0" |  |  |  |

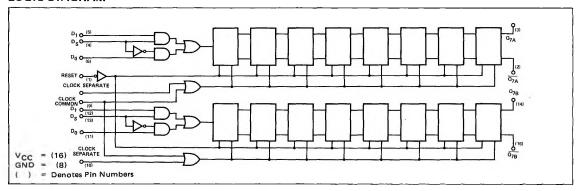

#### **LOGIC DIAGRAM**

#### ELECTRICAL CHARACTERISTICS (Over Recommended Operating Temperature And Voltage)

|                               | LIMITS       |      |              |          | TEST CONDITIONS                         |                |       |            |       |         | 10750 |

|-------------------------------|--------------|------|--------------|----------|-----------------------------------------|----------------|-------|------------|-------|---------|-------|

| CHARACTERISTICS               | MIN.         | TYP. | MAX.         | UNITS    | DATA<br>D <sub>1</sub> , D <sub>0</sub> | DATA<br>SELECT | CLK   | CLK<br>SEP | RESET | OUTPUTS | NOTES |

| "1" Output Voltage (Q)        | 2.6          | 3.5  |              |          | 2.0V                                    | 2.0V           | Pulse | 0.8V       | 2.0V  | -800µA  | 6     |

| "1" Output Voltage (Q)        | 2.6          | 3.5  |              | v        | V8,0                                    | 2.0V           | 0.8∨  | Pulse      |       | -800µA  | 6     |

| "0" Output Voltage (Q)        |              |      | 0.4          | ) v      | 0.8∨                                    | 0.8V           | Pulse | 0.80       |       | 16mA    | 7     |

| "0" Output Voltage (Q)        |              |      | 0.4          | v        | 2.0V                                    | 0.8V           | Puise | 0.8V       |       | 16mA    | 7     |

| "0" Input Current             |              |      |              |          |                                         |                |       |            | l     |         |       |

| Data, Reset                   | -0.1         |      | 1.6          | mA       | 0.4∨                                    |                | ŀ     |            | 0.4V  |         |       |

| Data Select<br>Clock Separate | -0.1<br>-0.1 |      | -3,2<br>-1.6 | mA       | ı                                       | 0.4V           | }     | 0.4∨       |       |         |       |

| Clock Common                  | -0.1         |      | 3.2          | mA       |                                         |                | 0.4V  | -          |       |         |       |

| "1" Input Current             |              |      |              |          | Ï                                       |                | ĺ     |            |       |         |       |

| Data, Reset, Clock Separate   |              |      | 40           | μА       | 4.5V                                    |                |       | 4.5V       | 4.5V  |         |       |

| Data Select                   |              |      | 80<br>80     | μA<br>μA |                                         | 4.5V           | 4.5V  |            |       |         |       |

| Clock Common                  |              |      |              | ] '      |                                         |                | 4.5V  |            |       |         | 8     |

| Power/Current Consumption     |              |      | 540/<br>103  | mW/mA    |                                         |                |       |            | 1     |         |       |

| Input Voltage Rating          |              |      |              |          |                                         |                |       |            |       |         |       |

| All Inputs                    | 5.5          |      |              | V        | 10mA                                    | 10mA           | 10mA  | 10mA       | 10 mA |         |       |

## $T_A = 25^{\circ} C$ and $V_{CC} = 5.0 V$

|                   | LIMITS |      |      |       | TEST CONDITIONS                         |                |               |            |       |         |      |

|-------------------|--------|------|------|-------|-----------------------------------------|----------------|---------------|------------|-------|---------|------|

| CHARACTERISTICS   | MIN.   | TYP. | MAX. | UNITS | DATA<br>D <sub>1</sub> , D <sub>0</sub> | DATA<br>SELECT | CLK<br>COMMON | CLK<br>SEP | RESET | OUTPUTS | NOTE |

| Turn-on Delay     |        |      |      |       |                                         |                |               |            |       |         |      |

| Clock To Output   |        | 25   | 40   | ns    |                                         |                |               |            |       |         | 10   |

| Reset To Output   |        | 25   | 40   | ns    | 1                                       |                |               |            |       |         | 10   |

| Turn-off Delay    |        |      |      |       | 1                                       |                |               |            | 1     |         | ' -  |

| Clock To Output   | ì      | 25   | 40   | ns    |                                         |                |               |            |       |         | 10   |

| Reset To Output   |        | 25   | 40   | ns    |                                         |                |               |            | l     |         | 10   |

| Clock Pulse Width | 15     | _    |      | ns    |                                         |                |               |            |       |         | 10   |

| Shift Rate        | 15     | 20   |      | MHz   |                                         |                |               |            |       | '       | 10   |

| Data Set-up Time  |        | 20   | 30   | ns    |                                         |                | 1             |            |       |         | 10   |

| Data Hold Time    |        |      | 5    | ns    |                                         |                |               |            | l     | l       | 10   |

#### NOTES:

- All voltage measurments are referenced to the ground terminal.

Terminals not specifically referenced are left electrically open.

- 2. All measurements are taken with ground pin tied to zero volts.

- 3. Positive current flow is defined as into the terminal referenced.

- 4. Positive Logic Definitions:

"UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the

isolation diodes become forward biased.

- 6. Output source current is supplied through a resistor to ground.

- 7. Output sink current is supplied through a resistor to VCC-

- 8. V<sub>CC</sub> = 5,25V

- Clock input is driven by a 1kHz square wave for at least 8 cycles prior to measurement.

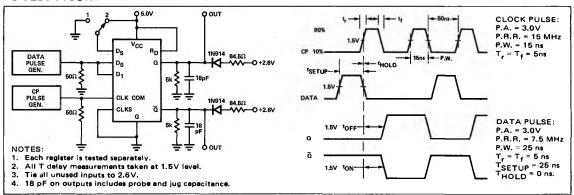

- 10. Refer to AC Test Figure.

### **AC TEST FIGURE AND WAVEFORMS**

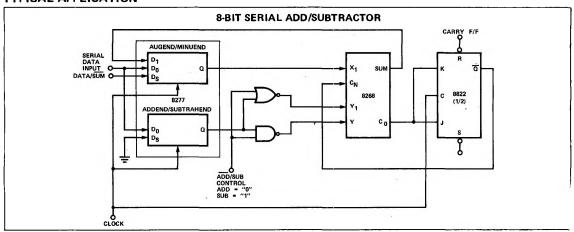

#### TYPICAL APPLICATION